Conceptos básicos analógicos - Parte 3: ADC pipeline y cómo usarlos

Colaboración de Editores de DigiKey de América del Norte

2020-07-14

Nota del editor: Los convertidores analógico-digital (ADC) conectan lo analógico con el mundo digital y por lo tanto son un componente fundamental de cualquier sistema electrónico que se conecta al mundo real. También son un factor determinante del rendimiento de un sistema. Esta serie explora los fundamentos de los CAD, sus diversos tipos y su aplicación. Parte 1 trata de los ADC SAR; Parte 2 trata de los convertidores delta-sigma (ΔƩ); y aquí, la Parte 3 trata de los rasgos, características y uso de ADC pipeline. La cuartaparte muestra cómo las SAE delta-sigma pueden generar resultados de ruido ultra-bajo. En la quintaparte se examinan las cuestiones difíciles de la conducción de insumos para los países en desarrollo sin litoral.

Algunas de las aplicaciones a las que prestan servicio los ADC son las estaciones base de infraestructura celular multiportadora de ultra alta velocidad, las telecomunicaciones, las observaciones de predistorsión digital y los receptores de retroceso, todo ello con el fin de requerir a los ADC que tomen muestras en la región de la gigamuestra por segundo. En la primera y segunda parte de esta serie de fundamentos analógicos se examinan los sucesivos registros de aproximación (SAR) y los ADC delta-sigma (ΔƩ), respectivamente, y la forma de aplicarlos en las aplicaciones apropiadas. Sin embargo, ninguna de las dos tecnologías está preparada para el reto de producir resultados de gigasamuestras por segundo (GSPS).

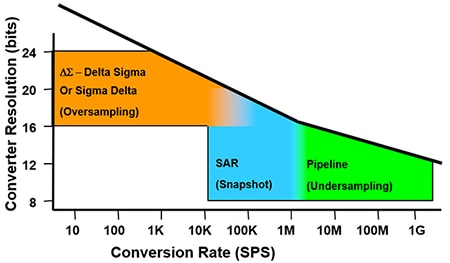

Por ejemplo, la CAD del SAR utiliza un algoritmo de "instantánea", por lo que su velocidad se limita a 10 megamuestras por segundo (MSPS) debido a su enfoque en serie. En el caso del algoritmo de sobremuestreo del ADC ΔƩ de alta resolución, esto requiere un tiempo adicional para adquirir y promediar múltiples muestras que crean velocidades de datos de salida de 24 bits de hasta 5 megahercios (MHz). Las tasas de GSPS están profundamente fuera de la gama de frecuencias de muestreo del ADC SAR y ADC ΔƩ.

La solución a este desafío de la ADC de ultra alta velocidad es una ADC en línea que procesa múltiples muestras mientras sigue enviando datos a su salida a velocidades de GSPS.

En este artículo se comparan brevemente SAR ΔƩ y ADC pipeline y luego se examinan las cuestiones relacionadas con el logro de los resultados de los convertidores de alta velocidad y por qué los ADC pipeline son una excelente alternativa para estas aplicaciones de alta velocidad. A continuación, se presentan dos ADC de Texas Instruments: uno destacando la precisión, el otro la alta velocidad; y muestra cómo empezar con ellos.

¿Qué es un ADC pipeline?

Un ADC pipeline consiste en varias etapas consecutivas. La primera etapa de estructura diferencial evalúa el valor del bit más significativo (MSB) y luego condiciona la señal y la pasa a la siguiente etapa para una conversión MSB-1. Cada etapa ejecuta su operación simultáneamente con otras etapas (Figura 1).

Figura 1: La topología del proyecto tiene múltiples etapas para implementar la conversión de un bit del convertidor multi-bit y luego condiciona la señal y pasa la señal a la siguiente etapa. (Fuente de la imagen: Texas Instruments)

Figura 1: La topología del proyecto tiene múltiples etapas para implementar la conversión de un bit del convertidor multi-bit y luego condiciona la señal y pasa la señal a la siguiente etapa. (Fuente de la imagen: Texas Instruments)

En la figura 1, las etapas son similares en función y solo resuelven uno o dos bits. Cada etapa tiene una muestra y una retención, un ADC de flash de baja resolución y una función de acondicionamiento de la señal. La primera etapa recibe la muestra e inmediatamente produce una decisión MSB. El valor digital MSB va al primer pestillo (pestillo 1). Si la decisión del MSB es una, la etapa resta el valor de carga del MSB de la muestra. Entonces el convertidor del proyecto aplica un múltiplo de ganancia 2x a la carga restante. Cuando una etapa completa sus operaciones, pasa la diferencia analógica a las etapas siguientes. La belleza del diseño con el múltiple de ganancia 2x es que la Etapa 1 hasta la Etapa n son fundamentalmente los mismos circuitos.

El número de etapas a menudo coincide con el número de bits de ADC. La salida de la conversión final combina los resultados digitales de cada etapa en el pestillo de salida. Este proceso de conversión da como resultado una latencia de datos de varios ciclos de reloj.

Comparación de muestras de ADC ΔΣ, SAR y pipeline

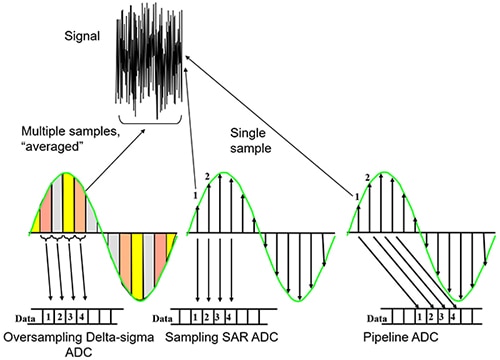

El convertidor ΔΣ utiliza un algoritmo de sobremuestreo para implementar filtros digitales de respuesta de impulso finito (FIR) o de respuesta de impulso infinito (IIR). Estos filtros crean una latencia o retardo de salida de la señal mientras adquieren múltiples muestras, lo que hace que una resolución extremadamente alta sea una compensación positiva. Como resultado, el tiempo de adquisición es más largo que con un convertidor de SAR o pipeline, que solo muestrean la señal una vez por cada conversión (figura 2).

Figura 2: el ADC ΔƩ más lento y de mayor resolución que ofrece señales de frecuencia inferiores. El ADC SAR de velocidad moderada y resolución media facilita las aplicaciones de propósito general. El ADC pipeline de alta velocidad y menor resolución se adapta a las soluciones de alta velocidad de vanguardia. (Fuente de la imagen: DigiKey)

Figura 2: el ADC ΔƩ más lento y de mayor resolución que ofrece señales de frecuencia inferiores. El ADC SAR de velocidad moderada y resolución media facilita las aplicaciones de propósito general. El ADC pipeline de alta velocidad y menor resolución se adapta a las soluciones de alta velocidad de vanguardia. (Fuente de la imagen: DigiKey)

El ADC SAR muestra una instantánea de la señal de entrada con un punto de adquisición definido en el tiempo. Al utilizar técnicas de redistribución de carga, el SAR completa rápidamente una conversión de latencia cero. El convertidor pipeline utiliza tecnologías de submuestreo para lograr conversiones de alta velocidad mediante la utilización de técnicas de redistribución de cargas, así como para retrasar la aparición de los resultados en la salida. Este algoritmo de conversión crea una latencia de datos.

La latencia frente a la velocidad de conversión difiere entre el SAR, el pipeline y el convertidor ΔƩ (Figura 3).

Figura 3: El algoritmo de sobremuestreo y promediación de ΔƩ crea un retraso en la aparición de la palabra final de datos de salida. Como la salida del ADC SAR aparece antes de la siguiente adquisición de la muestra, la latencia del ADC SAR es cero. El retraso en el resultado de los datos del convertidor del oleoducto crea una latencia no nula. (Fuente de la imagen: DigiKey)

Figura 3: El algoritmo de sobremuestreo y promediación de ΔƩ crea un retraso en la aparición de la palabra final de datos de salida. Como la salida del ADC SAR aparece antes de la siguiente adquisición de la muestra, la latencia del ADC SAR es cero. El retraso en el resultado de los datos del convertidor del oleoducto crea una latencia no nula. (Fuente de la imagen: DigiKey)

En la figura 3, el convertidor ΔƩ promedia múltiples muestras para cada resultado de conversión. El filtro de promediación de ΔƩ suele ser un filtro digital FIR o IIR. Este promedio de multimuestreo aumenta el tiempo de conversión total. Sin embargo, es posible que las altas resoluciones creen una dependencia de tiempo y precisión de la producción.

El tiempo de conversión del convertidor SAR abarca el tiempo de adquisición de la señal de entrada y el tiempo de conversión. El tiempo de adquisición permite que la señal de entrada se asiente antes de que se produzca el momento real de adquisición de la señal. El tiempo de paso es una combinación de redistribución de la carga interna y señales de salida de datos consecutivas en serie, empezando por el valor MSB.

Con un ADC pipeline, el usuario inicia una adquisición de muestras con el borde ascendente (o descendente) del reloj de entrada externo. La carga adquirida para esta muestra pasa a una segunda etapa, mientras que el convertidor captura el equivalente de carga de otra señal de entrada, y la segunda etapa determina el valor MSB. En el siguiente reloj externo, la segunda señal adquirida va a la segunda etapa, mientras que la primera señal va a la tercera etapa. Durante este ciclo de reloj, se determina el MSB-1 de la primera señal adquirida y el MSB de la segunda señal adquirida. Este proceso continúa con cada señal adquirida. Cuando una señal de entrada tiene una representación digital completa de salida, la etapa de salida del convertidor presenta una representación paralela de la señal de entrada.

El resultado de esta arquitectura es que los ADC pipelines son populares por sus tasas de muestreo desde unas pocas megamuestras por segundo hasta más de 1 GSPS. Las resoluciones van desde 8 bits con tasas de muestreo más rápidas hasta 16 bits con tasas más bajas. Estas resoluciones y tasas de muestreo cubren una amplia gama de aplicaciones, incluyendo imágenes de dispositivos acoplados a la carga (CCD), imágenes médicas ultrasónicas, receptores digitales, estaciones base, predistorsión digital y video digital. Algunas de estas aplicaciones enfatizan la precisión así como la velocidad.

ADC pipeline precisa

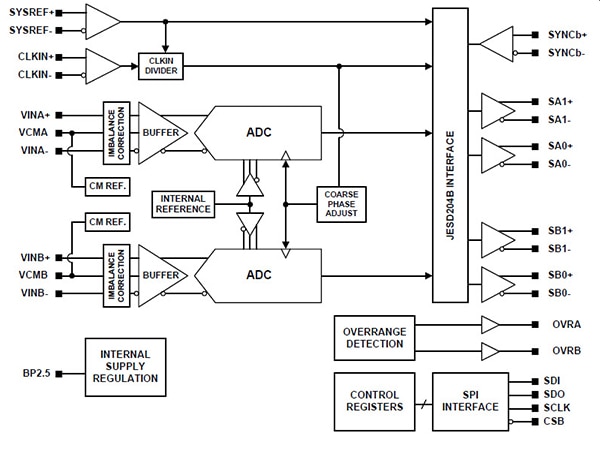

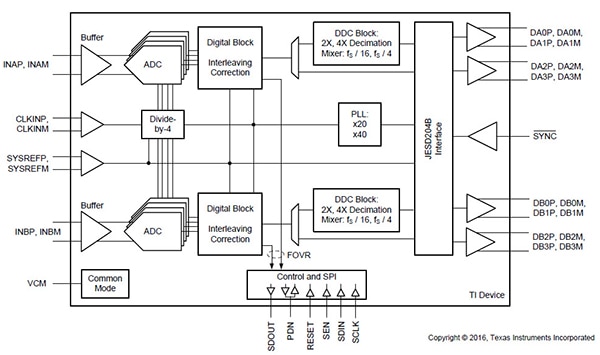

Un buen ejemplo de un ADC pipeline de precisión es el ADC16DX370 de Texas Instruments, un ADC pipeline de doble canal de 16 bits y 370 MSPS, seguida de una interfaz JESD204B de 7.4 gigabits por segundo (Gbit/s). Con una señal de entrada de 150 MHz, la relación señal/ruido (SNR), el rango dinámico libre de espurias (SFDR) y la densidad espectral de ruido (NSD) del ADC16DX370 son de 69.6 decibelios a escala completa (dBFS), 88 dBFS y -152.3 dBFS/Hercios, respectivamente.

Cada ADC tiene un búfer de entrada y un circuito de corrección de desequilibrio, así como los voltajes de referencia necesarios con conductores internos. El búfer de entrada integrado elimina la carga del condensador de muestreo interno y el ruido de retroceso de la carga. Este búfer alivia los requisitos del amplificador de conducción, el filtro antialiasing y la adaptación de la impedancia (Figura 4).

Figura 4: El ADC16DX370 de alto rendimiento y de 370 MSPS de Texas Instruments Convierte las señales analógicas en palabras digitales de 16 bits. (Fuente de la imagen: Texas Instruments)

Figura 4: El ADC16DX370 de alto rendimiento y de 370 MSPS de Texas Instruments Convierte las señales analógicas en palabras digitales de 16 bits. (Fuente de la imagen: Texas Instruments)

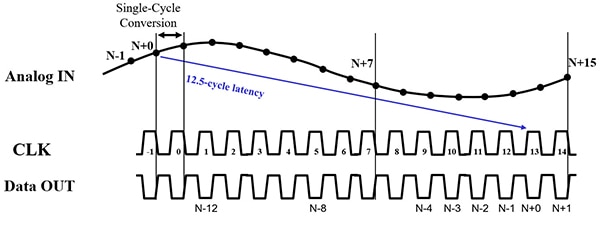

El ADC16DX370 deriva el reloj de muestreo de la entrada CLKIN con un receptor de bajo ruido y un divisor de reloj. Un divisor de reloj de entrada distribuye una señal de reloj de alta frecuencia por todo el sistema, y se divide localmente en el dispositivo ADC para evitar el acoplamiento de señales de frecuencias intermedias comunes (IF) a otras partes del sistema. La latencia del núcleo del ADC es de 12.5 ciclos de reloj (Figura 5).

Figura 5: El diagrama de tiempo muestra que la latencia del núcleo del ADC es de 12.5 ciclos de reloj. (Fuente de la imagen: DigiKey)

Figura 5: El diagrama de tiempo muestra que la latencia del núcleo del ADC es de 12.5 ciclos de reloj. (Fuente de la imagen: DigiKey)

El muestreo se produce en el borde ascendente de la señal diferencial (CLKIN+) - (CLKIN-). Como valor básico mínimo, el código de salida digital está disponible después de 12.5 ciclos de reloj de latencia de datos. Los factores divisores de frecuencia de entrada de CLKIN son 1, 2, 4 u 8.

El ADC16DX370 tiene pines de entrada de reloj diferencial. La terminación interna a CC de cada pin es una resistencia de 50 ohm (Ω) para una terminación diferencial interna total de 100 Ω. Las clavijas de entrada del reloj requieren un acoplamiento de CA externo.

El diseño de la placa de circuito impreso del ADC es fundamental para lograr un rendimiento completo. Se necesitan al menos seis capas para encaminar adecuadamente todas las señales que entran y salen del dispositivo. Las capas de enrutamiento de señales necesitan planos de tierra firme adyacentes para controlar los caminos de retorno de las señales a fin de minimizar las áreas de bucle, y el enrutamiento de microstrips y líneas de estrías debe hacerse con cuidado para controlar las impedancias. El uso de los aviones de potencia y los aviones de tierra firme adyacentes controlan las rutas de retorno de los suministros. Además, al reducirse al mínimo el espacio entre los aviones de suministro y los de tierra, se aumenta el desacoplamiento distribuido y se mejora el rendimiento.

Las aplicaciones objetivo del ADC16DX370 son receptores de muestreo de alta FI, receptores de estación base multiportadora y receptores multimodales y multibanda que complementan la mayor resolución y velocidad de conversión de 370 MSPS. Este ADC de 16 bits ofrece el rendimiento SNR (69.6 dBFS) necesario para discernir las pequeñas señales del ruido de fondo en un subsistema receptor heterodino de RF, por ejemplo.

Para ayudar a los diseñadores a evaluar el ADC16DX370, el ADC es compatible con la placa de evaluaciónADC16DX370EVM con el software High-Speed Data Converter (HSDC) Pro asociado. El EVM viene con un cable mini-USB para conectar a un PC. TI también proporciona la tarjeta de diseño de referencia TSW16DX370EVM que puede utilizarse para evaluar una solución de subsistema de FI del receptor con un ancho de banda utilizable de más de 100 MHz.

ADC pipeline de alta velocidad

Donde la alta velocidad así como el amplio rango dinámico son prioridades, los diseñadores pueden recurrir al ADS54J20 de Texas Instruments, un ADC de doble canal, 12-bit, 1 GSPS. El diseño de este ADC proporciona un alto SNR de 67.8 dBFS con un suelo de ruido de -157 dBFS/Hz. Esta ACD es perfecta para aplicaciones que buscan el mayor rango dinámico en un amplio ancho de banda instantáneo (Figura 6).

Figura 6: El ADC pipeline doble ADS54J20 proporciona una corrección de intercalación para conseguir un suelo de ruido de -157 dBFS/Hz y opciones de filtrado digital para diezmado. (Fuente de la imagen: Texas Instruments)

Figura 6: El ADC pipeline doble ADS54J20 proporciona una corrección de intercalación para conseguir un suelo de ruido de -157 dBFS/Hz y opciones de filtrado digital para diezmado. (Fuente de la imagen: Texas Instruments)

En la Figura 6, los algoritmos de intercalación y titubeo del ADS54J20 se utilizan para lograr un espectro limpio con una alta SFDR. El dispositivo también tiene varias opciones de filtrado para diezmados programables para sistemas que necesitan una mayor SNR y SFDR en un amplio rango de frecuencias.

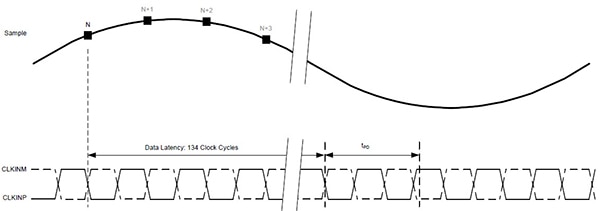

El filtro para diezmado de paso de banda tiene un mezclador digital y tres filtros FIR concatenados para crear una latencia de aproximadamente 134 ciclos de reloj de salida, más una compuerta lógica y un retardo de propagación del búfer de salida que equivale a 4 nanosegundos (ns) (Figura 7).

Figura 7: El diagrama de tiempo en la latencia del ADC es de 134 ciclos de reloj más puertas lógicas y retardo de propagación del búfer de salida (tPD). (Fuente de la imagen: Texas Instruments)

Figura 7: El diagrama de tiempo en la latencia del ADC es de 134 ciclos de reloj más puertas lógicas y retardo de propagación del búfer de salida (tPD). (Fuente de la imagen: Texas Instruments)

El bloque digital, el motor de intercalado y el filtro de diezmado (Figura 6, de nuevo), en combinación con la frecuencia de reloj de 1 gigahercio (GHz) de muestreo de alta velocidad contribuyen a la latencia del convertidor.

Algunas de las aplicaciones del objetivo del ADS54J20 son el radar y los conjuntos de antenas, la banda ancha inalámbrica y los receptores del sistema de terminación de cable módem (CMTS) y DOCSIS 3.1.

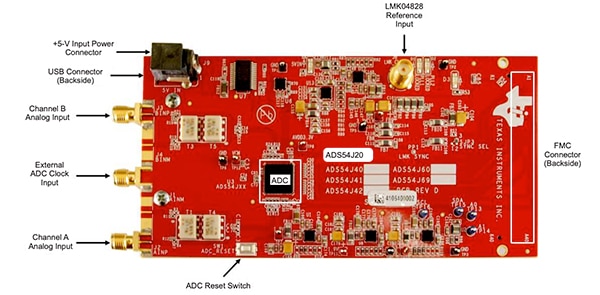

El ADS54J20 también cuenta con el soporte de la placa de evaluación, en este caso el ADS54J20EVM (Figura 8).

Figura 8: El ADS54J20 de alta velocidad es compatible con la placa de evaluación ADS54J20EVM que viene con un cable mini USB y un cable de alimentación. (Fuente de la imagen: Texas Instruments).

Figura 8: El ADS54J20 de alta velocidad es compatible con la placa de evaluación ADS54J20EVM que viene con un cable mini USB y un cable de alimentación. (Fuente de la imagen: Texas Instruments).

El ADS54J20EVM también se utiliza junto con el software HSDC Pro y viene con un cable mini USB para conectar a un PC, así como un cable de alimentación.

Conclusión:

Si bien los ADC SAR y ΔƩ tienen su lugar, la solución al desafío de las ADC de ultra alta velocidad es una ADC pipeline que procesa múltiples muestras y al mismo tiempo envía datos a su salida a velocidades de cientos de kilos-muestras-por-segundo a gigas-muestras-por-segundo. Sin embargo, no todos los ADC de oleoductos y gasoductos hacen hincapié sólo en la velocidad. Como se muestra, también se puede lograr una mayor precisión.

Independientemente del énfasis, los ADC en línea son una excelente opción para las estaciones base celulares de alta velocidad, las estaciones base de infraestructura celular multiportadora de ultra alta velocidad, las telecomunicaciones, las observaciones de predistorsión digital, los receptores de retroceso y muchas otras aplicaciones que requieren una conversión de alta velocidad.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.