Conceptos básicos analógicos-Parte 4: Optimización de los ADC Delta-Sigma para un bajo nivel de ruido

Colaboración de Editores de DigiKey de América del Norte

2020-08-05

Nota del editor: Los convertidores analógico-digital (ADC) conectan lo analógico con el mundo digital y por lo tanto son un componente fundamental de cualquier sistema electrónico que se conecta al mundo real. También son un factor determinante del rendimiento de un sistema. Esta serie explora los fundamentos de los CAD, sus diversos tipos y su aplicación. En la Parte 1 de esta serie, se analizaron los principios básicos analógicos de ADC SAR. En la Parte 2, se habla de los convertidores delta-sigma. En la Parte 3, mira los ADC pipeline. Aquí, la cuarta parte muestra cómo los ADC delta-sigma pueden generar resultados de ultra bajo ruido. En la Parte 5, se examinan las cuestiones difíciles de la conducción de insumos para los países en desarrollo sin litoral.

La topología del circuito integrado delta-sigma (ΔƩ) sigue apareciendo en los convertidores analógico-digitales (ADC), ofreciendo soluciones de alta resolución, alta integración y baja potencia para el control de procesos, la medición de temperatura de precisión y las aplicaciones de básculas de pesaje.

El hecho desconcertante de este tipo de convertidor es que comienza con una conversión de 1 bit con una relación señal-ruido (SNR) teórica de 7.78 decibelios (dB), lo que equivale a 2 voltios (VRMS) de ruido en un sistema de 5 voltios. A partir de ahí, el ADC puede convertirse en un auténtico convertidor delta-sigma de 24 bits que proporciona un SNR teórico de 146 dB, equivalente a 244 nanovoltios (nV) de ruido rms en un sistema de 5 voltios.

Este salto de resolución de 1 bit a 24 bits se basa en algoritmos de sobremuestreo, moduladores de forma de ruido y filtros digitales para reducir el ruido de cuantificación y aumentar el SNR. Hay una forma de evitar la complejidad del convertidor ΔƩ y su ruido asociado utilizando en su lugar una etapa de entrada de amplificador que alimenta a un ADC de registro de aproximación sucesiva (SAR) de 12 ó 16 bits. Esta ruta de diseño funcionará, pero requiere más circuitos integrados en la placa de la PC y un aumento de la lista de materiales.

Hay una mejor manera de abordar el problema del ruido: abordarlo de frente con un ADC ΔƩ de ultra-bajo ruido.

Este artículo analiza brevemente la aplicación de objetivo de bajo nivel de ruido y cómo el ADC ΔƩ está diseñado internamente para cumplir con este requisito. A continuación, presenta dos ADC ΔƩC de Texas Instruments -uno destacando la precisión de 24 bits, el otro destacando la precisión de 32 bits- mientras que muestra cómo aprovechar el robusto filtrado digital en ambos.

Donde el ADC ΔƩ encaja

Desde una perspectiva analógica, los ingenieros necesitan varios grados de precisión al medir la salida de los sensores de temperatura, presión, célula de carga y ópticos. Fundamentalmente, los amplificadores mejoran la capacidad de los diseñadores para cuantificar estas pequeñas, y en la mayoría de los casos cercanas a las ocurrencias analógicas de CC. La progresiva digitalización ha provocado un cambio de perspectiva y de capacidades, a la vez que ha mejorado la capacidad de almacenar y modificar las señales de los sensores.

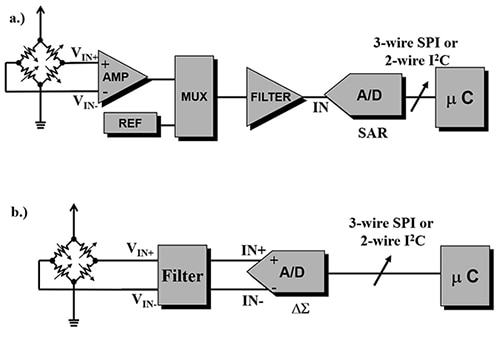

Un camino típico de la señal del sensor hacia la captura digital comienza con el sensor, se mueve a través de las etapas de ganancia, multiplexación y filtro, y luego hacia el ADC (Figura 1a).

Figura 1: Dos técnicas para digitalizar la señal de un sensor utilizan ADC (a) o ADC ΔƩ (b). Para los circuitos de alta resolución, el ADC SAR requiere amplificación y un filtro activo de quinto orden, mientras que el ADC ΔƩ requiere un filtro pasivo de primer orden analógico. (Fuente de la imagen: Baker’s Dozen: soluciones analógicas verdaderas para los diseñadores digitales, B. Baker, ISBN 0-7506-7819-4)

Figura 1: Dos técnicas para digitalizar la señal de un sensor utilizan ADC (a) o ADC ΔƩ (b). Para los circuitos de alta resolución, el ADC SAR requiere amplificación y un filtro activo de quinto orden, mientras que el ADC ΔƩ requiere un filtro pasivo de primer orden analógico. (Fuente de la imagen: Baker’s Dozen: soluciones analógicas verdaderas para los diseñadores digitales, B. Baker, ISBN 0-7506-7819-4)

El convertidor de la figura 1a es un ADC SAR que puede realizar conversiones de 12 a 18 bits y puede funcionar con tasas de conversión de hasta 10 megamuestras por segundo (MSPS). El convertidor de 16 bits proporciona 216 o 65.536 segmentos. En un sistema de 5 voltios, el bit menos significativo (LSB) es de 5 voltios/216298 o 76.3 microvoltios (mV), con una SNR teórica igual a 98 dB. Es posible lograr una mayor granularidad ejerciendo una ganancia analógica antes del convertidor de SAR.

La cadena de señales ΔƩ (Figura 1b) mejora la resolución de la cadena de señales con un solo convertidor, lo que también reduce el BOM. El ADC ΔƩ puede proporcionar conversiones de 16 a 32 bits. En esta cadena de señales, el ADC ΔƩ de 24 bits proporciona 224 o 16,777,216 segmentos. En un sistema de 5 voltios, el LSB es por lo tanto de 5 voltios/224, o 298 nV, con una SNR teórica igual a 146 dB. Este nivel de resolución acerca la granularidad del convertidor a las capacidades del sensor.

El ADC ΔƩ de 24 bits es más lento debido a los filtros digitales internos que requieren tiempo para implementar los cálculos de filtrado. Las tasas de datos de salida típicas de este convertidor van desde unos pocos hertzios hasta 1 MSPS. Tenga en cuenta que el filtro analógico es ahora un filtro de resistencia-capacitor (RC) de primer orden y económico, en lugar del complejo amplificador operacional de tres, filtro analógico de quinto orden.

Las diferencias entre el ruido de estos dos enfoques son claras: el ADC ΔƩ de bajo ruido supera al del ADC SAR (Tabla 1).

*Nota: SNR = 6.02 N + 1.76, donde N es el número de bits

|

Tabla 1: Segmentos ADC, LSB y SNR teóricos con voltaje de entrada a escala completa de 5 voltios para un ADC SAR de 16 bits y un ADC ΔƩ de 24 bits. (Origen de datos: DigiKey)

El ADC ΔƩ ofrece una excelente solución para soluciones de sensores, tales como temperatura, presión y célula de carga, donde la especificación de la velocidad no es crítica; sin embargo, la precisión es primordial. Este ADC puede convertir hasta estos pequeños valores de voltaje usando técnicas de reducción de ruido digitales, en lugar de analógicas.

Dentro del ADC ΔƩ

El interior del ADC ΔƩ es 80% digital. Generalmente, el convertidor recibe la señal de entrada e inmediatamente cambia esa señal analógica a digital. El convertidor combina entonces esa señal digital con conversiones posteriores del modulador en una etapa de filtro digital en la que la señal de 1 bit acumulada se cambia a múltiples bits. El convertidor envía entonces en serie la conversión multi-bit final al microcontrolador en espera a través de la etapa de salida digital.

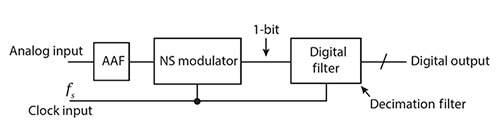

La señal analógica pasa primero a través de un filtro antialiasing de primer orden externo (AAF). Luego, el modulador de forma de ruido (NS) toma la señal analógica y genera un flujo de 1 bit a la velocidad del reloj del convertidor en el filtro digital (Figura 2).

Figura 2: El típico ΔƩ pone la señal analógica a través de un AAF de primer orden, genera un flujo de 1 bit usando el modulador NS, y luego produce un resultado multi-bit en la salida digital a un microcontrolador. (Fuente de la imagen: CMOS: Diseño de Circuito de Señal Mixta, 2nd Edición, J. Baker, ISBN 978-0-470-29026-2)

Figura 2: El típico ΔƩ pone la señal analógica a través de un AAF de primer orden, genera un flujo de 1 bit usando el modulador NS, y luego produce un resultado multi-bit en la salida digital a un microcontrolador. (Fuente de la imagen: CMOS: Diseño de Circuito de Señal Mixta, 2nd Edición, J. Baker, ISBN 978-0-470-29026-2)

El filtro digital registra múltiples códigos de la corriente de 1-bit y crea un resultado multi-bit completo en el filtro digital. Estos resultados multi-bit se transmiten en serie a través de la salida digital.

El modulador ΔƩ

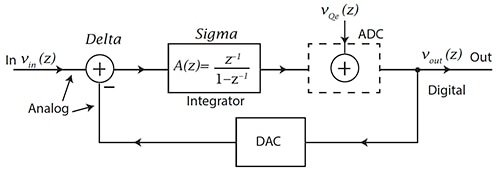

El número de bucles integradores/de retroalimentación determina el orden del modulador ΔƩ. El modulador ADC ΔƩ de primer orden tiene un único integrador y bucle de retroalimentación (Figura 3).

Figura 3: Modulador de primer orden con un integrador analógico y un ADC de 1 bit y un DAC en el bucle de retroalimentación. VQe(z) es la cuantificación del ruido del ADC. (Fuente de la imagen: CMOS: Mixed-Signal Circuit Design, 2.º edición, J. Baker, ISBN 978-0-470-29026-2)

Figura 3: Modulador de primer orden con un integrador analógico y un ADC de 1 bit y un DAC en el bucle de retroalimentación. VQe(z) es la cuantificación del ruido del ADC. (Fuente de la imagen: CMOS: Mixed-Signal Circuit Design, 2.º edición, J. Baker, ISBN 978-0-470-29026-2)

En la figura 3, la señal analógica (VIN(z)) entra en la porción Delta (Δ) del modulador. La señal analógica pasa entonces por una etapa integradora o etapa Sigma (Ʃ) a un ADC de 1 bit (con una tasa de muestreo de fS, según la Figura 2), que puede ser un comparador. Esta señal digitalizada ahora cronometrada se retroalimenta al convertidor digital-analógico (DAC) de 1 bit y también procede al VOUT(z) en la etapa Δ. El DAC de 1 bit presenta un voltaje analógico que debe ser restado de la señal de entrada analógica, VIN(z). La función de transferencia de este modulador de primer orden es:

![]() Ecuación 1

Ecuación 1

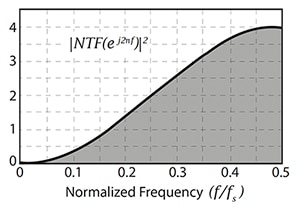

Debido al integrador y al bucle de retroalimentación, el modulador implementa un algoritmo de formación de ruido en el flujo de datos de salida digital del modulador (Figura 4).

Figura 4: La función de transferencia de ruido a la salida del modulador ΔƩ, donde la función de transferencia de ruido (NTF) es igual a 1-z-1, donde el 0.5 frecuencia normalizada es igual a FS/2. (Fuente de la imagen: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

Figura 4: La función de transferencia de ruido a la salida del modulador ΔƩ, donde la función de transferencia de ruido (NTF) es igual a 1-z-1, donde el 0.5 frecuencia normalizada es igual a FS/2. (Fuente de la imagen: Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

En la figura 4, la característica de formación de ruido es el primer paso para reducir la conversión del ruido de cuantificación de 1 bit. Con el ruido empujado con éxito a frecuencias más altas, un filtro digital de paso bajo completa el proceso de reducción de ruido.

Los moduladores de orden superior contienen integradores adicionales y bucles de retroalimentación. Por ejemplo, un modulador de tercer orden tiene tres integradores y tres bucles de retroalimentación. La función de modelación del ruido cambia con el orden del modulador reduciendo el ruido cerca de la DC y aumentando el ruido modelado.

Los moduladores de alto orden ofrecen un mejor rendimiento a expensas de más hardware de silicio, menor estabilidad y alcance de la señal.

Los filtros digitales de ΔƩ

El ADC ΔƩ funciona mediante el uso de sobremuestreo (OS). El sobremuestreo es la relación entre la tasa de muestreo del modulador (FS) y la tasa de datos de salida del ADC (FD), según la ecuación 2:

![]() Ecuación 2

Ecuación 2

El sobremuestreo mejora el ruido del ADC ΔƩ al limitar digitalmente el ancho de banda de los datos en forma de ruido con un filtro o filtros digitales de paso bajo.

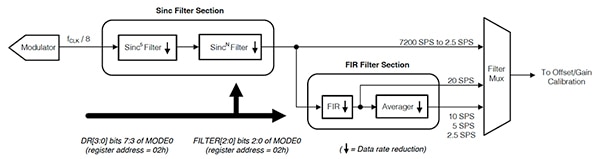

Los dos filtros digitales que se utilizan comúnmente en el ADC ΔƩ son los filtros sin(pf)/pf (sinc) y los filtros de fase lineal de respuesta a impulsos finitos (FIR). La implementación del filtro digital del ADC ΔƩADS1235 de 24 bits, el ADS1262 y ADS1263 32 bits (el ADS1263 integra un auxiliar, ADC ΔƩ de 24 bits de Texas Instruments destinado a las mediciones de fondo), ofrece una elección del uso de los filtros sinc exclusivamente, o una combinación de sinc seguido por los filtros FIR (Figura 5).

Figura 5: El ADC ΔƩ ADS1235 de 24 bits ofrece el uso de los filtros sinc exclusivamente, o una combinación de sinc seguido de los filtros FIR. (Fuente de la imagen: Texas Instruments)

Figura 5: El ADC ΔƩ ADS1235 de 24 bits ofrece el uso de los filtros sinc exclusivamente, o una combinación de sinc seguido de los filtros FIR. (Fuente de la imagen: Texas Instruments)

En la figura 5, el filtro sinc (denominado "Sinc") es un filtro digital de paso bajo. La salida (w(n)) de un filtro sincero se calcula utilizando la Ecuación 3:

![]() Ecuación 3

Ecuación 3

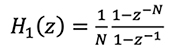

La función de transferencia del dominio z es:

Ecuación 4

Ecuación 4

La respuesta de frecuencia es:

![]() Ecuación 5

Ecuación 5

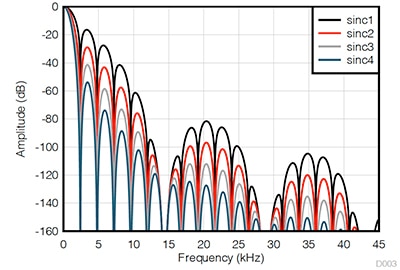

En la figura 5, SincN equivale a N filtros sinceros idénticos en serie. La amplitud gráfica frente a la respuesta de frecuencia del filtro sinc tiene un aspecto de peine (Figura 6).

Figura 6: En el ADS1262/63, a 2400 muestras por segundo (SPS) los numerosos filtros digitales sinc - en los que sinc2 equivale a dos filtros SINC idénticos en serie y sinc3 equivale a tres filtros sinc idénticos en serie, etc. - crean la respuesta en frecuencia tipo peine. (Fuente de la imagen: Texas Instruments)

Figura 6: En el ADS1262/63, a 2400 muestras por segundo (SPS) los numerosos filtros digitales sinc - en los que sinc2 equivale a dos filtros SINC idénticos en serie y sinc3 equivale a tres filtros sinc idénticos en serie, etc. - crean la respuesta en frecuencia tipo peine. (Fuente de la imagen: Texas Instruments)

En la figura 6, los picos y nulos son característicos de la respuesta del filtro sinc. Los nulos de respuesta de frecuencia se producen a f (Hz) = N -FD, donde N = 1, 2, 3, ... En las frecuencias nulas, el filtro tiene ganancia cero.

Los filtros sinc (en serie) crean una mayor atenuación, causando un aumento de la latencia. Por ejemplo, si el cálculo de un filtro sincro específico con una velocidad de reloj externo de 7,3728 MHz produce una velocidad de datos de salida de 14400 SPS, la velocidad de datos de salida del segundo filtro sincro es de 7200 SPS.

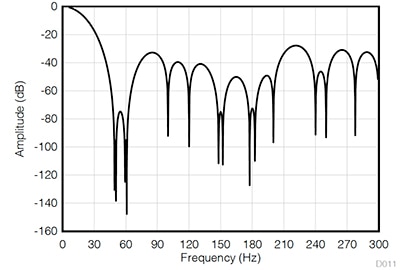

El filtro FIR de paso bajo es un filtro basado en coeficientes. El filtro tiene una atenuación simultánea de 50 Hz y 60 Hz y armónicos a velocidades de datos de 2.5 SPS a 20 SPS. El tiempo de latencia de conversión de las tasas de datos del filtro FIR es equivalente a un solo ciclo. El filtro FIR recibe datos prefiltrados del filtro sinc y diezma los datos para obtener las tasas de datos de salida de 10 SPS (Figura 7).

Figura 7: En el ADS1262/63, el filtro FIR atenúa las señales de 50 Hz y 60 Hz para reducir las interferencias de frecuencia de línea y proporciona una serie de nulos de respuesta situados cerca de estas frecuencias. Los nulos se repiten en los armónicos de 50 y 60 Hz. (Fuente de la imagen: Texas Instruments)

Figura 7: En el ADS1262/63, el filtro FIR atenúa las señales de 50 Hz y 60 Hz para reducir las interferencias de frecuencia de línea y proporciona una serie de nulos de respuesta situados cerca de estas frecuencias. Los nulos se repiten en los armónicos de 50 y 60 Hz. (Fuente de la imagen: Texas Instruments)

El filtro FIR atenúa las señales de 50 Hz y 60 Hz para reducir las interferencias de frecuencia de línea y proporciona una serie de nulos de respuesta situados cerca de estas frecuencias. Los nulos de respuesta se repiten en los armónicos de 50 y 60 Hz.

ADC ΔƩ preciso y de bajo ruido

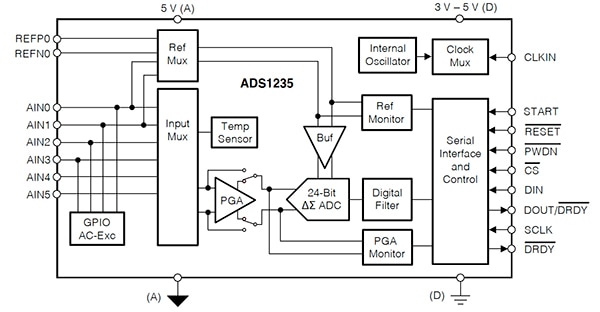

Un excelente ejemplo de un ADC ΔƩ de bajo ruido es el anteriormente mencionado convertidor de 24 bits de entrada diferencial ADS1235 de Texas Instruments.

El ADS1235 es un ADC ΔƩ de precisión, 7200 SPS, con tres diferenciales o cinco entradas de un solo extremo y un amplificador de ganancia programable integrado (PGA) con ganancias de 1, 64 y 128. Este dispositivo también incluye características de diagnóstico como monitores de referencia y PGA sobre el alcance. El ADC proporciona datos de conversión de alta precisión y cero deriva para equipos de alta precisión, incluyendo básculas, medidores de tensión y sensores de presión resistiva (Figura 8).

Figura 8: El diagrama de bloques del ADC ΔƩ ADS1235 de 24 bits con una entrada analógica de seis canales y un multiplexor de entrada GPIO. (Fuente de la imagen: Texas Instruments)

Figura 8: El diagrama de bloques del ADC ΔƩ ADS1235 de 24 bits con una entrada analógica de seis canales y un multiplexor de entrada GPIO. (Fuente de la imagen: Texas Instruments)

Para el ADS1235, los factores significativos que afectan al rendimiento del ruido son la velocidad de datos, la ganancia PGA y el modo de corte. Las velocidades de datos más lentas traen la frecuencia de esquina del filtro digital, reduciendo así el ruido. Además, debido a un promedio de datos de dos puntos, realizado en el modo de corte, el ruido disminuye en √2 en comparación con el funcionamiento normal.

Con una baja frecuencia, una velocidad de datos de 2.5 SPS y una ganancia PGA de 1 voltio/voltio, el ruido del convertidor a la salida digital sinc3 en un sistema de 5 voltios es de 0.15 mVRMS (0.3 mV de pico a pico (PP)) con una resolución efectiva de 24 bits, así como una resolución libre de ruido de 24 bits. El SNR teórico, así como el real, de este dispositivo es de 146 dB. De hecho, con estas condiciones, el modulador estable de cuarto orden y los filtros de sinc1 a sinc4 producen 24 bits de resolución efectiva, así como una resolución libre de ruido de 24 bits.

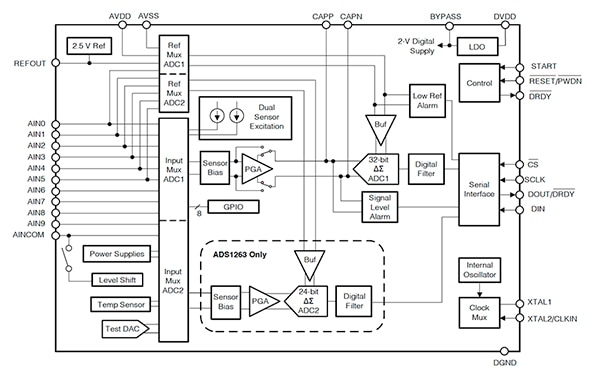

El ADS1235 ha realizado conversiones casi perfectas de 24 bits para una velocidad de datos de 2.5 SPS. El ADC ΔƩ de próxima generación en esta familia es el ADS1262/63 de Texas Instruments. La principal diferencia entre estos dispositivos es que el ADS1262/63 mejora el circuito de bajo ruido y ofrece un registro de datos de salida ampliado de 32 bits.

El ADS1262/63 tiene un PGA CMOS mejorado de bajo ruido con ganancias de 1, 2, 4, 8, 16 y 32. El frontal analógico flexible (AFE) incorpora dos fuentes de corriente de excitación sensorial adecuadas para las mediciones directas de RTD (Figura 9).

Figura 9: El diagrama de bloques del ADC ΔƩ de 32 bits ADS1262 y ADS1263 con multiplexor de entrada analógica de diez canales. El ADS1263 tiene un segundo ADC ΔƩ en chip de 24 bits. (Fuente de la imagen: Texas Instruments)

Figura 9: El diagrama de bloques del ADC ΔƩ de 32 bits ADS1262 y ADS1263 con multiplexor de entrada analógica de diez canales. El ADS1263 tiene un segundo ADC ΔƩ en chip de 24 bits. (Fuente de la imagen: Texas Instruments)

Al igual que con el ADS1235, la ganancia PGA, la velocidad de datos, el modo de filtro digital y el modo de corte son los factores significativos que afectan al rendimiento del ruido con el ADS1262/63. Con una resolución de 32 bits, el ADS1262/63 muestra realmente la capacidad de profundidad de bajo ruido.

Para empezar, un modulador estable de cuarto orden y los filtros del sinc1 al sinc4 conducen a la producción de 32 bits de resolución efectiva, así como una resolución libre de ruido de 24 bits. Configurando una baja frecuencia, una velocidad de datos de 2.5 SPS y una ganancia PGA de 1 voltio/voltio (desviada), el ruido del convertidor de la salida digital del sinc3 en un sistema de 5 voltios es de 0,08 mVRMS (0.307 mVPP). Este dispositivo supera la resolución efectiva con 26.9 bits, así como una resolución libre de ruido de 25 bits. Para este sistema de 32 bits la SNR teórica es de 387 dB, siendo la SNR real de 164 dB.

Las diferencias entre el ruido de los convertidores de 24 y 32 bits son claras, donde la capacidad de bajo ruido del ADC de 32 bits supera la del ADC ΔƩ de 24 bits (Tabla 2).

*Nota: SNR = 6.02 N + 1.76, donde N es # de bits

|

Tabla 2: Comparación del ruido rms del ADC, el ruido de pico a pico y el SNR con un voltaje de entrada a escala completa de 5 voltios. (Origen de datos: DigiKey)

Conclusión:

El ADC ΔƩ continúa empujando los límites de bajo ruido con una capacidad continuamente añadida. Este artículo muestra cómo este ADC casi digital y de bajo ruido se conecta directamente con las aplicaciones de temperatura, presión y células de carga. Una discusión de tuercas y tornillos de ADC ΔƩ de precisión y de 24 bits y 32 bits esboza el camino para realizar sus características ultra-precisa.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.