Conceptos básicos de la analogía - Parte 1: Convertidores analógicos-digitales de SAR

Colaboración de Editores de DigiKey de América del Norte

2020-04-15

Nota del editor: Los convertidores analógico-digital (ADC) conectan lo analógico con el mundo digital y por lo tanto son un componente fundamental de cualquier sistema electrónico que se conecta al mundo real. También son un factor determinante del rendimiento de un sistema. Esta serie explora los fundamentos de los CAD, sus diversos tipos y su aplicación. En la primera parte de esta serie sobre fundamentos analógicos, se examinarán las sucesivas SAE de registro de aproximación (SAR). En la segunda parte se discutirán los convertidores delta-sigma (ΔƩ).

Sigue siendo un mundo analógico, así que para llevar la información sensada al dominio digital, es necesario que se produzca algún tipo de conversión. Este trabajo pesado se reserva principalmente para el convertidor analógico-digital (ADC). A lo largo de los años, las tres topologías de la CAD que han cobrado importancia son el registro de aproximación sucesiva (SAR), el sigma-delta (S-D) y la CAD en línea. Las tres topologías del CAD son profundamente diferentes para operar en diferentes gamas de frecuencia para dar servicio a todo, desde aplicaciones de sensores de baja frecuencia hasta comunicaciones de alta frecuencia de LIDAR o satélites, y más allá.

El CAD de la SAR fue el primer convertidor que se convirtió a la corriente principal. Con el tiempo, esta topología de convertidor apareció en una variedad de aplicaciones, incluyendo el control de procesos, médico y los primeros sistemas de audio digital. Estas aplicaciones se benefician de los rangos de conversión de salida de la CAD de la SAR de 8 bits a 20 bits. Sin embargo, la afirmación de la CAD de la SAR es que captura una instantánea de la señal de entrada analógica, utilizando múltiples instantáneas de la señal para dibujar un cuadro a lo largo del tiempo.

Este artículo describe brevemente la cadena de señales que rodea al SAE. A partir de ahí, profundiza en esta topología de la CAD con un análisis de la etapa de entrada fundamental que es responsable de la acción instantánea de la CAD. A continuación, el artículo presenta ejemplos de soluciones de ADC SAR, AD7625BCPZ y AD4020BCPZ-RL7 de Analog Devices, centrándose en la mecánica de conversión analógica a digital interna del ADC4020BCPZ-RL7. También se proporcionan especificaciones clave para un sistema de adquisición de datos adecuado.

La cadena de señales analógicas del ADC SAR

La ADC SAR aparece en sistemas como el equipo de pruebas automáticas, la automatización de máquinas, el equipo médico y la adquisición de datos de precisión. En todas las aplicaciones de la ADC SAR hay una señal analógica que requiere una representación digital con una resolución modesta de 8 a 20 bits, con un muestreo de CC proximado a 15 megamuestras por segundo (MSPS) (en el momento de redactar este informe).

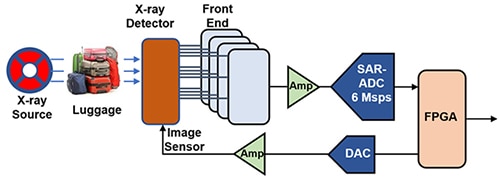

El ADC SAR puede operar sin una cadena de señales analógicas frontales (AFE). Sin embargo, si el trabajo del diseñador es también presentar con éxito una señal en el front-end del ADC SAR, es más probable que se requiera un cierto grado de acondicionamiento de la señal (Figura 1).

Figura 1: Esta cadena de señales ADC SAR de muestra incluye un detector de rayos X, un AFE, un controlador de amplificación, un convertidor MSPS AD7625BCPZ 6 de dispositivo analógico y un receptáculo digital para los resultados de la conversión (el FPGA). (Fuente de la imagen: DigiKey)

Figura 1: Esta cadena de señales ADC SAR de muestra incluye un detector de rayos X, un AFE, un controlador de amplificación, un convertidor MSPS AD7625BCPZ 6 de dispositivo analógico y un receptáculo digital para los resultados de la conversión (el FPGA). (Fuente de la imagen: DigiKey)

En la figura, una fuente de rayos X envía una señal a través del equipaje al detector de rayos X. El trabajo del dispositivo de rayos X es construir una imagen completa del equipaje en un corto período de tiempo para reducir la frustración del viajero.

El front-end toma la señal del detector y realiza funciones de acondicionamiento de la señal como la ganancia analógica y el cambio de nivel. La señal se presenta entonces al ADC SAR, que en este caso es el AD7625BCPZ de Analog Devices.

El amplificador anterior al ADC SAR proporciona una estabilidad adecuada, normalmente con un filtro de paso bajo de primer orden entre el amplificador y el ADC SAR. El ADC SAR es capaz de tomar muestras de hasta 6 MSPS -una muestra cada 167 nanosegundos (ns)- para acomodar múltiples instantáneas en un corto período de tiempo.

El núcleo de la etapa de entrada del ADC SAR se simplificó.

El ADC SAR ha sido objeto de numerosas mejoras y perfeccionamientos a lo largo del tiempo, pero en todos los casos la actividad principal durante el período de conversión es la redistribución de la carga, una de las aplicaciones más comunes del ADC de aproximación sucesiva. Además, con el ADC SAR, existe la ventaja adicional de latencia cero, a diferencia del S-D y el convertidor de tuberías.

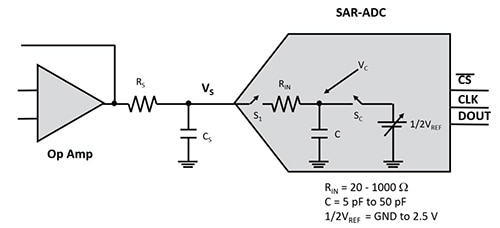

En el nivel más simple, es fácil ver dónde se produce la instantánea de la señal. El núcleo de entrada del ADC SAR contiene un interruptor de adquisición de la señal de entrada (S1), una matriz capacitiva, un interruptor de conversión (SC) y un voltaje de referencia interno (½ VREF) (Figura 2).

Figura 2: Un amplificador operacional (op amp), con un filtro estabilizador de salida, conduciendo un ADC SAR. (Fuente de la imagen: DigiKey)

Figura 2: Un amplificador operacional (op amp), con un filtro estabilizador de salida, conduciendo un ADC SAR. (Fuente de la imagen: DigiKey)

El funcionamiento del núcleo del ADC SAR es el siguiente:

- S1 se abre, SC se cierra: Esto desconecta la etapa de entrada de la fuente de la señal analógica.

- La carga en C es recalibrada por ½ VREF. Esta recalibración lleva al ADC SAR de vuelta a la zona cero.

- Entonces S1 se cierra, SC se abre: Ahora el dispositivo está conectado a la señal analógica de entrada.

- La CAD SAR adquiere la señal de entrada, VS, durante un tiempo de adquisición predeterminado. Este tiempo de adquisición permite la exposición repentina de S1 y SC al ruido de conmutación y la exposición repentina del amplificador a la carga del condensador y al ruido de conmutación.

- Entonces S1 se abre: Este es el ejemplo exacto en el que se produce la instantánea de la señal.

- El ADC SAR convierte la señal en VC a su representación digital. El tiempo que se tarda en hacer esto es el "tiempo de conversión".

Detalles del núcleo de la etapa de entrada del ADC SAR

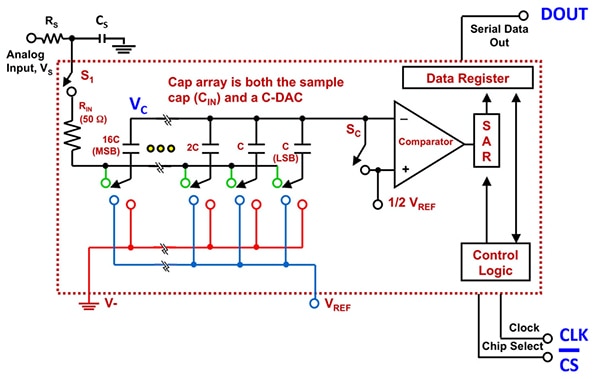

El núcleo de conversión se ocupa de la redistribución de la carga de la señal capturada en VC. La orquestación de la redistribución de la carga del convertidor se produce en el núcleo, cerrado por el reloj. A partir de este proceso, cada código de salida digital cronometrado llega a la salida DOUT del ADC SAR (Figura 3).

Figura 3: Una cortina del ADC SAR de 4 bits tiene una completa gama de capacitores con peso digital: 16C, 8C, 4C, 2C y dos C. (Fuente de la imagen: DigiKey)

Figura 3: Una cortina del ADC SAR de 4 bits tiene una completa gama de capacitores con peso digital: 16C, 8C, 4C, 2C y dos C. (Fuente de la imagen: DigiKey)

Como primer paso durante la conversión, el algoritmo ADC SAR determina el bit más significativo (MSB). El ACD SAR comienza a probar la magnitud de la señal en comparación con ½ VREF cambiando la parte inferior del capacito 16C entre las entradas del comparador V y VREF. La siguiente comparación en la línea de conversión de ADC SAR es la prueba del 8C (no se muestra) contra ½ VREF, seguida de la prueba del 4C, etc.

Detalles de la conversión de la producción de ACD SAR

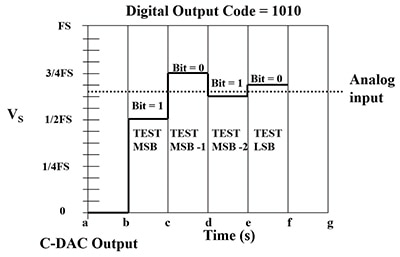

La decisión del MSB se transmite inmediatamente a través de la clavija DOUT, y el interruptor del MSB permanece congelado, mientras que la decisión del MSB 1 se toma. El ADC SAR lleva este algoritmo hasta la selección final del bit menos significativo (LSB) (Figura 4).

Figura 4: El ADC SAR de 4 bits registra el algoritmo de conversión a través de decisiones de bits y transmite esas decisiones a través de la clavija DOUT (que se muestra en la figura 3). (Fuente de la imagen: DigiKey)

Figura 4: El ADC SAR de 4 bits registra el algoritmo de conversión a través de decisiones de bits y transmite esas decisiones a través de la clavija DOUT (que se muestra en la figura 3). (Fuente de la imagen: DigiKey)

En la figura 4, las decisiones de bits de ADC SAR se toman desde el MSB hasta el LSB. Todos los datos de conversión continúan siendo registrados inmediatamente a través de DOUT en la parte superior derecha de la figura 3. Un tiempo de rendimiento completo generalmente requiere un tiempo amplio para la adquisición de la señal y un ciclo de reloj para cada bit.

Desafíos de la conversión de la SAARC

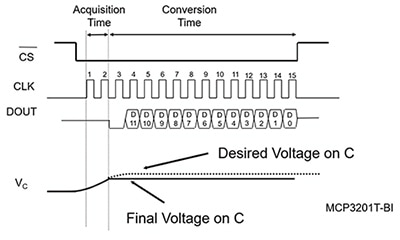

El diseñador debe ser consciente de la cantidad de tiempo de asentamiento de la señal que se necesita para asegurar que se capte el valor analógico correcto de la conversión (Figura 5).

Figura 5: El diagrama de tiempo de conversión de un DAC SAR de 12 bits. Cada conversión completa requiere 16 relojes. (Fuente de la imagen: DigiKey)

Figura 5: El diagrama de tiempo de conversión de un DAC SAR de 12 bits. Cada conversión completa requiere 16 relojes. (Fuente de la imagen: DigiKey)

En la figura 5, la señal de entrada, VC, no ha alcanzado su voltaje final deseado antes de que se abra el interruptor de entrada del convertidor. En este caso, el diseñador del circuito ha calculado mal el tiempo de asentamiento de la señal de entrada del amplificador.

El ADC SAR AD4020BCPZ-RL7 de 20 bits y 1.8 MSPS alivia la complejidad de la adquisición de la señal al ofrecer una fase de adquisición extendida, manteniendo al mismo tiempo la tasa de rendimiento. Tiene una baja relación señal-ruido (SNR) de 100.5 dB.

Función de transferencia del ADC SAR

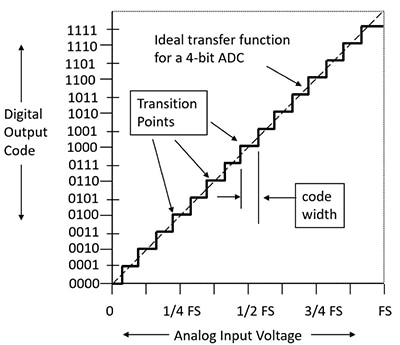

El número de códigos posibles para las SAE es igual a 2N, donde N es el número de bits. Por ejemplo, un convertidor de 4 bits tiene 24 o 16 códigos separados disponibles (Figura 6).

Figura 6: La función de transferencia, o gráfico del código de salida digital frente al voltaje de entrada analógico de un ADC SAR ideal de 4 bits, debería ser una línea recta. (Fuente de la imagen: DigiKey)

Figura 6: La función de transferencia, o gráfico del código de salida digital frente al voltaje de entrada analógico de un ADC SAR ideal de 4 bits, debería ser una línea recta. (Fuente de la imagen: DigiKey)

Pintar el cuadro

La tasa de rendimiento del ADC SAR incluye el tiempo de adquisición y el tiempo de conversión para lograr tasas de rendimiento de hasta 1.8 MSPS con una resolución de 20 bits a partir del AD4020BCPZ-RL7 de Analog Devices. Con la velocidad de rendimiento del AD4020BCPZ-RL7, es posible adquirir múltiples instantáneas y crear una solución de representación de imágenes digitales para la automatización de máquinas y equipos médicos.

Conclusión

Al utilizarse en aplicaciones que van desde el control de procesos hasta el ámbito médico y de consumo, el ADC SAR sigue demostrando su valía con su capacidad de captación de señales y la mejora constante de la resolución y la velocidad. El ADC SAR en este momento viene con resoluciones de 8 a 20 bits, con tasas de rendimiento de hasta 15 MSPS. Un ejemplo, el AD4020BCPZ-RL de Analog Devices ofrece bajo ruido, alta velocidad, y 20 bits, 1.8 MSPS de precisión. Sin embargo, la arquitectura de los convertidores ADC SAR aún no está terminada. Hay más por venir.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.