Conceptos básicos analógicos, parte 5: Abordar los problemas de conducción de entrada difíciles para el CAD del SAR

Colaboración de Editores de DigiKey de América del Norte

2020-10-28

Nota del editor: Los convertidores analógico-digital (ADC) conectan lo analógico con el mundo digital y por lo tanto son un componente fundamental de cualquier sistema electrónico que se conecta al mundo real. También son un factor determinante del rendimiento de un sistema. Esta serie explora los fundamentos de los CAD, sus diversos tipos y su aplicación. En la Parte 1 de esta serie, se analizaron los principios básicos analógicos de ADC SAR. En la Parte 2, se habla de los convertidores delta-sigma. En la Parte 3, se analizan las SAE de las tuberías. En la Parte 4, se muestra cómo las SAE delta-sigma pueden generar resultados de ultra-bajo ruido. En la Parte 5, se examinan las cuestiones difíciles de entrada para los ADC SAR.

Muchas aplicaciones de adquisición de datos, control industrial e instrumentación requieren un convertidor analógico-digital (ADC) de ultra alta velocidad cuando un convertidor de registro de aproximación sucesiva (SAR) es perfectamente adecuado. Sin embargo, es esencial asegurar que los circuitos externos alrededor del convertidor de SAR también estén a la altura de la tarea para asegurar un resultado de conversión exitoso. Los terminales cruciales que requieren un cuidado especial para el convertidor de SAR son sus entradas de señal analógica; si se dejan desatendidas, estas clavijas de entrada pueden producir problemas de estabilidad y "contragolpes" de carga capacitiva que pueden dar lugar a conversiones inexactas y alargar el tiempo de adquisición de la señal.

La solución para el control preciso de la señal de entrada para las aplicaciones de convertidores de SAR radica en el accionamiento de amplificadores operacionales (op-amps). Estos dispositivos, apoyados por los valores adecuados de resistencia de salida y condensador, son la base de una solución resistente y de alta precisión para los sistemas convertidores de SAR de 16 y 20 bits de alta resolución.

En el presente artículo se examinan brevemente las cuestiones relacionadas con el logro de conversiones estables y precisas del ADC SAR. A continuación, se presenta un amplificador de operación apropiado para conducir un ADC SAR y muestra cómo implementar los circuitos conductores de entrada necesarios. Las soluciones de los dispositivos analógicos se utilizarán a modo de ejemplo.

Circuitos de entrada del ADC SAR

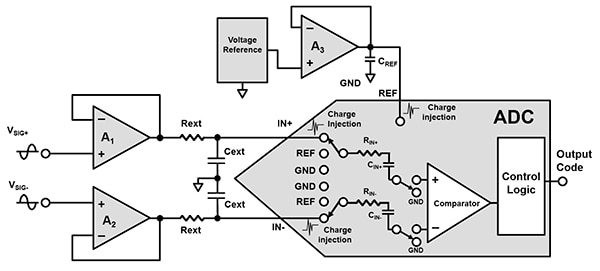

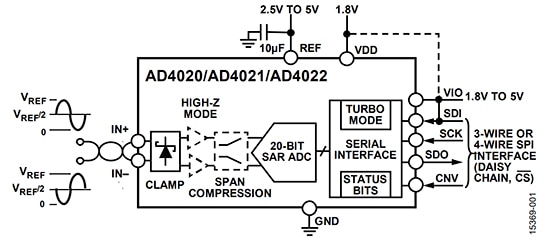

Los circuitos conductores del ADC SAR tienen amplificadores ópticos (A1 yA2) que separan el ADC de sus fuentes de señal (figura 1). En este circuito, Rext mantiene el amplificador estable "aislando" la etapa de salida del amplificador de la carga capacitiva ADC (CIN+ y CIN-) y Cext. Cext y CREF proporcionan una fuente de entrada casi perfecta para el ADC que absorbe la inyección de carga de conmutación de los terminales de entrada IN+, IN- y REF. Los terminales de entrada (IN+, IN-) rastrean el voltaje de la señal de entrada (VSIG+, VSIG-) durante el tiempo de adquisición del convertidor, proporcionando carga a los condensadores de muestreo de entrada del ADC, CIN+ y CIN-.

Figura 1: En este circuito, Rext "aísla" a Cext de la etapa de salida del amplificador de operaciones. Cext y CREF proporcionan depósitos de carga para el ADC diferencial de la SAR durante el período de muestreo. (Fuente de la imagen: Digi-Key Electronics)

Figura 1: En este circuito, Rext "aísla" a Cext de la etapa de salida del amplificador de operaciones. Cext y CREF proporcionan depósitos de carga para el ADC diferencial de la SAR durante el período de muestreo. (Fuente de la imagen: Digi-Key Electronics)

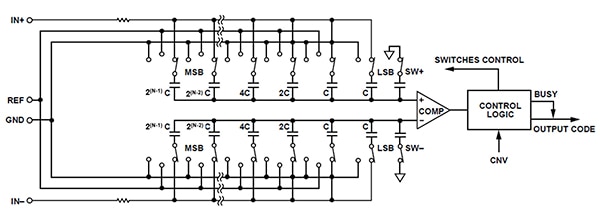

Si se observa el interior del ADC utilizando como ejemplos los ADC SAR AD7915 (16 bits) y AD4021 (20 bits) de Analog Devices, se puede ver que utiliza un convertidor digital-analógico (DAC) de redistribución de carga. El DAC capacitivo tiene dos conjuntos idénticos de condensadores de ponderación binaria. Estas matrices se conectan a las entradas del comparador no inversor y del comparador inversor (Figura 2).

Figura 2: Un esquema simplificado basado en AD7915 y AD4021 de un ADC SAR, donde N es igual al número de bits del convertidor. (Fuente de la imagen: Modificado por Digi-Key Electronics a partir de material original de Analog Devices)

Figura 2: Un esquema simplificado basado en AD7915 y AD4021 de un ADC SAR, donde N es igual al número de bits del convertidor. (Fuente de la imagen: Modificado por Digi-Key Electronics a partir de material original de Analog Devices)

Durante la fase de adquisición, las entradas (IN+ y IN-) cambian a la matriz capacitiva. Además, SW+ y SW- se cierran, conectando los capacitores de bits menos significativos (LSB) a tierra (GND). En este estado, los conjuntos de capacitores se convierten en los capacitores de muestreo, adquiriendo las señales analógicas IN+ e IN-. Una vez completada la fase de adquisición, la entrada de la CNV a la lógica de control (lado derecho) se eleva para iniciar la fase de conversión.

La fase de conversión comienza con la apertura de SW+ y SW- y la conmutación de los dos conjuntos de capacitores a GND. En esta configuración, el voltaje diferencial capturado IN+ y IN- hace que el comparador se desequilibre. El DAC de redistribución de carga cambia metódicamente cada elemento del conjunto de capacitores de bit más significativo (MSB) a LSB, entre GND y REF. La entrada del comparador varía por pasos de tensión con ponderación binaria (VREF/2N-1, VREF/2N-2... VREF/4, VREF/2). La lógica de control cambia los interruptores del MSB al LSB, llevando al comparador a una condición de equilibrio. Una vez completado este proceso, el CAD vuelve a la fase de adquisición, y la lógica de control genera el código de salida del CAD.

Inyección de carga de entrada, estabilidad del circuito y conducción del ADC AD7915

Una parte crítica del proceso de conversión es adquirir un voltaje de señal de entrada preciso. El proceso de conversión de datos del ADC funciona sin problemas cuando el amplificador de conducción carga con precisión los condensadores de entrada, CIN+ y CIN-, manteniendo la estabilidad hasta el final del tiempo de adquisición de la CAD. El problema para los diseñadores es que el terminal de entrada del ADC introduce una capacitancia (CIN+, CIN-) así como ruido de conmutación o inyección de carga "kickback" para que el amplificador de conducción lo maneje.

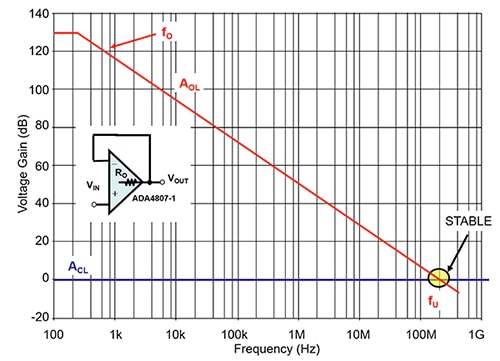

Un circuito de amplificación Bode plotter rápidamente estima la estabilidad del circuito. La herramienta de trazado Bode aproxima la magnitud de las funciones de transferencia de ganancia de lazo abierto y de lazo cerrado de un amplificador (Figura 3).

Figura 3: La función de transferencia en lazo abierto y cerrado del amplificador de la figura 1, sin Rext y Cext como cargas del amplificador y el siguiente ADC SAR. (Fuente de la imagen: Digi-Key Electronics)

Figura 3: La función de transferencia en lazo abierto y cerrado del amplificador de la figura 1, sin Rext y Cext como cargas del amplificador y el siguiente ADC SAR. (Fuente de la imagen: Digi-Key Electronics)

El eje y cuantifica la ganancia de lazo abierto (AOL) y la ganancia de lazo cerrado (ACL) del circuito del amplificador, donde la curva AOL del amplificador comienza a 130 decibelios (dB) y la ganancia de lazo cerrado,ACL, es igual a 0 dB. Las unidades a lo largo del eje x cuantifican logarítmicamente la frecuencia de ganancia de lazo abierto y cerrado de 100 Hertz (Hz) a 1 gigahertz (GHz).

En la figura 3, la ganancia de bucle abierto de CC del amplificador a aproximadamente 220 Hz (fO) progresa hacia abajo desde 130 dB a una tasa de -20 dB/década. A medida que la frecuencia aumenta, esta tasa de atenuación continúa más allá de 0 dB a aproximadamente 180 megahercios (MHz). Dado que esta curva representa un sistema unipolar, la frecuencia de cruce, fU, es igual al producto de ancho de banda del amplificador de ganancia estable de la unidad (GBWP). Este gráfico representa un sistema estable porque la tasa de cierre del AOL y elACL es de 20 dB/década.

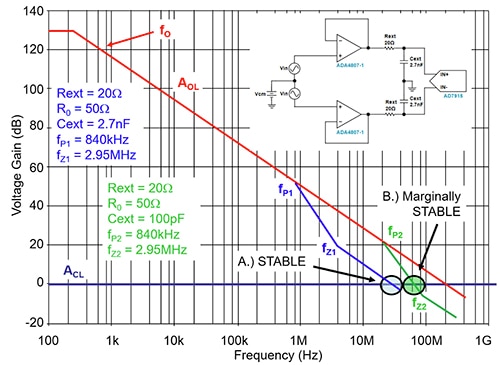

La adición de Rext y Cext y el ADC SAR modifica el circuito del amplificador creando un sistema cero y polo (Figura 4). El sistema consta de un amplificador ADC PulSAR diferencial AD7915 de 16 bits y 1 megamuestra por segundo (MSPS) y un amplificador ADA4807-1 de 180 MHz, de entrada/salida de carril a carril, ambos de Analog Devices. La combinación del amplificador y el ADC requiere Rext debido a la carga de capacitancia de entrada del ADC de 30 picofaradios (pF) (típicamente). El circuito también requiere que Cext actúe como un cubo de carga para proporcionar suficiente carga en la entrada del ADC para que coincida exactamente con el voltaje de entrada.

Figura 4: Se muestra la respuesta del gráfico Bode de dos amplificadores de operación ADA4807 que accionan el ADC SAR AD7915 con dos pares Rext/Cext separados. Las frecuencias de las esquinas fP1 y fZ1 modifican la ganancia de bucle abierto del amplificador, creando una respuesta estable del sistema. Las frecuencias de las esquinas fP2 y fZ2 modifican la ganancia de bucle abierto del amplificador, creando una respuesta marginalmente estable. (Fuente de la imagen: Digi-Key Electronics)

Figura 4: Se muestra la respuesta del gráfico Bode de dos amplificadores de operación ADA4807 que accionan el ADC SAR AD7915 con dos pares Rext/Cext separados. Las frecuencias de las esquinas fP1 y fZ1 modifican la ganancia de bucle abierto del amplificador, creando una respuesta estable del sistema. Las frecuencias de las esquinas fP2 y fZ2 modifican la ganancia de bucle abierto del amplificador, creando una respuesta marginalmente estable. (Fuente de la imagen: Digi-Key Electronics)

El circuito de la figura 4 puede oscilar potencialmente debido a la carga capacitiva de la CAD y a la inyección de carga de conmutación de la CAD cuando se produce la adquisición inicial. El polo adicional y el cero creados por los componentes de salida del amplificador Rext/Cext aseguran un sistema estable, de modo que la intersección de la curva de ganancia de bucle abierto y cerrado es mayor de 20 dB/década, lo que hace que el margen de fase sea menor de 45°. Esta configuración, con fP2 y fZ2, crea un circuito inestable.

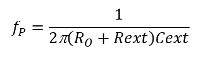

Para prevenir la inestabilidad, cuando se evalúa la curva de ganancia de bucle abierto del amplificador con Rext y Cext en el circuito, los diseñadores necesitan incluir el efecto de la resistencia de salida de bucle abierto del amplificador,RO. La combinación de RO igual a 50 ohmios (W), Rext, y Cext modifican la curva de respuesta de lazo abierto introduciendo un polo (fP, Ecuación 1) y un cero (fZ, Ecuación 2). Los valores RO, Rext y Cext determinan la frecuencia de esquina de fP. Los valores de Rext y Cext determinan la frecuencia de esquina cero, fZ.

Ecuación 1

Ecuación 1

Ecuación 2

Ecuación 2

Los cálculos de fP y fZ son:

fP1 = 842 kHz

fZ1 = 2.95 MHz

con: RO = 50 W

Rext = 20 W

Cext = 2.7 nanofaradios (nF)

fP2 = 22.7 MHz

fZ2 = 79.5 MHz

con: RO = 50 W

Rext = 20 W

Cext = 0.1 nF

Los valores anteriores para fP1 y fZ1 proporcionan un sistema estable para el AD7915 y el ADA4807-1.

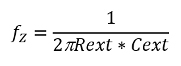

Impulso del ADC SR AD4021 Easy Drive

Una alternativa al AD7915 es el convertidor SAR AD4021 20-bit 1 MSPS Easy Drive. La familia de dispositivos AD4021 reduce enormemente el retroceso de entrada y la corriente de entrada a 0.5 microamperios (?A)/MSPS. El Easy Drive tiene un consumo de energía reducido y una complejidad de la cadena de señales.

La entrada analógica del AD4021 tiene un circuito que reduce el típico retroceso de carga no lineal de la entrada SAR de condensador conmutado. La reducción del retroceso, y una fase de adquisición más larga, permiten el uso de amplificadores con un ancho de banda menor y un conductor de menor potencia (Figura 5).

Figura 5: Los circuitos de entrada y el tiempo de adquisición del AD4021 reducen la corriente de conmutación de retroceso y relajan los estrictos requisitos del amplificador del conductor. (Fuente de la imagen: Analog Devices).

Figura 5: Los circuitos de entrada y el tiempo de adquisición del AD4021 reducen la corriente de conmutación de retroceso y relajan los estrictos requisitos del amplificador del conductor. (Fuente de la imagen: Analog Devices).

La combinación de la reducción del retroceso y el mayor tiempo de adquisición también permite un mayor valor de resistencia Rext en el filtro de resistencia-condensador (RC) de entrada y un correspondiente condensador Cext más pequeño. Esta combinación de una carga de amplificador Cext más pequeña mejora la estabilidad y reduce la disipación de energía.

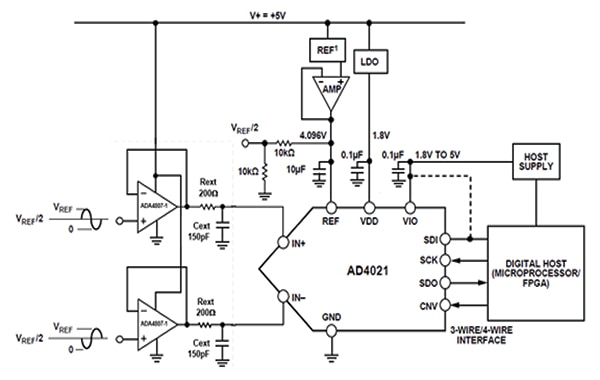

El diagrama de conexión recomendado para el AD4021 usando una sola fuente de 5 voltios parece tener un diagrama de circuito similar. Sin embargo, los requisitos del amplificador se relajan, y los valores de Rext/Cext (R y C) son más pequeños (Figura 6).

Figura 6: Típico diagrama de aplicación del AD4021 y el ADA4807-1 alimentado por una sola fuente de 5 voltios con requisitos de amplificación más relajados y un valor de Rext más grande en comparación con la conducción del AD7915 discutido anteriormente. (Fuente de la imagen: Analog Devices).

Figura 6: Típico diagrama de aplicación del AD4021 y el ADA4807-1 alimentado por una sola fuente de 5 voltios con requisitos de amplificación más relajados y un valor de Rext más grande en comparación con la conducción del AD7915 discutido anteriormente. (Fuente de la imagen: Analog Devices).

En la figura 6, el AD4021 basado en el SAR también utiliza un muestreo de redistribución de carga DAC. El ADC tiene un reloj de conversión integrado y un reloj de serie. Por consiguiente, el proceso de conversión no requiere una entrada de reloj sincrónico (SCK). Esta configuración del reloj permite la prolongación del tiempo de adquisición, lo que mejora la precisión al proporcionar más tiempo para que la señal de entrada se asiente en un valor final.

La principal consideración para el amplificador de accionamiento, tanto para el AD7915 como para el AD4021, es el ruido, ya que la combinación amplificador/Rext/Cext debe asentarse de un paso a escala completa a un nivel de 16 bits (0.0015%, 15 ppm) para el AD7915, y un nivel de 20 bits (0.00001%, 1 ppm) para el AD4021.

Para preservar el rendimiento de la relación señal-ruido (SNR) de los AD7915 y AD4021, el ruido del amplificador del conductor debe ser inferior a un tercio del ruido del ADC. El ruido del AD4021 es de 60 microvoltios rms (mVrms), lo que requiere que la combinación amplificador/Rext/Cext sea inferior a 20 mVrms. El ruido del AD4021 es de 31.5 mVrms, lo que requiere que la combinación amplificador/Rext/Cext sea inferior a 10.5 mVrms.

La herramienta de controladores ADC de precisión de Analog Devices ayuda a los diseñadores a calcular rápidamente los valores correctos de Rext y Cext. Con un piloto seleccionado y un ADC, esta herramienta modela el tiempo de asentamiento del circuito, el ruido y el comportamiento de la distorsión.

Conclusión:

El ADC de la SAR sigue dominando las aplicaciones de adquisición de datos a ultra alta velocidad, control industrial e instrumentación. Sin embargo, los circuitos de entrada externos de estos dispositivos -el amplificador de conducción y el filtro de entrada- requieren una consideración especial para dar cabida a los posibles problemas de inyección de carga de conmutación y de estabilidad del amplificador.

La solución para un control preciso de la señal de entrada para la mayoría de los convertidores SAR, como el AD7916 y el AD4021, está en el controlador de amplificador de operaciones, en este caso el ADA4807-1. Como se muestra, estos dispositivos, apoyados por los valores adecuados de resistencia de salida y condensador, forman una base sólida sobre la que construir un sistema convertidor de SAR de 16 ó 20 bits de alta precisión, resistente y de alta resolución.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.