Conceptos básicos analógicos - Parte 2: ADC Delta-Sigma (ΔƩ) y cómo aprovechar al máximo sus capacidades digitales

Colaboración de Editores de DigiKey de América del Norte

2020-05-14

Nota del editor: Los convertidores analógico-digital (ADC) conectan lo analógico con el mundo digital y por lo tanto son un componente fundamental de cualquier sistema electrónico que se conecta al mundo real. También son un factor determinante del rendimiento de un sistema. Esta serie explora los fundamentos de los CAD, sus diversos tipos y su aplicación. En la Parte 1 de esta serie, se analizaron los principios básicos analógicos de ADC SAR. Aquí, la segunda parte trata de los convertidores delta-sigma (ΔƩ). En la Parte 3, mira los ADC pipeline. Parte 4 muestra cómo los ADC delta-sigma pueden generar resultados de ruido ultra-bajo. En la Parte 5, se examinan las cuestiones difíciles de la conducción de insumos para los países en desarrollo sin litoral.

Como se analizó en la parte 1: Convertidor analógico-digital (ADC) en el registro de aproximación sucesiva (SAR), el desafío de alta precisión de una cadena de señales de un sensor analógico con ganancia múltiple, acondicionamiento de la señal y complejas etapas de filtrado analógico, todas ellas alimentando un SAR-ADC puede dar lugar a errores analógicos. Los diseñadores también pueden terminar con una solución de placa de PC costosa y densamente poblada.

Además, a partir de las señales de los sensores ultrabajos, la salida de cada etapa analógica de la cadena de señales aporta errores que se manifiestan en la salida digital del convertidor como una baja relación señal/ruido (SNR) y altos errores de distorsión. Los diseñadores de tales sistemas necesitan dar un paso atrás y repensar el paradigma del ADC del sensor de alta precisión.

La solución a los problemas asociados con un sistema de sensores de alta precisión es seleccionar una topología ADC que digitalice rápidamente la pequeña señal del sensor e implemente digitalmente las ruidosas funciones analógicas de ganancia y filtrado. Esta es la función del ADC delta-sigma (ΔƩ).

En este artículo se describe brevemente la función fundamental de un ADC ΔƩ y la mecánica de conversión analógica a digital interna utilizando como ejemplo el front-end universal de entrada analógica a digital AD4110-1 de Analog Devices. Desde allí, profundiza en una vista de la cadena de señales circundante y proporciona especificaciones críticas para un sistema de adquisición de datos adecuado.

La estructura de un ADC ΔƩ

Justo antes del cambio de siglo, el ADC ΔƩ captó la atención analógica. Con la adopción generalizada de la tecnología avanzada de ΔƩ, la señal analógica primaria y los procesos de computación comenzaron a residir en el dominio digital. Un examen del circuito integrado (CI) del ADC ΔƩ, muestra que más del 80% de los inmuebles de silicio ejecutan funciones digitales. El subproducto de los circuitos predominantemente digitales es la resistencia y una pequeña huella.

¿Cómo fue posible? Comienza con la digitalización directa de las señales analógicas de bajo voltaje. Una vez en el dominio digital, los circuitos digitales pueden sustituir casi por completo el filtrado analógico y, al mismo tiempo, realizar las funciones de ganancia necesarias (figura 1). Los circuitos digitales también se encogen con cada nodo de proceso de los semiconductores.

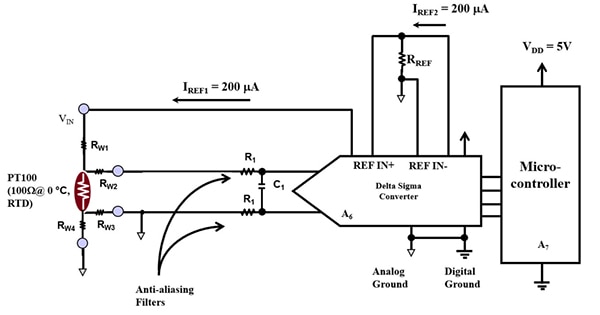

Figura 1: Un ΔƩ contiene casi todos los circuitos necesarios para el filtrado y la ganancia. En este ejemplo, un ADC ΔƩ detecta y digitaliza el voltaje del detector de temperatura de pequeña resistencia (RTD). Luego utiliza la ganancia y el filtrado de la señal digital interna para obtener un resultado digital de 24 bits de bajo ruido. (Fuente de la imagen: A Baker's Dozen)

Figura 1: Un ΔƩ contiene casi todos los circuitos necesarios para el filtrado y la ganancia. En este ejemplo, un ADC ΔƩ detecta y digitaliza el voltaje del detector de temperatura de pequeña resistencia (RTD). Luego utiliza la ganancia y el filtrado de la señal digital interna para obtener un resultado digital de 24 bits de bajo ruido. (Fuente de la imagen: A Baker's Dozen)

En la figura 1, el sistema ADC ΔƩ de 24 bits consiste en una entrada analógica, un motor digital central y un terminal de E/S digital. El convertidor adquiere la señal RTD de bajo voltaje, y a través del filtrado digital, produce una representación digital completa de 24 bits de la entrada analógica. Aquí no existe un bloque de ganancia analógica, normalmente dominante en los circuitos ADC SAR, y el único filtro analógico es la combinación de R1 y C1. Sí, ¡este es un filtro de primer orden simple y barato!

Cómo funciona el ADC ΔƩ

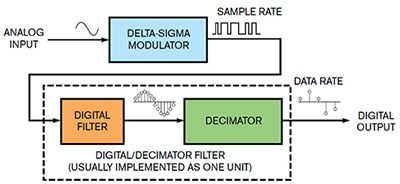

La topología básica de un ADC ΔƩ tiene un modulador ΔƩ en serie con un filtro digital. Más allá de esta topología básica, la mayoría de los ADC ΔƩ tienen una variedad de otras características. Sin embargo, todos los convertidores de ΔƩ poseen este núcleo esencial (Figura 2).

Figura 2: En lo más profundo, cada ADC tiene un modulador ΔƩ, un filtro digital y un decimador. (Fuente de la imagen: EDN)

Figura 2: En lo más profundo, cada ADC tiene un modulador ΔƩ, un filtro digital y un decimador. (Fuente de la imagen: EDN)

En la figura 2, la entrada puede ser sinusoidal o CC; esta discusión se centrará en una entrada sinusoidal. El modulador ΔƩ digitaliza una onda sinusoidal de un solo ciclo a un flujo de 1 bit. La frecuencia de muestra de salida del modulador ΔƩ es Fs. Aunque la conversión del modulador de 1 bit parece tener un alto ruido de cuantificación, el ruido de la señal está en realidad "moldeado" en las frecuencias más altas. Esto allana el camino para una conversión de bajo ruido y alta resolución en la salida del filtro digital.

A la salida del modulador, el filtro digital acumula los resultados de 1 bit del modulador ΔƩ y realiza los cálculos del filtro. La señal de salida del filtro digital refleja digitalmente la señal de entrada analógica mientras continúa con una frecuencia de salida Fs. La señal ahora reside exclusivamente en el dominio digital. Un filtro digital de paso bajo, o filtro de diezmado, atenúa el ruido de alta frecuencia y reduce la tasa de datos de salida, 1/Fd. El filtro digital/decimador toma muestra y filtra el flujo de código de 1 bit del modulador a un código multi-bit más lento.

Mientras que la mayoría de los convertidores solo tienen una frecuencia de muestreo, el convertidor ΔƩ tiene dos: la frecuencia de muestreo de entrada (Fs) y la frecuencia de datos de salida (Fd). La relación de estas dos variables de frecuencia define la relación de diezmo del sistema (DR), según la ecuación 1:

![]() Ecuación 1

Ecuación 1

Modulador ΔƩ

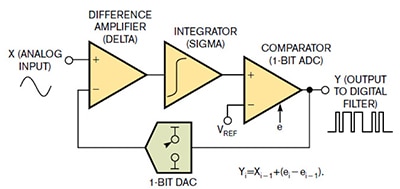

El modulador ΔƩ realiza la conversión real analógica a digital produciendo una corriente de códigos de 1 bit. Este proceso comienza en un amplificador de diferencia (Figura 3).

Figura 3: La etapa de entrada del modulador ADC ΔƩ detecta el delta entre la entrada analógica y el DAC de retroalimentación. La segunda etapa implementa una función integradora o sigma en la señal analógica. (Fuente de la imagen: EDN)

Figura 3: La etapa de entrada del modulador ADC ΔƩ detecta el delta entre la entrada analógica y el DAC de retroalimentación. La segunda etapa implementa una función integradora o sigma en la señal analógica. (Fuente de la imagen: EDN)

En la figura 3, el amplificador diferencial (delta) transmite la señal analógica a un integrador (sigma). A la salida del integrador, un comparador diferencia a una tasa de muestreo muy alta (1/Fs) entre la salida del integrador y una referencia de tensión (VREF). Además, el comparador presenta el flujo de 1 bit al convertidor digital-analógico (DAC) de 1 bit. El modulador mide entonces la diferencia entre la señal de entrada analógica y la salida analógica del DAC de retroalimentación.

El modulador ΔƩ da forma al ruido a frecuencias más altas a través de la acción del integrador y el bucle de retroalimentación del DAC. La fórmula de la Figura 3 (abajo a la derecha) muestra la ecuación de transferencia como Yi = Xi-1 + (ei - ei-1). El modulador digitaliza la señal de entrada (Xi) a un código de salida de 1 bit (Yi) con un ruido de cuantificación (ei). Específicamente, la salida del modulador (Yi) es igual a la entrada (Xi-1) más el ruido de cuantificación (ei - ei-1). La fórmula muestra el ruido de cuantificación como una diferencia entre el error actual (ei) menos el error anterior del modulador (ei-1).

Filtros digitales y de diezmado

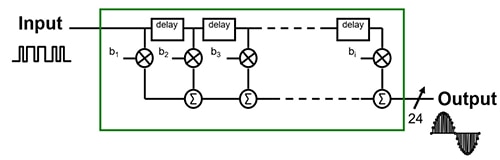

El promedio es una forma de filtrado digital, común en los ADC ΔƩ industriales de baja velocidad. Casi todos los ADC ΔƩ industriales incorporan la clase de filtros de promedio llamados filtros sinc que utilizan un filtro de respuesta de impulso finito (FIR) de fase lineal, que es un filtro digital de paso bajo (Figura 4).

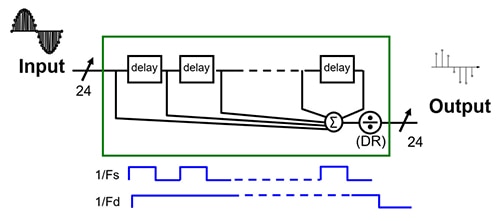

Figura 4: Los coeficientes (bx) en este filtro digital FIR de promedio son todos iguales. (Fuente de la imagen: DigiKey)

Figura 4: Los coeficientes (bx) en este filtro digital FIR de promedio son todos iguales. (Fuente de la imagen: DigiKey)

En la figura 4, el flujo de bits de salida del modulador es la entrada de este filtro digital y el reloj de muestreo del modulador determina el tiempo de retardo. Los coeficientes de la figura 4 (bx) para los filtros FIR son todos iguales a uno. Con este algoritmo de promedio, el filtro digital FIR genera una representación digital de bajo ruido y 24 bits de la entrada analógica de la figura 3, con muestras que se producen a la velocidad de muestreo del modulador (1/Fs). El filtro de diezmado reduce entonces la tasa de datos de salida, usando el DR.

En la literatura, el término "diezmo" se refiere al acto militar de retirar sistemáticamente a los soldados no deseados. El diezmado en la electrónica digital utiliza el mismo concepto para reducir la tasa de datos de salida de la señal digital (1/Fd) por la DR. La manera rápida y digital de hacerlo es desechar sistemáticamente algunas de las muestras de salida del filtro digital (Figura 5).

Figura 5: El proceso de diezmado reduce sistemáticamente el número de salidas digitales de 24 bits por un factor de la tasa de datos de salida (1/Fd, en la parte inferior de la imagen) dividido por la tasa de muestreo (1/Fs). (Fuente de la imagen: DigiKey)

Figura 5: El proceso de diezmado reduce sistemáticamente el número de salidas digitales de 24 bits por un factor de la tasa de datos de salida (1/Fd, en la parte inferior de la imagen) dividido por la tasa de muestreo (1/Fs). (Fuente de la imagen: DigiKey)

El proceso de diezmado de la figura 5 diezma la tasa de datos de salida (1/Fd) por la RD, según la ecuación 1.

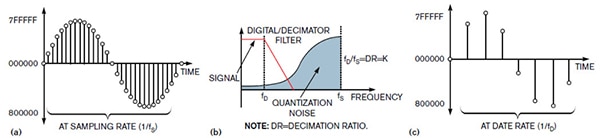

Los eventos a través del filtro digital y de diezmado reducen efectivamente el ruido de ADC ΔƩ (Figura 6).

Figura 6: Aquí se muestra la salida del filtro digital (a) en el dominio del tiempo; la salida en forma de ruido del modulador superpuesta a la función de paso bajo del filtro de diezmado (b); y la señal de salida del decimador en el dominio del tiempo (c). (Fuente de la imagen: EDN)

Figura 6: Aquí se muestra la salida del filtro digital (a) en el dominio del tiempo; la salida en forma de ruido del modulador superpuesta a la función de paso bajo del filtro de diezmado (b); y la señal de salida del decimador en el dominio del tiempo (c). (Fuente de la imagen: EDN)

La figura 6 muestra la señal digital a medida que viaja a través del filtro digital/decimal. La salida de 24 bits del filtro digital (figura 6(a)) funciona a la misma velocidad que la tasa de muestreo del modulador (1/Fs). El modulador ya ha dado forma al ruido de cuantificación en frecuencias más altas (Figura 6(b)), por lo que el filtro digital/decimación captura la porción de frecuencia más baja de la señal de salida. La salida del filtro de diezmado (Figura 6(c)) produce una representación digital de menor frecuencia de la señal analógica original.

Expansión digital

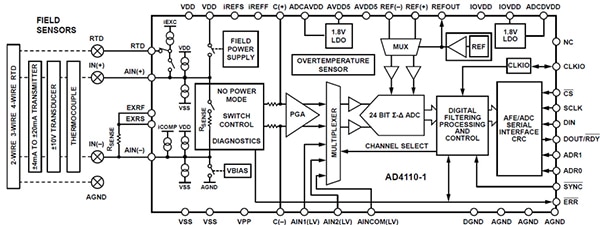

El ADC ΔƩ reside principalmente en el dominio digital. Ahora se pueden añadir fácilmente etapas de ganancia programables digitalmente, fuentes de corriente, indicadores de señales de entrada de circuito corto o abierto y varias interfaces de salida en serie (Figura 7).

Figura 7: El AD4110-1 de Analog Devices proporciona múltiples funciones de front-end analógico para sistemas de control de procesos industriales. (Fuente de la imagen: Analog Devices)

Figura 7: El AD4110-1 de Analog Devices proporciona múltiples funciones de front-end analógico para sistemas de control de procesos industriales. (Fuente de la imagen: Analog Devices)

La figura 7 muestra que el ADC ΔƩ AD4110-1 de Analog Devices tiene numerosas mejoras digitales, incluyendo terminales de entrada programables, funciones de diagnóstico y velocidades de datos flexibles. Las interfaces de los sensores de entrada incluyen RTD y sensores de temperatura de termopar.

El AD4110-1 tiene el núcleo básico de un ADC ΔƩ, pero el énfasis digital del dispositivo permite una serie de funciones habilitadas digitalmente hasta el punto de que el AD4110-1 es ahora un front-end analógico universal (AFE).

Al igual que un ADC ΔƩ estándar, el AD4110-1 es capaz de digitalizar voltajes extremadamente bajos de termopares, RTD y puentes. Mientras que estas funciones a menudo requieren circuitos de excitación adicionales, el AD4110-1 los tiene integrados en la placa.

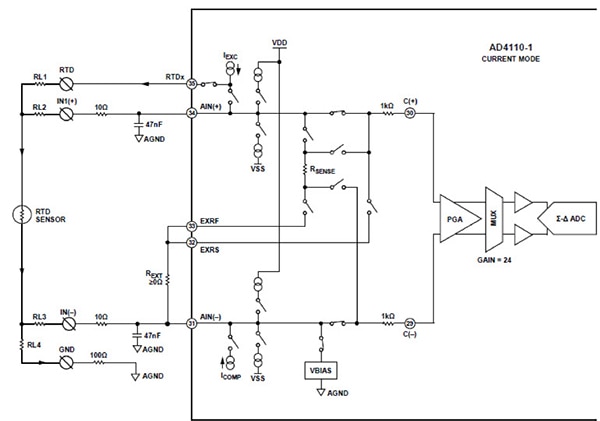

Por ejemplo, el RTD requiere una fuente de corriente de precisión que sea ratiométrica a la referencia de voltaje del convertidor (Figura 8).

Figura 8: Conexiones de cable apropiadas para un RTD de cuatro hilos y el ADC ΔƩ AD4110-1. La corriente de excitación RTD es programable en seis niveles entre 0.1 miliamperios (mA) y 1 mA. (Fuente de la imagen: Analog Devices)

Figura 8: Conexiones de cable apropiadas para un RTD de cuatro hilos y el ADC ΔƩ AD4110-1. La corriente de excitación RTD es programable en seis niveles entre 0.1 miliamperios (mA) y 1 mA. (Fuente de la imagen: Analog Devices)

En la figura 8, el AD4110-1 incluye una corriente de excitación que puede ser programada a seis niveles entre 0.1 mA y 1 mA usando el registro PGA_RTD_CTRL del convertidor. La corriente de excitación de la resistencia RTD es del pin 35. El convertidor detecta la caída de voltaje a través del RTD por medio de las clavijas 34 y 31 de las entradas de alta impedancia. El amplificador de ganancia programable (PGA) AD4110-1 ofrece 16 ganancias programables de 0.2 a 24 voltios. Con esta característica, el diseñador puede complementar aún más el sensor de entrada al rango de entrada del AD4110-1. Otras capacidades auxiliares son las corrientes de tracción/tiro para detectar la presencia de un cable abierto (útil con los termopares), la calibración de la ganancia y los coeficientes de corrección.

Conclusión

El ADC ΔƩ elimina los complejos circuitos analógicos de entrada y proporciona una señal de salida digital de alta resolución y bajo ruido promediado digitalmente utilizando un modulador de entrada, un filtro digital FIR y un filtro de diezmado. Como gran parte de los circuitos están en forma digital, pueden escalarse fácilmente con nodos de proceso digital avanzados, y se puede añadir más funcionalidad manteniendo una huella pequeña y una complejidad reducida de la placa.

El ADC ΔƩ AD4110-1 de Analog Devices aprovecha las características de esta arquitectura de ADC. El AD4110-1 tiene el núcleo básico de un ADC ΔƩ, pero el énfasis digital del dispositivo permite una serie de funciones digitales hasta el punto de que el AD4110-1 es ahora un AFE universal y verdaderamente listo para RTD y termopar.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.