Implementación de generadores de reloj programables de alto rendimiento para centros de datos y sistemas industriales

La sincronización precisa para admitir comunicaciones Ethernet e interconexión de componentes periféricos exprés (PCIe) es importante y puede ser un desafío cuando se diseñan servidores, sistemas de almacenamiento y redes o sistemas industriales integrados. No se trata solo de agregar un bus Ethernet o PCIe. Un diseño típico puede tener varios buses. Todos necesitan una compatibilidad de temporizador preciso con un mínimo de fluctuación. Un sistema típico requiere una combinación de buses de comunicaciones que operan en varias frecuencias hasta 650 MHz (megahercios).

Usted necesita soluciones que ocupen el menor espacio posible en la placa de CI (circuito impreso). Además, las necesidades de sincronización de Ethernet y PCIe difieren, lo que aumenta el desafío del diseño. Para abordar estas demandas, puede recurrir a CI generadores de reloj programables compactos que pueden entregar simultáneamente hasta 12 relojes de referencia para buses Ethernet y PCIe.

En este blog se revisan brevemente algunas de las necesidades de temporización de los buses Ethernet y PCIe, y se presentan soluciones de generadores de reloj programables compactos de Renesas que usted puede usar y que son compatibles simultáneamente con las necesidades de múltiples buses PCIe y Ethernet. También se presentan placas de evaluación para acelerar el desarrollo de circuitos de temporización en servidores, sistemas de almacenamiento y redes o sistemas industriales integrados.

Control de la fluctuación y minimización de EMI (interferencia electromagnética)

PCIe y Ethernet se utilizan para diferentes propósitos. Las aplicaciones PCIe incluyen comunicaciones de chip a chip en una placa de CI y conexiones a tarjetas de expansión, mientras que Ethernet se usa para LAN (redes de área local), SAN (redes de área de almacenamiento) y aplicaciones similares. Los diferentes entornos operativos imponen diferentes demandas a los circuitos de temporización.

La atenuación de la fluctuación es de vital importancia en las redes Ethernet. Por ejemplo, en Ethernet de alta velocidad de hasta 650 megahercios (MHz), la fluctuación de fase de RMS (raíz cuadrada media) debe limitarse a 150 fs (femtosegundos) como máximo para garantizar la integridad de la señal, la reducción de los retrasos de propagación y un comportamiento predecible.

Además de controlar la fluctuación, los buses PCIe se benefician del uso de modulación de espectro ensanchado que distribuye la energía de la fluctuación en un rango más amplio de frecuencias, lo que minimiza la EMI (interferencia electromagnética). El control de EMI significa una menor necesidad de blindaje en las placas de CI, lo que reduce los costos del sistema y acelera la integración del sistema. Los generadores VersaClock de Renesas le permiten controlar la cantidad de modulación de espectro ensanchado para optimizar las compensaciones costo-rendimiento requeridas por aplicaciones específicas.

Haga más en menos espacio

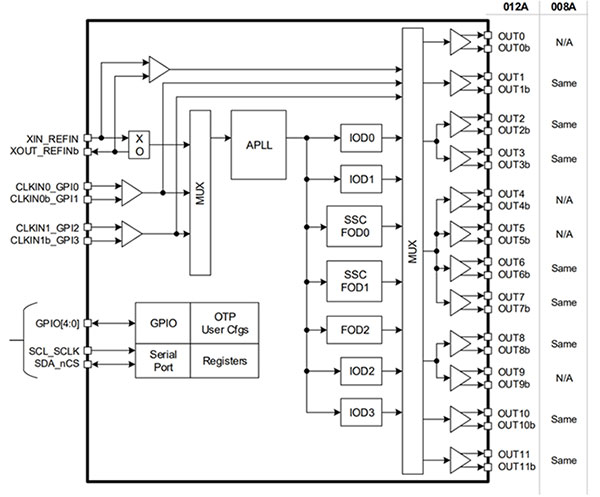

Una solución de temporizador integrado basado en los generadores VersaClock de Renesas le permite hacer más en menos espacio en la placa de CI. Están disponibles con 8 o 12 relojes independientes y cuentan con las siguientes características (Figura 1):

- Fluctuación de fase de 169 fs RMS (10 kHz [kilohercios] – 20 MHz, 156.25 MHz)

- Reloj común PCIe Gen6 (CC) 27 fs RMS

- Compatibilidad con la operación de SRIS (expansión independiente de referencia separada) y de SRNS (referencia separada sin expansión) de PCIe

- Salidas de LVDS (tecnología de señal diferencial de bajo voltaje) de 1 kHz a 650 MHz y LP-HCSL (lógica de dirección de corriente de alta velocidad y baja potencia)

Figura 1: Hay generadores de reloj programables VersaClock disponibles que admiten hasta ocho relojes (columna '008A' a la derecha) o hasta 12 relojes (columna '012A'). (Fuente de imagen: Renesas)

Figura 1: Hay generadores de reloj programables VersaClock disponibles que admiten hasta ocho relojes (columna '008A' a la derecha) o hasta 12 relojes (columna '012A'). (Fuente de imagen: Renesas)

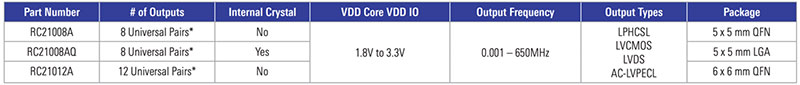

Un enfoque tradicional para construir una solución de temporización con cinco relojes independientes requiere un circuito de oscilador de cristal común que ocupe aproximadamente 3 x 3 mm (milímetros) de espacio en la placa más cuatro subosciladores, cada uno de los cuales ocupa aproximadamente 5 x 3 mm. O puede usar un único CI VersaClock, como el RC21008A, que ocupa apenas 5 x 5 mm. Y ese mismo CI puede admitir hasta ocho salidas de reloj, lo que reduce aún más el espacio de la placa, el número de componentes y el costo. Se muestran las características clave del RC21008A, junto con otros dos CI de la familia VersaClock 7: el RC21008AQ y el RC21012A (Tabla 1).

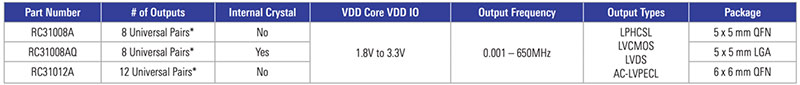

Tabla 1: Se muestran las características clave de tres generadores de reloj de la familia VersaClock 7; “*” indica que las salidas son configurables a diferencial o LVCMOS. (Fuente de la tabla: Renesas)

Tabla 1: Se muestran las características clave de tres generadores de reloj de la familia VersaClock 7; “*” indica que las salidas son configurables a diferencial o LVCMOS. (Fuente de la tabla: Renesas)

Atenuación de la fluctuación

Los atenuadores de fluctuación programables RC31008A, RC31008AQ y RC31012A tienen capacidades de sincronización de red, incluido JEDEC JESD204B/C para compatibilidad de sincronización de convertidor en salidas diferenciales o asimétricas con acoplamiento de CA o CC, y soporte para SyncE (Ethernet sincrónica) para sincronización basada en red. Al igual que los CI generadores de reloj VersaClock, estos atenuadores de fluctuación están disponibles con 8 o 12 salidas, lo que reduce el tamaño y el costo de la solución (Tabla 2).

Tabla 2: Atenuadores de fluctuación de la familia VersaClock 7, “*” indica el número de salidas configurables a diferencial o LVCMOS. (Datos de la tabla: Renesas)

Tabla 2: Atenuadores de fluctuación de la familia VersaClock 7, “*” indica el número de salidas configurables a diferencial o LVCMOS. (Datos de la tabla: Renesas)

Placas de evaluación

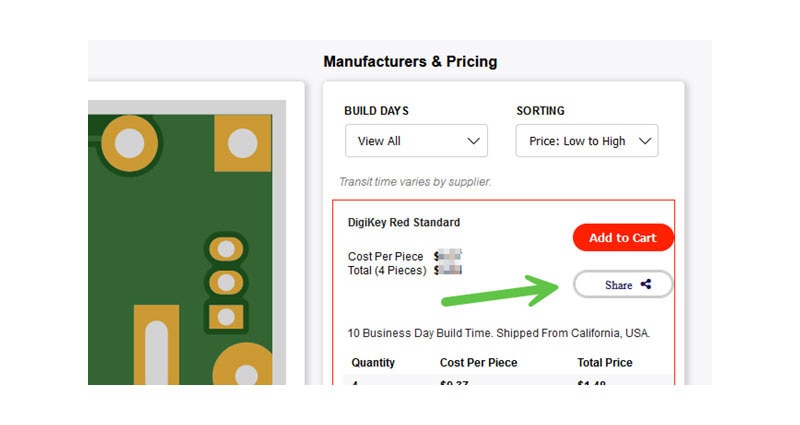

Para acelerar sus actividades de desarrollo, Renesas ofrece una variedad de EVB (placas de evaluación), que incluyen RC21008-EVB (Figura 2) y RC21012-EVB, para diseños de generador de reloj de 8 y 12 salidas, respectivamente, y las placas de evaluación RC31008-EVB y RC31012-EVB que se pueden utilizar para atenuadores de fluctuación de 8 y 12 salidas, respectivamente. Estas EVB pueden admitir el generador de reloj en modo sintetizador para el cumplimiento de PCIe y el rendimiento de espectro ensanchado, y también pueden admitir el modo de atenuación de fluctuación. Soportan rangos de frecuencia de la entrada de referencia de 1 kHz a 650 MHz en modo diferencial y de 1 kHz a 200 MHz en modo de salida asimétrica. Cuentan con una disipación de potencia típica de menos de 1 vatio con especificaciones de fluctuación de:

- Fluctuación de fase de 150 fs RMS (12 kHz–20 MHz, entero)

- Fluctuación de fase de 200 fs RMS (12 kHz–20 MHz, fracción)

Figura 2: Las EVB, como el RC21008-EVB de la serie VersaClock 7, admiten el desarrollo de ocho soluciones de salida. (Fuente de imagen: Renesas)

Figura 2: Las EVB, como el RC21008-EVB de la serie VersaClock 7, admiten el desarrollo de ocho soluciones de salida. (Fuente de imagen: Renesas)

Conclusión

Como se muestra, los generadores de reloj VersaClock y los atenuadores de fluctuaciones de Renesas se pueden utilizar para desarrollar soluciones de temporización de bajo costo, compactas y de alto rendimiento para buses PCIe y Ethernet en una variedad de aplicaciones industriales y de procesamiento de datos. Para ayudarlo a comenzar, las EVB están disponibles para acelerar el proceso de desarrollo y acortar el tiempo de comercialización.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum