Fundamentos de los FPGA - Parte 4: Introducción de los FPGA de Xilinx

Colaboración de Editores de DigiKey de América del Norte

2020-04-01

Nota del editor: Las soluciones de procesamiento óptimas suelen ser proporcionadas por combinaciones de RISC, CISC, procesadores gráficos y FPGA; FPGA por sí mismas; o por FPGA que cuentan con núcleos de procesador duro como parte de su tejido. Sin embargo, muchos diseñadores no están familiarizados con las capacidades de los FPGA, cómo han evolucionado y cómo usarlos.La Parte 1 de esta serie de varias partes proporciona una introducción de alto nivel a los FPGA; la Parte 2 se centró en las ofertas de FPGA de Lattice Semiconductor; y la Parte 3 se concentró en las familias de dispositivos FPGA y las herramientas de diseño de Microchip Technology (de su filial Microsemi Corporation). Aquí, en la cuarta parte, se discuten los componentes y herramientas de Xilinx. En la Parte 5 se considerarán las ofertas de Altera.

Como se expuso en la primera parte, los arreglo de compuerta programable en campo (FPGA) tienen muchas características que los convierten en un activo informático inestimable, ya sea utilizados de forma autónoma o en una arquitectura heterogénea, pero muchos diseñadores no están familiarizados con los FPGA ni con la forma de incorporar estos dispositivos en sus diseños.

Una forma de superar este impedimento es mirar más profundamente las arquitecturas FPGA y las herramientas asociadas de los principales proveedores; este artículo examina la línea de Xilinx.

Descripción general de las opciones de FPGA de alto nivel

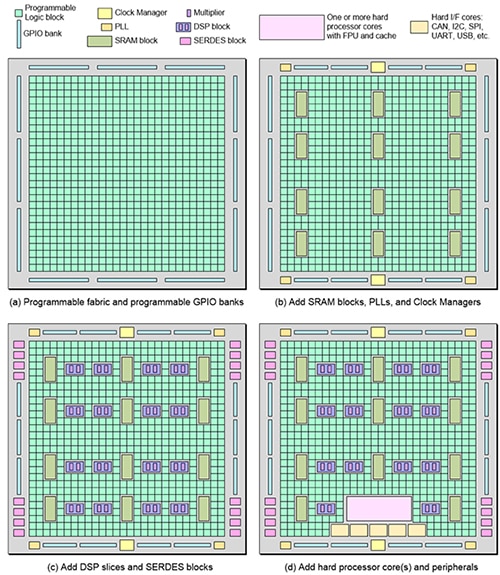

Existen muchos tipos diferentes de FPGA en el mercado, cada uno con diferentes combinaciones de capacidades y funciones. En el corazón de cualquier FPGA está su tejido programable. Esto se presenta como un conjunto de bloques lógicos programables, también conocidos como elementos lógicos (LE) (Figura 1a). El siguiente paso en el tejido del FPGA es incluir cosas como bloques de SRAM, llamados bloque RAM (BRAM), bucles de bloqueo de fase (PLL) y gestores de reloj (Figura 1b). También se pueden añadir bloques de procesamiento de señales digitales (DSP) (llamados partes DSP) y bloques de serializador/deserializador de alta velocidad (SERDES) (Figura 1c).

Figura 1: Los FPGA más simples contienen sólo tejido programable e IO de propósito general configurable (GPIO) (a); las diferentes arquitecturas aumentan este tejido fundamental con bloques SRAM, PLL y gestores de reloj (b); bloques DSP e interfaces SERDES (c); y núcleos de procesador duro y periféricos (d). (Fuente de la imagen: Max Maxfield)

Figura 1: Los FPGA más simples contienen sólo tejido programable e IO de propósito general configurable (GPIO) (a); las diferentes arquitecturas aumentan este tejido fundamental con bloques SRAM, PLL y gestores de reloj (b); bloques DSP e interfaces SERDES (c); y núcleos de procesador duro y periféricos (d). (Fuente de la imagen: Max Maxfield)

Las funciones de la interfaz periférica como CAN, I2C, SPI, UART y USB se pueden implementar como núcleos flexibles en la estructura programable, pero muchos FPGA las incluyen como núcleos rígidos en el silicio. Del mismo modo, los microprocesadores pueden implementarse como núcleos flexibles en la estructura programable o como núcleos rígidos en el silicio (Figura 1d). Los FPGA con núcleos de procesador duro se denominan FPGA de sistema en chip (SoC). Diferentes FPGA ofrecen distintos conjuntos de funciones, características y capacidades dirigidas a diferentes mercados y aplicaciones.

Hay varios proveedores de FPGA, entre ellos Altera (que fue adquirida por Intel), Atmel (que fue adquirida por Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (que también fue adquirida por Microchip Technology) y Xilinx.

Todos estos proveedores ofrecen múltiples familias de FPGA; algunos ofrecen FPGA de SoC, algunos ofrecen dispositivos dirigidos a aplicaciones de inteligencia artificial (AI) y aprendizaje automático (ML), y algunos ofrecen dispositivos tolerantes a la radiación dirigidos a entornos de alta radiación como el espacio. Elegir el mejor dispositivo para la tarea en cuestión puede ser complicado porque existen muchas familias y cada una de ellas ofrece diferentes recursos.

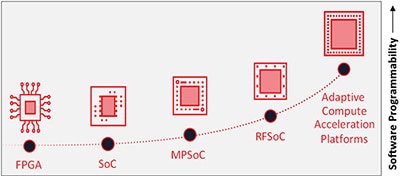

Introducción a FPGA, SoC, MPSoC, RFSoC y ACAP de Xilinx

El rendimiento y las capacidades de los dispositivos programables de Xilinx van desde modestas a extremadamente altas. Desde los FPGA tradicionales, a los SoC (tejido programable FPGA con un solo procesador de núcleo duro), MPSoC (tejido programable FPGA con múltiples procesadores de núcleo duro), RFSoC (MPSoC con capacidad de RF) y ACAP (plataformas de aceleración de cómputo adaptativo) (Figura 2).

Figura 2: Con el tiempo, la cartera arquitectónica de Xilinx ha evolucionado desde simples FPGA que contienen solo tejido programable, a dispositivos SoC en los que el tejido programable se aumenta con un procesador de núcleo duro, a MPSoC con múltiples procesadores, a RFSoC con capacidades de RF, a la última generación de ACAP, que están dirigidos a aplicaciones como la IA. (Fuente de la imagen: Max Maxfield)

Figura 2: Con el tiempo, la cartera arquitectónica de Xilinx ha evolucionado desde simples FPGA que contienen solo tejido programable, a dispositivos SoC en los que el tejido programable se aumenta con un procesador de núcleo duro, a MPSoC con múltiples procesadores, a RFSoC con capacidades de RF, a la última generación de ACAP, que están dirigidos a aplicaciones como la IA. (Fuente de la imagen: Max Maxfield)

Xilinx tiene un cartera de productos tan extenso, se dirige a tantos segmentos de mercado y proporciona una gama tan amplia de métodos de implementación que puede ser un reto para alguien que es nuevo en los FPGA entender el "panorama general".

En el caso de los mercados a los que Xilinx se dirige, pero no se limita a, centros de datos (computación, red, almacenamiento); comunicaciones (alámbricas, inalámbricas); aeroespacial y de defensa; industrial, científico y médico (ISM); prueba, medición y emulación (TME); y automotriz, radiodifusión y consumo.

En el caso de los métodos de implementación, estos incluyen lo que Xilinx llama Dispositivos adaptables de hardware, que incluyen chips, tarjetas de evaluación y kits de desarrollo; Sistemas finales desplegables, que incluyen sistema en módulos (SoM) y tarjetas aceleradoras PCIe; y FPGA como un servicio (FAAS), que incluye la evaluación y el aprovechamiento de las tecnologías de Xilinx a través de los principales proveedores de nube, incluyendo Amazon Web Services (AWS), Alibaba.com y Nimbix.net

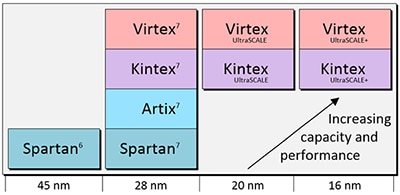

Con respecto a las ofertas de FPGA de Xilinx, una forma de categorizarlas es por el nodo de tecnología de procesos (Figura 3).

Figura 3: Las ofertas de FPGA de Xilinx proporcionan un cartera completa de múltiples nodos para abordar los requerimientos a través de un amplio conjunto de aplicaciones. (Fuente de la imagen: Max Maxfield)

Figura 3: Las ofertas de FPGA de Xilinx proporcionan un cartera completa de múltiples nodos para abordar los requerimientos a través de un amplio conjunto de aplicaciones. (Fuente de la imagen: Max Maxfield)

Según la aplicación de que se trate, los diseñadores pueden optar por una FPGA de bajo costo y pequeña huella implementada en un nodo tecnológico anterior, o en el caso de una aplicación de red de última generación, por ejemplo, elegir un dispositivo de alta capacidad, gran ancho de banda y alto rendimiento implementado en un nodo tecnológico más reciente.

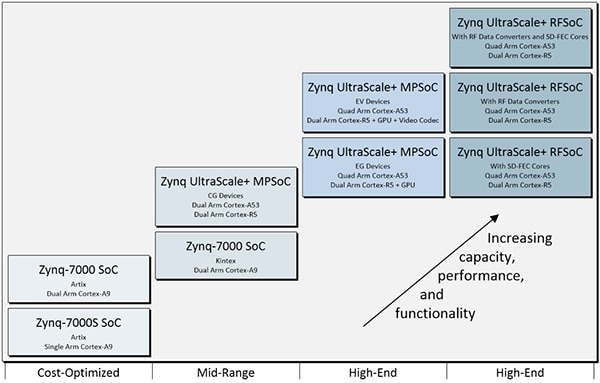

En el caso de diseños que requieren uno o más núcleos de procesador duro (y otras funciones endurecidas como GPU, códecs y núcleos de decisión suave, corrección de errores hacia adelante (SD-FEC)), Xilinx ofrece una cartera de dispositivos bajo el nombre general de Zynq. En la Figura 4 se muestra un resumen de las ofertas de Zynq SoC, MPSoC y RFSoC. Este conjunto de soluciones proporciona a los diseñadores una amplia gama de capacidades para facilitar la optimización de la potencia, el rendimiento, el costo y el tiempo de comercialización.

Figura 4: Las ofertas de SoC, MPSoC y RFSoC de Xilinx integran la programabilidad de software de un procesador con la programabilidad de hardware de una FPGA, proporcionando a los diseñadores el rendimiento, la flexibilidad y la escalabilidad del sistema. (Fuente de la imagen: Max Maxfield)

Figura 4: Las ofertas de SoC, MPSoC y RFSoC de Xilinx integran la programabilidad de software de un procesador con la programabilidad de hardware de una FPGA, proporcionando a los diseñadores el rendimiento, la flexibilidad y la escalabilidad del sistema. (Fuente de la imagen: Max Maxfield)

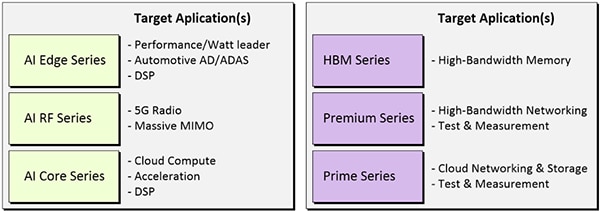

Las ofertas más recientes de Xilinx son los dispositivos de la Plataforma de aceleración computacional adaptable Versal (ACAP), todos ellos implementados en el nodo de tecnología de procesos de 7 nanómetros (nm). Los ACAP son plataformas de computación multinúcleo altamente integradas que pueden adaptarse a diversos algoritmos en evolución. Son dinámicamente personalizables a nivel de hardware y software para adaptarse a una amplia gama de aplicaciones y cargas de trabajo. Diseñados alrededor de una red programable en un chip (NoC), los ACAP son fácilmente programados por diseñadores de hardware y desarrolladores de software por igual.

Las nuevas características de los dispositivos Versal incluyen motores inteligentes (un conjunto masivo de procesadores vectoriales para cargas de trabajo ML y DSP); un NoC programable de gran ancho de banda, baja latencia y baja potencia que puede mover terabytes de datos; y un armazón integrado que proporciona un mejor rendimiento, utilización y productividad con una infraestructura básica preconstruida y conectividad de sistema.

En la figura 5 se muestra una visión general de la cartera de Versal ACAP.

Figura 5: Los ACAP Versal de Xilinx son plataformas de computación multinúcleo altamente integradas que pueden adaptarse a diversos algoritmos en evolución. Los ACAP son dinámicamente personalizables a nivel de hardware y software para adaptarse a una amplia gama de aplicaciones y cargas de trabajo. (Fuente de la imagen: Max Maxfield)

Figura 5: Los ACAP Versal de Xilinx son plataformas de computación multinúcleo altamente integradas que pueden adaptarse a diversos algoritmos en evolución. Los ACAP son dinámicamente personalizables a nivel de hardware y software para adaptarse a una amplia gama de aplicaciones y cargas de trabajo. (Fuente de la imagen: Max Maxfield)

Como se discutirá en la sección de herramientas de diseño, un diferenciador clave asociado con los dispositivos Versal es una nueva pila de software que está dirigida a científicos e ingenieros de software, así como a ingenieros de diseño de hardware tradicional.

Hay un sinnúmero de dispositivos Xilinx disponibles. Algunas ofertas representativas serían un Artix-7 FPGA, un Kintex UltraScale FPGA, un Kintex UltraScale+ FPGA, un módulo SoC Zynq-7000 de Trenz Electronic GmbH y un Zynq UltraScale+ MPSoC.

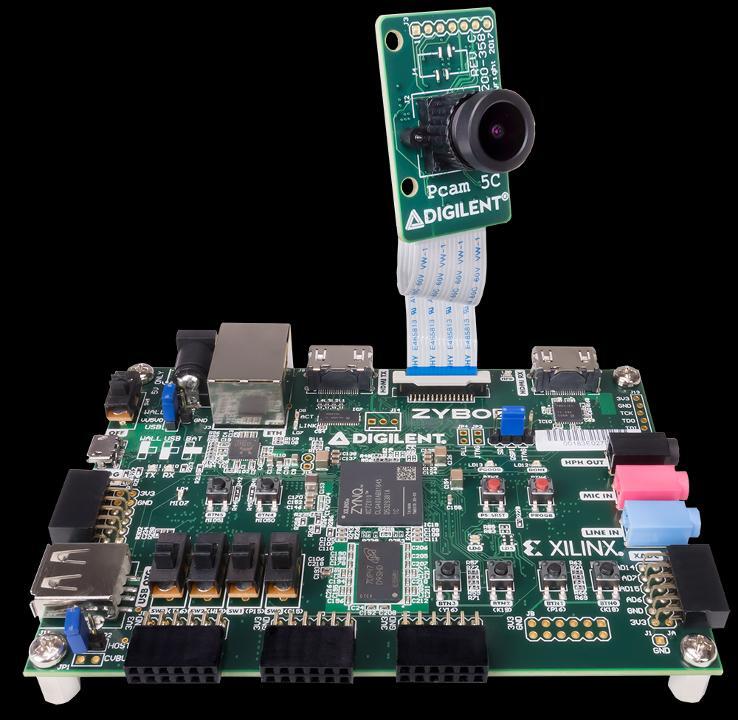

Asimismo, existe una amplia variedad de placas de evaluación y desarrollo. Algunas ofertas representativas serían una placa de evaluación de FPGA Artix-7 de Digilent, una placa de evaluación de FPGA Kintex UltraScale de Analog Devices, una placa de evaluación de FPGA Kintex UltraScale+ de Xilinx, una placa de evaluación de FPGA Zynq-7000 SoC de Digilent, y una placa de evaluación de FPGA Zynq UltraScale+ MPSoC, también de Xilinx.

Diseño y desarrollo con FPGA, SoC y ACAP de Xilinx

Un área en la que Xilinx realmente se diferencia de la competencia es en la amplitud y la profundidad de sus herramientas de diseño y flujos.

En la primera parte de esta serie sobre los FPGA, observamos que la forma tradicional de diseñar estos dispositivos es que los ingenieros utilicen un lenguaje de descripción de hardware (HDL), como Verilog o VHDL para captar la intención del diseño a un nivel de abstracción conocido como nivel de transferencia de registros (RTL). Estas descripciones RTL pueden ser simuladas primero para verificar que funcionan como se requiere, después de lo cual se pasan a una herramienta de síntesis que genera el archivo de configuración utilizado para programar el FPGA.

El siguiente paso en la abstracción es capturar la intención del diseño usando un lenguaje de programación como C/C++, o una implementación especial como SystemC, que es un conjunto de clases y macros de C++ que proporcionan una interfaz de simulación dirigida por eventos. Estos facilitan la simulación de procesos concurrentes, cada uno de los cuales se describe utilizando una sintaxis sencilla de C++. Tales descripciones pueden ser analizadas y perfiladas ejecutándolas como programas regulares, después de lo cual se pasan a un motor de síntesis de alto nivel (HLS), que produce RTL que se alimenta en el motor de síntesis regular.

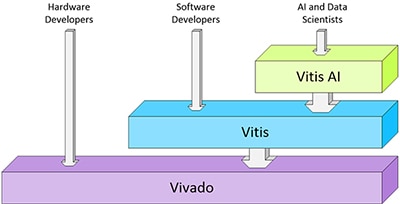

Toda esta funcionalidad es adoptada por las Ediciones HLx de Vivado Design Suite, cuya salida es el flujo de bits de configuración que será cargado en los dispositivos FPGA, SoC, MPSoC, RFSoC o ACAP. Además de permitir que los desarrolladores de hardware aprovechen el diseño basado en C y la reutilización optimizada, Vivado también proporciona la reutilización del subsistema IP, la automatización de la integración y el cierre acelerado del diseño (Figura 6).

Figura 6: Una vista de alto nivel de la pila de herramientas de diseño de Xilinx Vivado y Vitis refleja cómo los usuarios pueden trabajar con las herramientas en los niveles de abstracción más apropiados. Los diseñadores de hardware trabajan con Vivado, los desarrolladores de software trabajan con Vitis, y los científicos de datos y de la IA trabajan con Vitis AI. (Fuente de la imagen: Max Maxfield)

Figura 6: Una vista de alto nivel de la pila de herramientas de diseño de Xilinx Vivado y Vitis refleja cómo los usuarios pueden trabajar con las herramientas en los niveles de abstracción más apropiados. Los diseñadores de hardware trabajan con Vivado, los desarrolladores de software trabajan con Vitis, y los científicos de datos y de la IA trabajan con Vitis AI. (Fuente de la imagen: Max Maxfield)

El siguiente nivel de abstracción se basa en la Plataforma de software unificada Vitis, que proporciona a los desarrolladores de software la capacidad de construir sin problemas aplicaciones aceleradas. Conceptualmente "sentado en la cima" de Vitis es Vitis AI, que permite a la IA y a los científicos de datos trabajar al nivel de abstracción de TensorFlow. Vitis AI es una plataforma de desarrollo para la inferencia de la IA en plataformas de hardware Xilinx, incluyendo tanto los dispositivos de borde como las tarjetas PCIe de Alveo. Consiste en IP optimizada, herramientas, librerías, modelos y diseños de ejemplo, y está diseñada para explotar todo el potencial de aceleración de la IA en los dispositivos FPGA y ACAP de Xilinx.

La IA de Vitis alimenta a Vitis, que a su vez alimenta a Vivado. La clave de la figura 6 es que los usuarios solo "ven" lo que necesitan "ver". Es decir, los desarrolladores de hardware solo "verán" a Vivado, los desarrolladores de software solo "verán" a Vitis, y los científicos de la IA y de los datos solo "verán" a Vitis IA. De esta manera, los usuarios pueden trabajar con las herramientas en los niveles de abstracción más apropiados.

Proporcionar a los desarrolladores de software un conjunto de herramientas como Vitis, que los aísla del hardware subyacente, abre los FPGA a un grupo mucho más grande de desarrolladores. De manera similar, el hecho de proporcionar a los científicos de la IA y de los datos un conjunto de herramientas como Vitis AI, que les permite centrarse en su propio nivel de abstracción y los aísla del software subyacente, abre una vez más los FPGA a una nueva clase de desarrolladores.

Al proporcionar estas capacidades, Xilinx está a la vanguardia de un impulso en toda la industria para elevar las herramientas FPGA a niveles cada vez más altos de abstracción de diseño que permitirán a los desarrolladores aprovechar más fácilmente las capacidades de estos dispositivos e integrarlas en sus próximos diseños.

Conclusión

Las soluciones óptimas de diseño de procesamiento a menudo son proporcionadas por combinaciones de procesadores y FPGA, por FPGA por sí solos o por FPGA que cuentan con núcleos de procesadores duros como parte de su tejido. Como tecnología, los FPGA han evolucionado rápidamente a lo largo de los años y son capaces de hacer frente a muchos requisitos de diseño en términos de flexibilidad, velocidad de procesamiento y potencia, lo que las hace muy útiles para una amplia gama de aplicaciones, desde interfaces inteligentes hasta visión artificial e inteligencia artificial.

Como se muestra, la oferta de dispositivos programables de Xilinx va desde modestos a extremadamente altos en términos de rendimiento y capacidades. Van desde los FPGA tradicionales, a los SoC (tejido programable FPGA con un solo procesador de núcleo duro), MPSoC (tejido programable FPGA con múltiples procesadores de núcleo duro), RFSoC (MPSoC con capacidad de RF), y ACAP (plataformas de aceleración de cómputo adaptativo).

Para ayudar a los diseñadores a crear diseños con estos dispositivos, Xilinx ofrece un conjunto de herramientas para atender las necesidades de los desarrolladores de hardware (Vivado), los desarrolladores de software (Vitis) y los científicos de la IA y los datos (Vitis AI).

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.