Incorpore RISC-V a su curso de Arquitectura de Computadoras usando RVfpga

Estimados profesores y amigos:

Los medios virtuales son convenientes y nos salvaron durante la pandemia, pero no se comparan con las clases presenciales. Me refiero a esa sensación inmersiva de la experiencia práctica y la misión compartida con colegas que intentan dominar el mismo tema.

Ahora estamos en plena serie global de talleres para "capacitar a los profesores" sobre cómo usar RISC-V en cursos de arquitectura de computadoras y el diseño de SoC (sistemas en chip). Empezamos en EE. UU. el año pasado y también participamos en varios eventos de Europa. Entre ellos cabe destacar el taller de diciembre en Silicon Valley, al que asistieron casi 60 profesores y formadores.

Próximamente, nos dirigiremos al este: Israel, Japón, Taiwán, Corea y China.

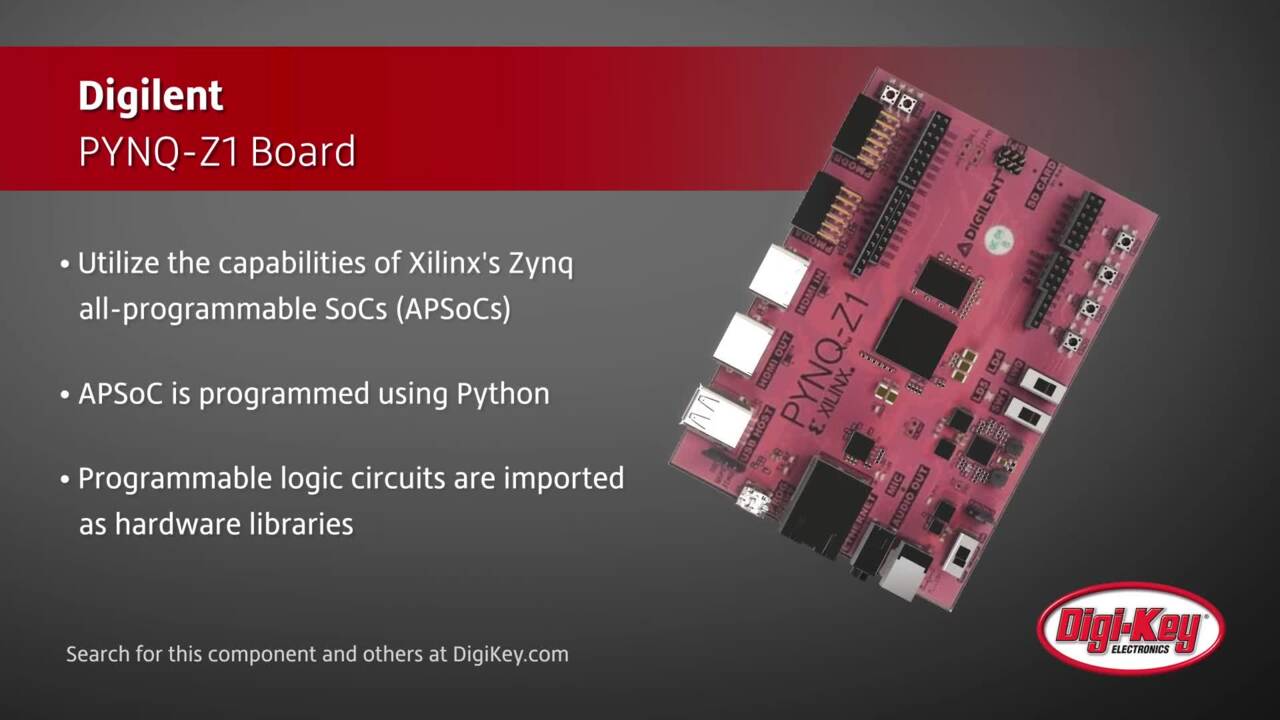

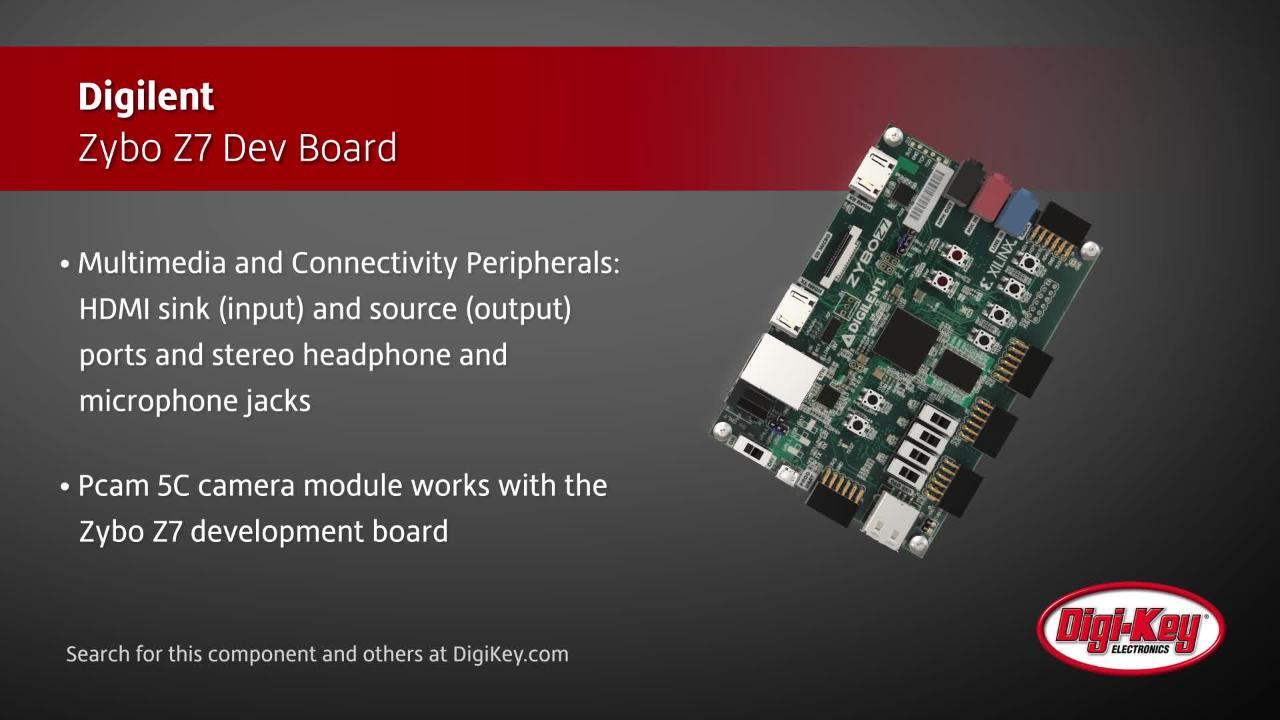

Los socios de RVfpga, incluido DigiKey, están trabajando con nosotros para que esto sea posible.

En tal sentido, les pedimos un día de su tiempo a fin de que puedan capacitar a la próxima generación de estudiantes de Ingeniería y Ciencias de la Computación y estos adquieran experiencia en el mundo real sobre arquitectura de computadoras y la arquitectura del conjunto de instrucciones RISC-V.

¿Qué es RVfpga?

En este taller presencial de RVfpga de un día, se presenta un sistema RISC-V comercial dirigido a un FPGA (arreglo programable de puertas en campo); se analizan la teoría, la arquitectura y la estructura del curso, y se muestra la forma de usar los laboratorios prácticos, como parte del curso completo de RVfpga.En el curso, se exploran los fundamentos de la arquitectura de computadoras utilizando el núcleo SweRV EH1 RISC-V de código abierto, completamente verificado y ya en silicio de Western Digital dirigido a un FPGA Xilinx Artix 7 en la placa de desarrollo Nexys A7 de Digilent. Todos obtendrán experiencia práctica con la plataforma de FPGA y las herramientas de software, lo que permitirá un comienzo rápido cuando regresen a sus universidades.

El SweRV no es un "núcleo con fines educativos"; este pertenece al mundo real y se usa dentro de las GPU de Imagination y las unidades de estado sólido de Western Digital.

¿Qué aprenderán?

- El taller muestra cómo poner en funcionamiento rápidamente el sistema de FPGA RISC-V y las herramientas RISC-V.

- Se describe cada uno de los laboratorios y se hace una demostración de algunos de ellos de forma práctica.

- Se discute también cómo integrar RVfpga en sus planes de estudios.

Los temas específicos incluyen:

- Instalación de las herramientas (que recomendamos antes del taller)

- Orientación del núcleo SweRV EH1 RISC-V y SoC a un FPGA

- Programación del SoC RISC-V

- Adición de más funcionalidad al SoC RISC-V

- Análisis y modificación de la jerarquía de núcleo RISC-V y memoria

¿Quién debe asistir?

- Este evento se dirige principalmente a la "Formación de profesores" y es de gran valor para los profesores de EE (Ingeniería Eléctrica), CS (Ciencias de la Computación) y CE (Ingeniería de Computación) que quieran enseñar Arquitectura de Computadoras.

- Los formadores de empresas comerciales lo encontrarán muy útil, así como los graduados que vislumbren una carrera docente o convertirse en diseñadores de chips.

Redes

Es una gran oportunidad para crear vínculos nuevos y actualizar los existentes con otros profesores que deseen mantener sus cursos actualizados. Ayúdennos a correr la voz y traigan a sus colegas.

Conozcan a innovadores que están evaluando usar RISC-V para proyectos emergentes y a formadores de empresas que necesitan excelentes materiales para formar a nuevos empleados.

Nuestros formadores:

Gracias a la colaboración con académicos cualificados y expertos de otras empresas que trabajan con RISC-V, contamos con algunos de los instructores más expertos del mundo.

ASEE Baltimore y UCSC Santa Clara

La profesora Sarah Harris es profesora de Ingeniería Eléctrica e Informática en la Universidad de Nevada, Las Vegas. Sarah Harris obtuvo su M.S. y Ph.D. en la Universidad de Stanford. Es coautora de tres conocidos libros de texto: Digital Design and Computer Architecture, Second Edition (2007), ARM Edition (2015), y RISC-V Edition (2021). Sus intereses de investigación incluyen desde arquitectura de computadoras, aplicaciones de sistemas integrados y aprendizaje automático hasta ingeniería biomédica y robótica.

Taiwán

Michio Abe, consolidado experto en arquitecturas de CPU RISC. Es director de Ventas y Soluciones para Japón en MIPS LLC. Su carrera comenzó en NEC en 1985 y ha participado en el desarrollo de CPU MIPS, incluido el desarrollo de CPU MIPS originales de NEC en 1991. A esto le siguió el desarrollo de SoC para vehículos con MIPS y otros núcleos y arquitecturas. Ha estado a cargo de la promoción y comercialización de CPU MIPS en Japón desde 2015, inicialmente como parte de Imagination Technologies y ahora como empresa independiente.

Nuestro anfitrión local es el profesor Brian Lin, de la NTUST de Taipéi.

FPL 2023 Gothenburg

Daniel A. Chaver Martínez obtuvo una licenciatura en Física en la Universidad de Santiago de Compostela (USC) en 1998 y una licenciatura en Ingeniería Electrónica en la Universidad Complutense de Madrid (UCM) en 2000. Desarrolló su Ph. D. de 2000 a 2006 en la UCM. Ha impartido diferentes cursos relacionados con la arquitectura de computadoras desde el año 2000. Sus intereses de investigación actuales incluyen: Técnicas arquitectónicas para memorias caché y no volátiles, y programación de sistemas operativos para multiprocesadores asimétricos. Desde 2015 colabora con Imagination Technologies en el desarrollo de procesadores y material didáctico.

Serie de talleres (fecha y ubicación)

| Fecha | Ubicación/evento | Ciudad, país | Formato | Registro |

|

Del 25 al 28 de junio |

Conferencia ASEE | Baltimore, EE. UU. |

Documento: RVfpga: Curso de Arquitectura de Computadoras y MOOC usando un SoC RISC-V dirigido a un FPGA y simulación |

https://nemo.asee.org/public/conferences/327/registration |

| Del 5 al 6 de julio |

NTUST |

Taipéi, Taiwán |

DOS talleres presenciales de RVfpga de un día en inglés (con soporte en mandarín y japonés) |

https://www.eventbrite.co.uk/e/549461984587 [eventbrite.co.uk] https://www.eventbrite.co.uk/e/602617443997 [eventbrite.co.uk] |

| Octubre, fecha por confirmar | Universidad de Zhejiang |

Hangzhou, China |

Taller presencial de RVfpga de medio día en chino. Formadores: Prof. Liu, Peng y Xi, Yuhao, Universidad de Zhejiang, Hangzhou |

Por anunciar |

| 5 de septiembre de 9 a. m. a 1 p. m. |

FPL 2023 |

Universidad de Chalmers, Gotemburgo, Suecia |

Taller presencial de RVfpga de medio día en inglés (Está disponible la inscripción solo para el taller: aproximadamente $120) |

https://2023.fpl.org/attend/registration |

| 9 de noviembre |

Centro de capacitación de UCSC Silicon Valley |

Santa Clara, Ca. EE. UU. |

Taller presencial de RVfpga de un día en inglés |

https://www.eventbrite.co.uk/e/rvfpga-understanding-computer-architecture-in-person-workshop-nov-9th-tickets-654132025497 |

Más información

- Sobre el IUP y RVfpga: https://university.imgtec.com/teaching-download/

- Blog de RISC-V: https://blog.imaginationtech.com/how-rvfpga-understanding-computer-architecture-will-give-under-grads-real-world-skills

- Introducción a RISC-V: https://www.digikey.com/en/resources/risc-v

Esperamos contar con su presencia.

Saludos,

Robert C. W. Owen

Consultor principal: Programa Universitario Mundial

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum