Usar el camino rápido de la FPGA para construir aplicaciones de inteligencia artificial de alto rendimiento y eficiencia energética

Colaboración de Editores de DigiKey de América del Norte

2021-01-12

Los diseñadores que buscan implementar algoritmos de inteligencia artificial (IA) en los procesadores de inferencia en el borde están bajo constante presión para reducir el consumo de energía y el tiempo de desarrollo, incluso cuando las demandas de procesamiento aumentan. Las matrices de puertas programables en campo (FPGA) ofrecen una combinación particularmente efectiva de velocidad y eficiencia energética para implementar los motores de inferencia de red neural (NN) requeridos para la IA de borde. Sin embargo, para los desarrolladores que no están familiarizados con las FPGA, los métodos convencionales de desarrollo de FPGA pueden parecer complejos, lo que a menudo hace que los desarrolladores recurran a soluciones menos óptimas.

Este artículo describe un enfoque más simple de la Microchip Technology que permite a los desarrolladores evitar el desarrollo tradicional de FPGA para crear NN entrenados usando FPGA y un kit de desarrollo de software (SDK), o usar un kit de video basado en FPGA para pasar inmediatamente al desarrollo de aplicaciones de visión integrada inteligente.

¿Por qué usar la IA de borde?

Edge computing aporta una serie de beneficios a las aplicaciones de la Internet de las Cosas (IoT) en segmentos tan variados como la automatización industrial, los sistemas de seguridad, los hogares inteligentes y más. En una aplicación de IoT industrial (IIoT) dirigida al piso de la fábrica, edge computing puede mejorar dramáticamente el tiempo de respuesta en los lazos de control de procesos eliminando los retrasos de ida y vuelta a las aplicaciones basadas en la nube. Del mismo modo, un sistema de seguridad basado en borde o una cerradura inteligente para la puerta de casa puede seguir funcionando incluso cuando la conexión a la nube se pierde accidental o intencionadamente. En muchos casos, el uso de edge computing en cualquiera de estas aplicaciones puede ayudar a reducir el costo operativo general al disminuir la dependencia del producto de los recursos de la nube. En lugar de enfrentarse a una necesidad inesperada de recursos de nube adicionales y costosos a medida que aumenta la demanda de sus productos, los desarrolladores pueden confiar en las capacidades de procesamiento local incorporadas en sus productos para ayudar a mantener los gastos de funcionamiento más estables.

La rápida aceptación y el aumento de la demanda de modelos de inferencia de aprendizaje automático (ML) amplifica drásticamente la importancia de edge computing. Para los desarrolladores, el procesamiento local de los modelos de inferencia ayuda a reducir la latencia de respuesta y los costos de los recursos de la nube necesarios para la inferencia basada en la nube. Para los usuarios, el uso de modelos de inferencia locales añade confianza en que sus productos seguirán funcionando a pesar de la pérdida ocasional de la conectividad a Internet o los cambios en las ofertas del proveedor del producto basadas en la nube. Además, la preocupación por la seguridad y la privacidad puede impulsar aún más la necesidad de un procesamiento y una inferencia locales para limitar la cantidad de información confidencial que se transfiere a la nube a través de la Internet pública.

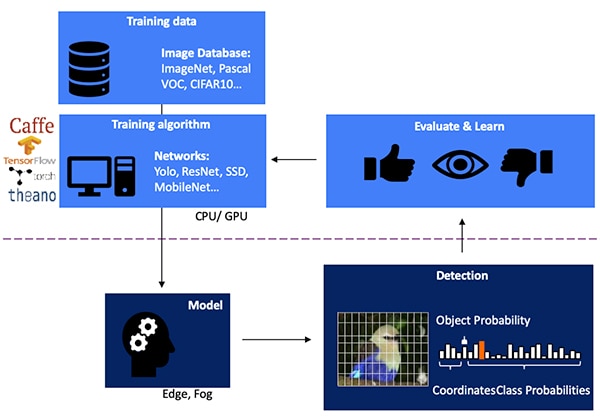

El desarrollo de un modelo de inferencia de NN para la detección de objetos basada en la visión es un proceso de varios pasos que comienza con el entrenamiento del modelo, generalmente realizado en un marco de ML como TensorFlow usando imágenes etiquetadas disponibles públicamente o imágenes etiquetadas personalizadas. Debido a las exigencias de procesamiento, la formación de modelos se realiza normalmente con unidades de procesamiento gráfico (GPU) en la nube o en otra plataforma de computación de alto rendimiento. Después de completar el entrenamiento, el modelo se convierte en un modelo de inferencia capaz de funcionar con recursos de edge computing o niebla y entregar los resultados de la inferencia como un conjunto de probabilidades de clase de objeto (Figura 1).

Figura 1: La implementación de un modelo de inferencia para la IA de borde se encuentra al final de un proceso de varios pasos que requiere el entrenamiento y la optimización de los NN en marcos que utilizan datos de entrenamiento disponibles o personalizados. (Fuente de la imagen: Microchip Technology)

Figura 1: La implementación de un modelo de inferencia para la IA de borde se encuentra al final de un proceso de varios pasos que requiere el entrenamiento y la optimización de los NN en marcos que utilizan datos de entrenamiento disponibles o personalizados. (Fuente de la imagen: Microchip Technology)

Por qué los modelos de inferencia son un reto computacional

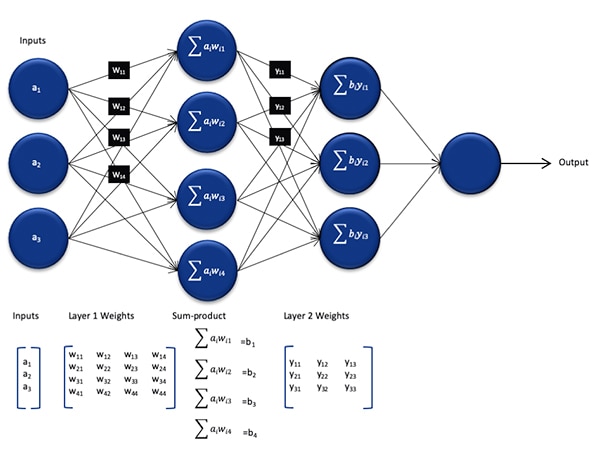

Aunque reducido en tamaño y complejidad en comparación con el modelo utilizado durante el proceso de capacitación, un modelo de inferencia NN sigue presentando un desafío computacional para los procesadores de uso general debido al gran número de cálculos que requiere. En su forma genérica, un modelo de NN profundo comprende múltiples capas de conjuntos de neuronas. Dentro de cada capa de una red totalmente conectada, cada nij de neurona necesita calcular la suma de los productos de cada entrada con un peso wij asociado (Figura 2).

Figura 2: El número de cálculos requeridos para la inferencia con un NN puede imponer una carga de trabajo computacional significativa. (Fuente de la imagen: Microchip Technology)

Figura 2: El número de cálculos requeridos para la inferencia con un NN puede imponer una carga de trabajo computacional significativa. (Fuente de la imagen: Microchip Technology)

No se muestra en la figura 2 el requisito computacional adicional impuesto por la función de activación que modifica la salida de cada neurona asignando valores negativos a cero, asignando valores superiores a 1 a 1 y funciones similares. La salida de la función de activación para cada nij de la neurona sirve como entrada a la siguiente capa i+1, continuando de esta manera para cada capa. Por último, la capa de salida del modelo NN produce un vector de salida que representa la probabilidad de que el vector (o matriz) de entrada original corresponda a una de las clases (o etiquetas) utilizadas durante el proceso de aprendizaje supervisado.

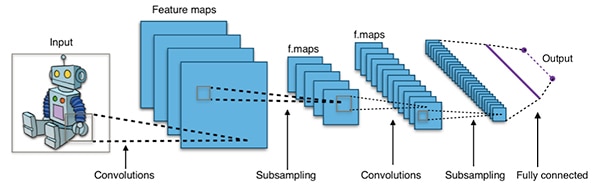

Los modelos efectivos de NN se construyen con arquitecturas mucho más grandes y complejas que la arquitectura genérica representativa de NN que se muestra arriba. Por ejemplo, un NN convolucional típico (CNN) utilizado para la detección de objetos de imagen aplica estos principios de manera fragmentaria, explorando a lo largo del ancho, alto y profundidad de color de una imagen de entrada para producir una serie de mapas de características que finalmente producen el vector de predicción de salida (Figura 3).

Figura 3: Las CNN utilizadas para la detección de objetos de imagen implican un gran número de neuronas en muchas capas, imponiendo una mayor demanda en la plataforma de computación. (Fuente de la imagen: Aphex34 CC BY-SA 4.0)

Figura 3: Las CNN utilizadas para la detección de objetos de imagen implican un gran número de neuronas en muchas capas, imponiendo una mayor demanda en la plataforma de computación. (Fuente de la imagen: Aphex34 CC BY-SA 4.0)

Usando FPGA para acelerar las matemáticas del NN

Aunque siguen surgiendo varias opciones para ejecutar los modelos de inferencia en el borde, pocas alternativas proporcionan una mezcla óptima de flexibilidad, rendimiento y eficiencia energética necesaria para una inferencia práctica de alta velocidad en el borde. Entre las alternativas fácilmente disponibles para la IA de borde, las FPGA son particularmente eficaces porque pueden proporcionar una ejecución de alto rendimiento basada en hardware de operaciones de computación intensiva, a la vez que consumen relativamente poca energía.

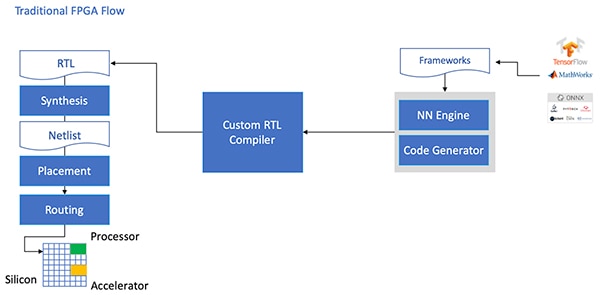

A pesar de sus ventajas, las FPGA a veces se pasan por alto debido a un flujo de desarrollo tradicional que puede ser desalentador para los desarrolladores sin una amplia experiencia en FPGA. Para crear una implementación efectiva de FPGA de un modelo de NN generado por un marco de NN, el desarrollador necesitaría entender los matices de convertir el modelo en lenguaje de transferencia de registros (RTL), sintetizar el diseño y trabajar en la etapa final de diseño físico de lugar y ruta para producir una implementación optimizada (Figura 4).

Figura 4: Para implementar un modelo de NN en una FPGA, los desarrolladores han necesitado hasta ahora entender cómo convertir sus modelos a RTL y trabajar a través del flujo tradicional de la FPGA. (Fuente de la imagen: Microchip Technology)

Figura 4: Para implementar un modelo de NN en una FPGA, los desarrolladores han necesitado hasta ahora entender cómo convertir sus modelos a RTL y trabajar a través del flujo tradicional de la FPGA. (Fuente de la imagen: Microchip Technology)

Con sus FPGA de PolarFire, software especializado y propiedad intelectual (IP) asociada, Microchip Technology proporciona una solución que hace que la inferencia de alto rendimiento y bajo consumo de energía en el borde esté ampliamente disponible para los desarrolladores sin experiencia en FPGA.

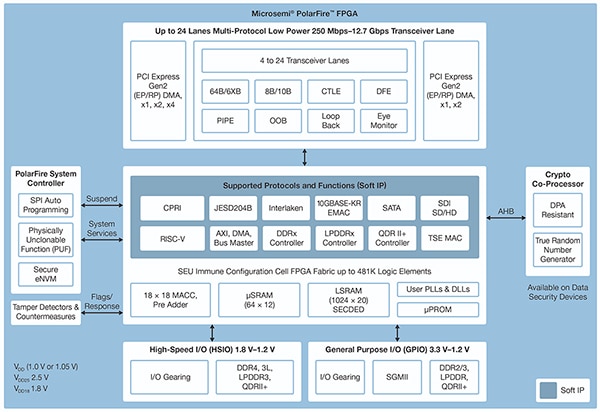

Fabricados con una avanzada tecnología de procesos no volátiles, los FPGA del PolarFire están diseñados para maximizar la flexibilidad y el rendimiento mientras se minimiza el consumo de energía. Junto con una amplia gama de interfaces de alta velocidad para comunicaciones y entrada/salida (E/S), presentan un profundo tejido FPGA capaz de soportar una funcionalidad avanzada utilizando núcleos IP blandos, incluyendo procesadores RISC-V, controladores de memoria avanzados y otros subsistemas de interfaz estándar (Figura 5).

Figura 5: La arquitectura PolarFire de Microchip Technology proporciona un tejido profundo diseñado para soportar los requisitos de diseño de alto rendimiento, incluyendo la implementación de un modelo de inferencia de cálculo intensivo. (Fuente de la imagen: Microchip Technology)

Figura 5: La arquitectura PolarFire de Microchip Technology proporciona un tejido profundo diseñado para soportar los requisitos de diseño de alto rendimiento, incluyendo la implementación de un modelo de inferencia de cálculo intensivo. (Fuente de la imagen: Microchip Technology)

El tejido de PolarFire FPGA proporciona un extenso conjunto de elementos lógicos y bloques especializados, soportados en una gama de capacidades por diferentes miembros de la familia del PolarFire FPGA, incluyendo las series MPF100T, MPF200T, MPF300T y MPF500T (Tabla 1).

|

Tabla 1: Una variedad de características y capacidades de tejido FPGA están disponibles en la serie PolarFire. (Fuente de la tabla: DigiKey, basado en la hoja de datos PolarFire de Microchip Technology)

Entre las características de particular interés para la aceleración de la inferencia, la arquitectura de PolarFire incluye un bloque matemático dedicado que proporciona una función de multiplicación y acumulación (MAC) de 18 bits × 18 bits firmada con una pre-agregador. Un modo de producto de puntos incorporado utiliza un solo bloque matemático para realizar dos operaciones de multiplicación de 8 bits, lo que proporciona un mecanismo para aumentar la capacidad aprovechando el impacto insignificante de la cuantificación del modelo en la precisión.

Además de acelerar las operaciones matemáticas, la arquitectura PolarFire ayuda a aliviar el tipo de congestión de memoria que se produce cuando se implementan modelos de inferencia en arquitecturas de propósito general, como pequeñas memorias distribuidas para almacenar los resultados intermedios creados durante la ejecución del algoritmo NN. Además, los pesos y valores de sesgo de un modelo NN pueden almacenarse en una memoria de sólo lectura (ROM) de 16 de profundidad por 18 bits de coeficiente, construida a partir de elementos lógicos situados cerca del bloque matemático.

Combinados con otras características del tejido FPGA del PolarFire, los bloques matemáticos proporcionan la base para el nivel más alto de CoreVectorBlox IP de Microchip Technology. Esto sirve como un motor NN flexible capaz de ejecutar diferentes tipos de NN. Junto con un conjunto de registros de control, el CoreVectorBlox IP incluye tres grandes bloques funcionales:

- Microcontrolador: Un simple procesador de software RISC-V que lee el objeto grande binario de firmware (BLOB) de Microchip y el archivo NN BLOB específico del usuario desde un almacenamiento externo. Controla las operaciones generales de CoreVectorBlox ejecutando instrucciones del BLOB de firmware.

- Procesador de matrices (MXP): Procesador suave que comprende ocho unidades aritméticas lógicas (ALU) de 32 bits y está diseñado para realizar operaciones paralelas en vectores de datos utilizando operaciones tensoriales elementales, como add, sub, xor, shift, mul, dotprod y otras, utilizando una precisión mixta de 8, 16 y 32 bits, según sea necesario.

- Acelerador de la CNN: Acelera las operaciones de MXP utilizando un conjunto bidimensional de funciones MAC implementadas mediante bloques matemáticos y operando con una precisión de 8 bits.

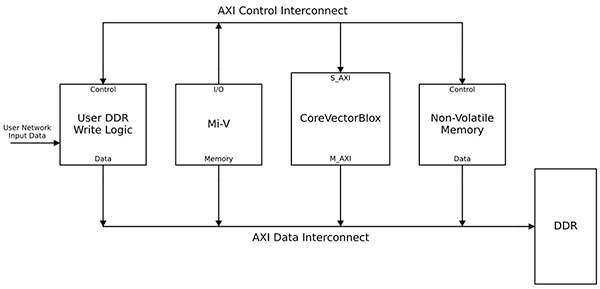

Un sistema de procesamiento NN completo combinaría un bloque IP CoreVectorBlox, memoria, controlador de memoria y un procesador anfitrión, como el núcleo del procesador de software Microsoft RISC-V (Mi-V) (Figura 6).

Figura 6: El bloque IP de CoreVectorBlox funciona con un procesador de host como el microcontrolador Mi-V RISC-V de Microchip para implementar un modelo de inferencia NN. (Fuente de la imagen: Microchip Technology)

Figura 6: El bloque IP de CoreVectorBlox funciona con un procesador de host como el microcontrolador Mi-V RISC-V de Microchip para implementar un modelo de inferencia NN. (Fuente de la imagen: Microchip Technology)

En una implementación de un sistema de video, el procesador anfitrión cargaría el firmware y los BLOB de red desde la memoria flash del sistema y los copiaría en la memoria de acceso aleatorio (RAM) de doble tasa de datos (DDR) para ser usados por el bloque CoreVectorBlox. A medida que llegan los cuadros de video, el procesador del host los escribe en la RAM DDR y le indica al bloque CoreVectorBlox que comience a procesar la imagen. Después de ejecutar el modelo de inferencia definido en la red BLOB, el bloque CoreVectorBlox escribe los resultados, incluyendo la clasificación de la imagen, de nuevo en la memoria RAM DDR para su uso por la aplicación de destino.

El flujo de desarrollo simplifica la aplicación de la NN FPGA

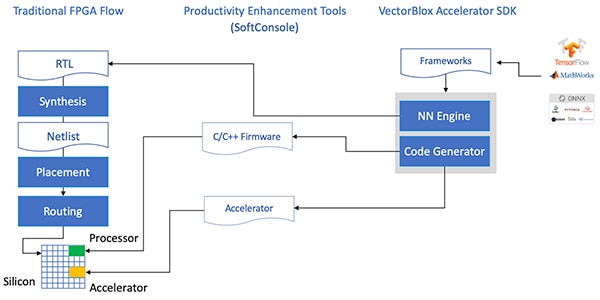

El microchip protege a los desarrolladores de la complejidad de implementar un modelo de inferencia de NN en las FPGA de PolarFire. En lugar de tratar los detalles del flujo tradicional de FPGA, los desarrolladores del modelo NN trabajan con sus marcos NN como de costumbre y cargan el modelo resultante en el Kit de Desarrollo de Software del Acelerador VectorBlox (SDK) de Microchip Technology. El SDK genera el conjunto de archivos necesarios, incluidos los necesarios para el flujo normal de desarrollo de la FPGA y los archivos de firmware y de red BLOB mencionados anteriormente (Figura 7).

Figura 7: El SDK del acelerador VectorBlox maneja los detalles de la implementación de un modelo NN en una FPGA, generando automáticamente los archivos necesarios para diseñar y ejecutar el modelo de inferencia basado en la FPGA. (Fuente de la imagen: Microchip Technology)

Figura 7: El SDK del acelerador VectorBlox maneja los detalles de la implementación de un modelo NN en una FPGA, generando automáticamente los archivos necesarios para diseñar y ejecutar el modelo de inferencia basado en la FPGA. (Fuente de la imagen: Microchip Technology)

Debido a que el flujo del SDK del acelerador de VectorBlox superpone el diseño del NN sobre el motor de NN implementado en la FPGA, diferentes NN pueden funcionar en el mismo diseño de la FPGA sin necesidad de rehacer el flujo de síntesis del diseño de la FPGA. Los desarrolladores crean un código C/C++ para el sistema resultante y pueden cambiar los modelos dentro del sistema sobre la marcha o ejecutar los modelos simultáneamente usando el corte de tiempo.

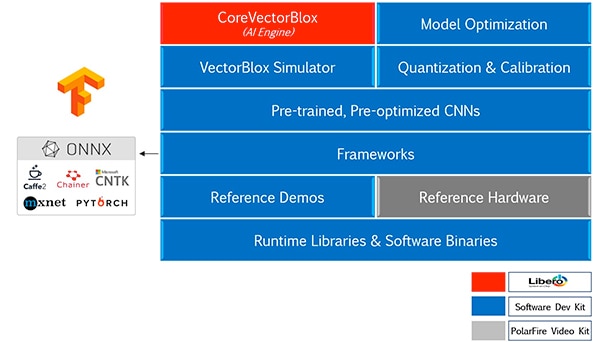

El SDK del acelerador VectorBlox fusiona el paquete de diseño FPGA Libero de Microchip Technology con un conjunto completo de capacidades para el desarrollo de modelos de inferencia NN. Junto con los servicios de optimización, cuantificación y calibración de modelos, el SDK proporciona un simulador de NN que permite a los desarrolladores utilizar los mismos archivos BLOB para evaluar su modelo antes de su uso en la implementación del hardware de la FPGA (Figura 8).

Figura 8: El SDK del acelerador VectorBlox proporciona un conjunto completo de servicios diseñados para optimizar la implementación de FPGA de los modelos de inferencia generados por el marco. (Fuente de la imagen: Microchip Technology)

Figura 8: El SDK del acelerador VectorBlox proporciona un conjunto completo de servicios diseñados para optimizar la implementación de FPGA de los modelos de inferencia generados por el marco. (Fuente de la imagen: Microchip Technology)

El SDK del acelerador VectorBlox soporta modelos en formato de Intercambio de Redes Neurales Abiertas (ONNX) así como modelos de varios marcos de trabajo incluyendo TensorFlow, Caffe, Chainer, PyTorch, y MXNET. Las arquitecturas de CNN soportadas incluyen MNIST, versiones de MobileNet, ResNet-50, Tiny Yolo V2, y Tiny Yolo V3. Microchip está trabajando para expandir el soporte para incluir la mayoría de las redes en el conjunto de herramientas de código abierto OpenVINO zoo de modelos pre-entrenados, incluyendo Yolo V3, Yolo V4, RetinaNet, y SSD-MobileNet, entre muchos otros.

El kit de video demuestra la inferencia de la FPGA

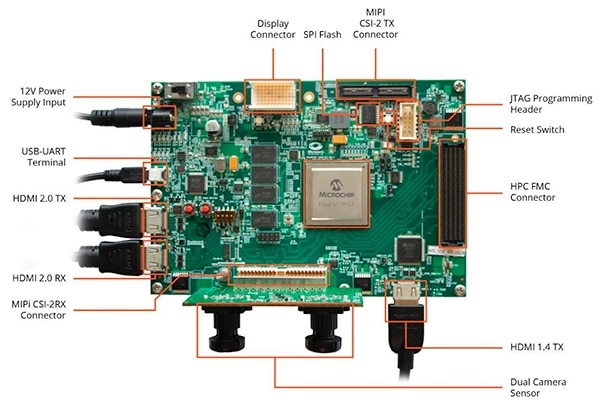

Para ayudar a los desarrolladores a avanzar rápidamente en el desarrollo de aplicaciones de visión incorporada inteligente, Microchip Technology proporciona una completa aplicación de muestra diseñada para funcionar en el kit de imagen y video de FPGA PolarFireMPF300-VIDEO-KIT y diseño de referencia.

Al basarse en el FPGA PolarFire MPF300T de Microchip, la placa del kit combina un sensor de cámara dual, una RAM de doble velocidad de datos 4 (DDR4), memoria flash, gestión de la energía y una variedad de interfaces (Figura 9).

Figura 9: El kit de video e imágenes FPGA PolarFire MPF300-VIDEO-KIT de Microchip y el software asociado proporcionan a los desarrolladores un rápido inicio de la inferencia basada en FPGA en aplicaciones inteligentes de visión integrada. (Fuente de la imagen: Microchip Technology)

Figura 9: El kit de video e imágenes FPGA PolarFire MPF300-VIDEO-KIT de Microchip y el software asociado proporcionan a los desarrolladores un rápido inicio de la inferencia basada en FPGA en aplicaciones inteligentes de visión integrada. (Fuente de la imagen: Microchip Technology)

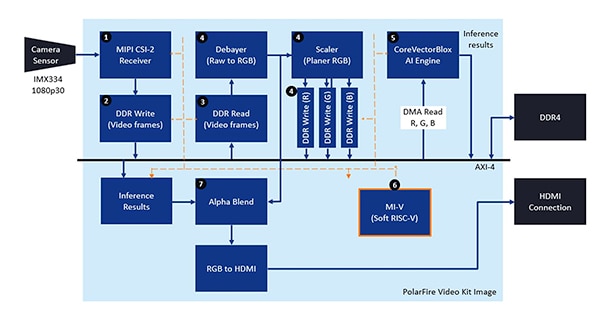

El kit viene con un proyecto de diseño completo de Libero usado para generar el firmware y los archivos BLOB de la red. Después de programar los archivos BLOB en la memoria flash incorporada, los desarrolladores hacen clic en el botón de ejecución en Libero para iniciar la demostración, que procesa las imágenes de video del sensor de la cámara y muestra los resultados de la inferencia en una pantalla (Figura 10).

Figura 10: El Kit de video e imágenes FPGA PolarFire de Microchip Technology demuestra cómo diseñar y utilizar una implementación FPGA de un sistema inteligente de visión incorporado construido alrededor del motor NN del Microchip CoreVectorBlox. (Fuente de la imagen: Microchip Technology)

Figura 10: El Kit de video e imágenes FPGA PolarFire de Microchip Technology demuestra cómo diseñar y utilizar una implementación FPGA de un sistema inteligente de visión incorporado construido alrededor del motor NN del Microchip CoreVectorBlox. (Fuente de la imagen: Microchip Technology)

Para cada cuadro de vídeo de entrada, el sistema basado en FPGA ejecuta los siguientes pasos (con los números de los pasos correlacionados con la figura 10):

- Cargar un cuadro de la cámara

- Almacenar el marco en la memoria RAM

- Lee el cuadro de la RAM

- Convierte la imagen en bruto a RGB, RGB plano, y almacena el resultado en la RAM

- El procesador Mi-V soft RISC-V inicia el motor CoreVectorBlox, que recupera la imagen de la RAM, realiza la inferencia y almacena los resultados de la probabilidad de clasificación de vuelta a la RAM

- El Mi-V utiliza los resultados para crear un marco de superposición con cuadros delimitadores, resultados de clasificación y otros metadatos y almacena el marco en la RAM

- El marco original se mezcla con el marco de superposición y se escribe en la pantalla HDMI

La demostración admite la aceleración de los modelos Tiny Yolo V3 y MobileNet V2, pero los desarrolladores pueden ejecutar otros modelos admitidos por el SDK utilizando los métodos descritos anteriormente, realizando un pequeño cambio de código para añadir el nombre del modelo y los metadatos a la lista existente que contiene los dos modelos predeterminados.

Conclusión:

Los algoritmos de IA, como los modelos NN, suelen imponer cargas de trabajo intensivas en computación que requieren recursos de computación más robustos que los disponibles con los procesadores de propósito general. Mientras que las FPGA están bien equipadas para cumplir con los requisitos de rendimiento y baja potencia de la ejecución del modelo de inferencia, los métodos convencionales de desarrollo de FPGA pueden parecer complejos, lo que a menudo hace que los desarrolladores recurran a soluciones no óptimas.

Como se ha demostrado, utilizando IP especializado y software de la tecnología del microchip, los desarrolladores sin experiencia en FPGA pueden implementar diseños basados en la inferencia con mayor capacidad para cumplir con los requisitos de rendimiento, potencia y programación del diseño.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.