Cómo implementar la IA Edge en FPGA con herramientas familiares

Colaboración de Editores de DigiKey de América del Norte

2026-02-17

La inteligencia artificial (IA) en el borde de la red (IA edge) rara vez significa sólo inferencia. Las implantaciones en el mundo real suelen implicar entrada/salida (E/S) de alta velocidad, acondicionamiento de señales y bucles de control en tiempo real, todos los cuales se ejecutan de forma concurrente. Estas cargas de trabajo multifunción exigen una coordinación estrecha y unos niveles de determinismo que los diseñadores consideran difíciles de alcanzar utilizando el hardware de IA convencional.

Dos factores agravan la cuestión. En primer lugar, los modelos de IA evolucionan a un ritmo vertiginoso, lo que obliga a los diseñadores a adoptar plataformas que admitan actualizaciones rápidas de los algoritmos. Al mismo tiempo, muchos sistemas de borde permanecen en el campo durante una década o más, lo que dificulta garantizar la adaptabilidad a largo plazo. En segundo lugar, el camino desde el modelo entrenado hasta el sistema implementado sigue estando fragmentado. Los científicos de datos trabajan en PyTorch y TensorFlow, mientras que los equipos integrados utilizan cadenas de herramientas totalmente diferentes, lo que crea fricciones durante los traspasos y ralentiza el tiempo de producción.

Para hacer frente a estos desafíos se necesitan plataformas que combinen un procesamiento de IA de alto rendimiento con un comportamiento determinista, una E/S flexible y una adaptabilidad a largo plazo, todo ello dentro de unas envolventes de potencia limitadas típicas de las implementaciones de borde.

Este artículo destaca las aplicaciones y los requisitos asociados que desafían a los diseñadores a explorar nuevas arquitecturas de IA edge. A continuación, se presentan los dispositivos de arreglos de compuerta programable en campo (FPGA) habilitados para IA edge y las herramientas de software de Altera, y muestra cómo pueden utilizarse para satisfacer las necesidades de estas aplicaciones en una amplia gama de puntos de rendimiento y potencia.

La evolución de la IA Edge exige innovación arquitectónica

Los sistemas Edge emplean cada vez más diversas técnicas de IA, el clásico aprendizaje automático (ML) para la detección de anomalías, las redes neuronales convolucionales (CNN) para la percepción y los transformadores para los grandes modelos lingüísticos (LLM). Estos algoritmos de cálculo intensivo coexisten a menudo con funciones exigentes ajenas a la IA, como el procesamiento de señales, la creación de redes y el control en tiempo real.

Los sistemas autónomos son un buen ejemplo. A menudo necesitan ingerir datos procedentes de múltiples modalidades de sensores (por ejemplo, video, audio, radar, LiDAR y retroalimentación de movimiento/posición), procesar previamente esos flujos con un alto rendimiento, analizar los resultados con IA sofisticada y, a continuación, gestionar bucles de control de alta precisión, todo ello con un determinismo fiable.

Se pueden encontrar muchos ejemplos similares en aplicaciones de automatización industrial, imágenes médicas, defensa y telecomunicaciones. Un tema común es que las cargas de trabajo convergentes son difíciles de acomodar con las arquitecturas tradicionales.

Cómo las FPGA son especialmente adecuadas para la IA edge

Por el contrario, estos requisitos se adaptan bien a las capacidades de las FPGA. En su núcleo, las FPGA proporcionan una lógica configurable que ejecuta operaciones en verdadero paralelo, con un comportamiento de temporización incorporado en el momento del diseño en lugar de fluctuar durante el tiempo de ejecución. Esta arquitectura permite el determinismo de baja latencia crítico para la IA de borde. La lógica flexible también aprovecha las potentes E/S: Por lo general, las FPGA ofrecen una gran cantidad de E/S de alta velocidad que pueden interactuar con una amplia gama de sensores y actuadores, proporcionando un acoplamiento estrecho con el procesamiento de IA.

Las FPGA también contienen memoria interna distribuida, que mantiene los datos cerca de la lógica que opera con ellos. Esto reduce los cuellos de botella que surgen cuando varias etapas de procesamiento deben competir por el acceso a un bus de memoria compartida, una limitación habitual en las arquitecturas basadas en procesadores.

Muchos FPGA también incorporan hardware especializado de procesamiento de señal digital (DSP). Estos circuitos reforzados ofrecen un mayor rendimiento y una mejor eficiencia energética para las cargas de trabajo de procesamiento de señales que el tejido de uso general. Algunas FPGA también integran sistemas de procesadores cableados que pueden ejecutar pilas de software estándar, incluido Linux, lo que permite el desarrollo de software convencional para tareas como redes, gestión de dispositivos e interfaces de usuario.

En resumen, una única FPGA puede consolidar funciones que, de otro modo, requerirían chips de E/S, aceleradores de IA, DSP y procesadores de plano de control independientes. El resultado puede ser una lista de materiales (BOM) reducida, una huella de placa más pequeña y un menor consumo de energía, manteniendo al mismo tiempo la baja latencia y el determinismo que exigen las aplicaciones de IA edge.

Cómo la incorporación de bloques tensoriales de IA desbloquea nuevas posibilidades

El hardware FPGA DSP tradicional ya está bien adaptado a muchas cargas de trabajo de borde, pero la inferencia de IA tiende a estar dominada por operaciones de multiplicación-acumulación densas, pero de baja precisión. Para solucionar este problema, los dispositivos Agilex 3 y Agilex 5 de Altera incorporan DSP mejorados con bloques de tensor de IA. Se trata de hardware especializado para multiplicaciones matriz-matriz y vector-matriz, que aparecen repetidamente en los gráficos de cálculo de la IA.

En el corazón de este enfoque se encuentra un producto escalar y un motor sumador/acumulador (Figura 1). En el modo tensor, el motor de puntos cableado realiza un producto de puntos de 10 elementos utilizando entradas de 8 bits y pesos precargados de 8 bits. Para ampliar el rango dinámico, la ruta de datos también puede utilizar un "exponente común" compartido para el escalado de estilo de punto flotante en bloque, abordando el escenario típico en el que la inferencia de IA requiere un alto rango dinámico pero una baja precisión.

Figura 1: El bloque tensor de IA puede realizar productos de puntos de 10 elementos. (Fuente de la imagen: Altera)

Figura 1: El bloque tensor de IA puede realizar productos de puntos de 10 elementos. (Fuente de la imagen: Altera)

El resultado del producto de punto es de 32 bits (punto fijo o punto flotante de precisión única), y puede conectarse en cascada a una etapa sumadora/acumuladora adicional para calcular productos de punto más grandes a través de bloques adyacentes. Cada bloque tensor de IA incluye dos columnas punto-producto, lo que permite una gran variedad de modos de funcionamiento.

En un caso de uso típico, parte del hardware matemático mejorado se utiliza en su función tradicional de DSP, como la realización de transformadas rápidas de Fourier (FFT) en datos de radar. Otros se utilizan como bloques tensoriales de IA, como una CNN para realizar la detección de objetos. Esta flexibilidad es fundamental para los sistemas de borde que deben manejar la IA junto con otras funciones de cálculo intensivo.

Una gama de opciones de FPGA para diferentes cargas de trabajo de IA

Las familias Agilex también proporcionan una flexibilidad considerable en el escalado del rendimiento. Las piezas van desde dispositivos centrados en la eficiencia que miden solo 12 mm × 12 mm hasta variantes de alto rendimiento que ofrecen hasta 152.6 teraoperaciones pico por segundo (TOPS), con un escalado similar en las capacidades de interfaz de E/S y memoria.

Un ejemplo de pieza de alto rendimiento es el Agilex 5 A5ED065BB32AE4SR0, que ofrece 22.7 TOPS en un encapsulado de 32 × 32 mm. Un ejemplo de pieza orientada a la eficiencia es el Agilex 3 A3CW135BM16AE6S, que proporciona 2.8 TOPS en un encapsulado de 16 × 16 mm. Las especificaciones clave de cada uno de ellos se muestran en la Tabla 1.

|

Tabla 1: Se muestran algunas especificaciones clave de las FPGA Agilex 5 y Agilex 3 de muestra. (Fuente de la tabla: Altera (modificado por el autor))

Ambas familias están disponibles como FPGA tradicionales o como sistemas en chip (SoC) con procesadores Arm integrados. Los SoC Agilex 3 incorporan un doble núcleo Arm Cortex-A55 de 800 megahercios (MHz). Los SoC Agilex 5 presentan un clúster asimétrico con núcleos Cortex-A76 duales a 1.8 gigahercios (GHz) junto a núcleos Cortex-A55 duales a 1.5 GHz. Ambas configuraciones son compatibles con Linux, lo que permite el desarrollo de software convencional para redes, gestión de dispositivos e interfaces de usuario.

Simplificación de la implementación de la IA edge mediante FPGA

Los modelos de IA suelen desarrollarse en marcos centrados en el software con ciclos de iteración rápidos, mientras que las implementaciones FPGA requerían históricamente conocimientos de desarrollo de hardware y ciclos de integración más largos. El paquete FPGA AI Suite de Altera (Figura 2) proporciona un camino más directo desde un modelo entrenado hasta una propiedad intelectual (IP) de inferencia FPGA implementable utilizando un flujo compatible con el utillaje de IA estándar de la industria.

Figura 2: El flujo de trabajo de FPGA AI Suite tiende un puente entre los marcos de trabajo de IA estándar y la implementación de FPGA. (Fuente de la imagen: Altera)

Figura 2: El flujo de trabajo de FPGA AI Suite tiende un puente entre los marcos de trabajo de IA estándar y la implementación de FPGA. (Fuente de la imagen: Altera)

El flujo de trabajo puede resumirse de la siguiente manera:

- Desarrolle el modelo de inferencia en un marco estándar como PyTorch, TensorFlow u ONNX.

- Utilice el kit de herramientas OpenVINO para convertir el modelo en una representación intermedia (RI) compuesta por un archivo gráfico (.xml) y pesos (.bin).

- Pase los artefactos IR al compilador de gráficos de IA de FPGA, que mapea el modelo en los recursos FPGA disponibles. Dichos recursos pueden incluir un procesador host externo, un procesador interno o una configuración sin cabezal.

- Compile e implemente las capas resultantes utilizando Quartus Prime Pro Edition, con la ejecución gestionada a través de la pila de tiempo de ejecución del motor de inferencia y las interfaces de programación de aplicaciones (API) de IA de FPGA para el movimiento de memoria y la programación del hardware.

- Como parte del proceso de compilación, utilice el optimizador de arquitectura para equilibrar el rendimiento y el uso de recursos. Por ejemplo, utilícelo para asegurarse de que la implementación cumple los objetivos de rendimiento de inferencia dejando espacio para otra lógica de la FPGA.

En términos prácticos, el valor de este enfoque es que convierte la "implementación en una FPGA" en un proceso de integración más que en un esfuerzo de diseño del acelerador. Los científicos de datos pueden permanecer dentro de los flujos de trabajo de desarrollo de modelos establecidos, mientras que los equipos de FPGA e integrados reciben artefactos que encajan de forma natural en un ciclo de construcción e implementación, lo que permite una iteración más rápida a medida que evolucionan los modelos y los requisitos. Los modelos preentrenados disponibles a través del zoo de modelos abiertos para el kit de herramientas OpenVINO pueden acelerar aún más el desarrollo.

Comenzar rápidamente con kits de desarrollo fáciles de usar

Para empezar a explorar la IA edge en FPGA, los diseñadores disponen de varias opciones de kits de desarrollo. Para aplicaciones de mayor rendimiento, el kit de desarrollo Terasic P0775 Atum A5 (figura 3) es una buena elección. El kit se desarrolló en torno al Agilex 5 A5ED065BB32AE4SR0 y proporciona una amplia mezcla de interfaces adecuadas para sistemas de clase edge. Entre sus principales características se incluyen 8 gigabytes (Gbytes) de memoria DDR4, puertos QSFP+ y Ethernet (GbE) de 2.5 gigabits (Gbit), PCIe Gen 3 x4, conectores de cámara MIPI duales y una salida HDMI. El kit incluye una licencia gratuita para Quartus Prime Pro Edition.

Figura 3: El kit de desarrollo P0775 Atum A5 proporciona acceso al desarrollo de IA y visión de alto rendimiento. (Fuente de la imagen: Terasic)

Figura 3: El kit de desarrollo P0775 Atum A5 proporciona acceso al desarrollo de IA y visión de alto rendimiento. (Fuente de la imagen: Terasic)

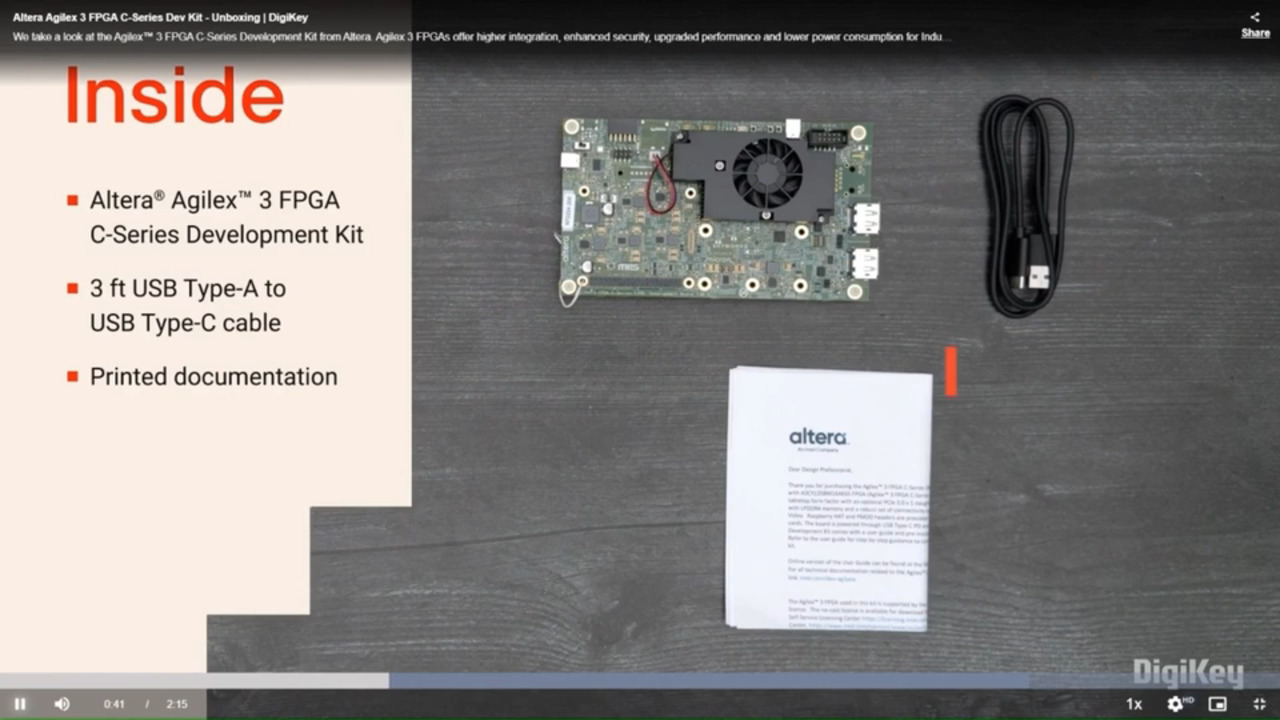

Para aplicaciones centradas en la eficiencia, los diseñadores pueden recurrir al kit de desarrollo FPGA Agilex 3 y SoC serie C DK-A3W135BM16AEA (figura 4). Este kit está desarrollado en torno a la Agilex 3 A3CW135BM16AE6S y hace hincapié en la creación de prototipos compactos con una expansión respetuosa con el ecosistema. La placa proporciona 4 Gbytes de LPDDR4, GbE, DisplayPort y USB 2.0, junto con un conector Raspberry Pi HAT y una interfaz Digilent Pmod para una expansión de baja fricción.

Figura 4: El kit de desarrollo FPGA Agilex 3 y SoC serie C DK-A3W135BM16AEA proporciona una plataforma compacta para la IA edge centrada en la eficiencia. (Fuente de la imagen: Altera)

Figura 4: El kit de desarrollo FPGA Agilex 3 y SoC serie C DK-A3W135BM16AEA proporciona una plataforma compacta para la IA edge centrada en la eficiencia. (Fuente de la imagen: Altera)

Conclusión

La introducción de los LLM y otras cargas de trabajo de IA novedosas en el borde está impulsando a los desarrolladores a buscar nuevos enfoques. Las FPGA ofrecen una solución única que no solo proporciona un rendimiento determinista y de baja latencia, sino que también se encarga de muchas otras funciones del sistema. Con las FPGA Agilex compatibles con IA y la FPGA AI Suite, los desarrolladores pueden acceder a estas capacidades de forma rápida y sencilla, abriendo nuevas posibilidades arquitectónicas para diseños altamente adaptables y duraderos.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.