Diseñe un ECG de alta resolución con un amplificador totalmente diferencial y un ADC de alta resolución

Colaboración de Editores de DigiKey de América del Norte

2019-10-31

Los ECG no invasivos de uso médico crean típicamente representaciones visuales básicas del estado de salud del corazón para el análisis clínico y la intervención médica. Sin embargo, algunos detalles del funcionamiento del corazón, como el "potencial tardío", requieren componentes electrónicos de ECG de resolución extremadamente alta. La resolución espacial requerida para estas imágenes puede verse comprometida por el ruido y otros inhibidores del rendimiento en el detector del ECG, el sistema del detector, e incluso por la técnica de adquisición.

Los diseñadores pueden evitar muchos problemas y desarrollar un sistema de ECG de alta precisión mediante la aplicación efectiva de un controlador de bajo nivel de ruido y un ADC de alta resolución.

Este artículo resume cómo funcionan los ECG antes de detallar los problemas asociados con el emparejamiento de un amplificador de controlador con un ADC de alta resolución para esta aplicación. Luego introduce una combinación de muestras que comprende la alta velocidad del ADA4945-1ACPZ-R7 de Analog Devices, el controlador de ADC totalmente diferencial y el ADC AD7768BSTZ de Analog Devices de ocho canales y 24 bits, y muestra cómo configurar resistencias y condensadores externos para lograr un rendimiento óptimo.

El sistema de ECG

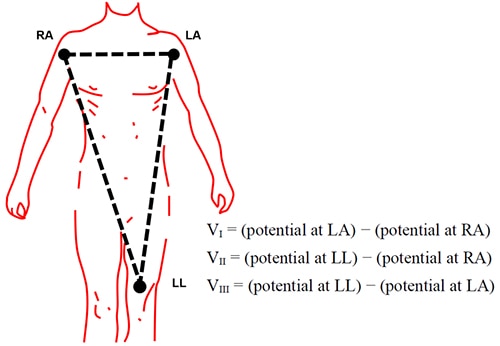

El ECG es una prueba no invasiva que refleja las afecciones cardíacas subyacentes mediante la recopilación de señales eléctricas de mV (milivoltios) generadas por el corazón. Las señales de ECG se pueden detectar en muchos puntos del cuerpo, pero décadas de tradición médica estandarizaron las ubicaciones aceptadas de esos puntos en una formación imaginaria de tres derivaciones de extremidades, llamada triángulo de Einthoven (Figura 1).

Figura 1: Las señales de ECG se pueden detectar en muchos puntos del cuerpo, pero el triángulo de Einthoven define las ubicaciones generalmente aceptadas. (Fuente de la imagen: DigiKey)

Figura 1: Las señales de ECG se pueden detectar en muchos puntos del cuerpo, pero el triángulo de Einthoven define las ubicaciones generalmente aceptadas. (Fuente de la imagen: DigiKey)

El triángulo describe la colocación de los electrodos RA (brazo derecho), LA (brazo izquierdo) y LL (pierna izquierda). También forman los valores VI, VII y VIII .

Los datos de este sistema permiten a los médicos comprender la frecuencia subyacente y el mecanismo del ritmo cardíaco. Sin embargo, con un examen más detallado, los datos pueden mostrar el aumento del grosor (hipertrofia) y el daño generado a las diversas partes del músculo cardíaco. Además, el gráfico de ECG bidimensional simple puede proporcionar evidencia de flujo sanguíneo muy deficiente al músculo cardíaco o patrones de actividad eléctrica anormal que pueden predisponer al paciente a alteraciones anormales del ritmo cardíaco.

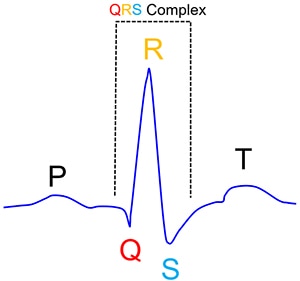

Se muestra la señal de ECG del corazón normal, que enfatiza la combinación usual de tres de las desviaciones gráficas observadas en un electrocardiograma típico, llamado complejo QRS (Figura 2).

Figura 2: Los puntos Q, R y S crean el complejo QRS, que por lo general es la parte central y visualmente más obvia de un gráfico de ECG. (Fuente de la imagen: DigiKey)

Figura 2: Los puntos Q, R y S crean el complejo QRS, que por lo general es la parte central y visualmente más obvia de un gráfico de ECG. (Fuente de la imagen: DigiKey)

El complejo QRS es la parte central y más evidente de la señal. Esta señal corresponde a la despolarización de los ventrículos derecho e izquierdo del corazón humano. En adultos, el complejo QRS por lo general dura de 0.08 a 0.10 segundos. Una duración del complejo QRS de más de 0.12 s se considera anormal. El desafío de medición en el sistema de ECG es captar de manera confiable y completa la señal QRS.

Este desafío no es tan complejo. En teoría, la frecuencia de muestra para un equipo de ECG es de al menos 50 Hz. Las verdaderas implementaciones de ECG tienen una frecuencia de muestra de más de 500 Hz, con una velocidad de conversión típica del convertidor interno del detector de ECG ≥1 kHz (kilohercio). Con estas frecuencias de muestra, la resolución requerida de los convertidores internos del sistema de detección de ECG típico es de 12 bits.

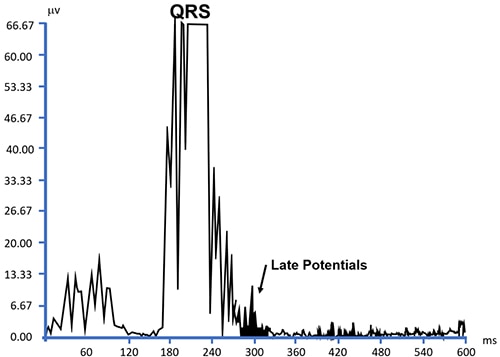

Estas especificaciones de resolución y velocidad son consistentes con un detector de ECG de uso general. Sin embargo, algunas irregularidades cardíacas solo se pueden detectar con detectores de ECG de mayor resolución. Por ejemplo, los pacientes que presentan VT (taquicardia ventricular sostenida) pueden tener formas de onda de baja amplitud y alta frecuencia en la parte terminal del complejo QRS que persisten durante decenas de milisegundos. Se cree que la despolarización posterior temprana de las células del ventrículo derecho generan los "potenciales tardíos" de los resultados de ECG (Figura 3).

Figura 3: Los potenciales tardíos de los resultados de ECG ocurren durante el complejo QRS, pero por lo general son demasiado pequeños y no aparecen en los detectores típicos de ECG. (Fuente de la imagen: DigiKey)

Figura 3: Los potenciales tardíos de los resultados de ECG ocurren durante el complejo QRS, pero por lo general son demasiado pequeños y no aparecen en los detectores típicos de ECG. (Fuente de la imagen: DigiKey)

Las amplitudes potenciales tardías a menudo son demasiado pequeñas para aparecer en un ECG normal. Sin embargo, con sistemas de alta resolución de más de 20 bits, el ADC promedia las grabaciones internas del complejo QRS para filtrar el ruido aleatorio, de manera que los potenciales tardíos se hacen visibles en la imagen del ECG.

Existen implicaciones clínicas importantes cuando los ECG no invasivos de alta resolución pueden detectar potenciales tardíos cardíacos. Por ejemplo, con pacientes que tienen MI (infarto agudo de miocardio), la detección del potencial tardío es importante para el pronóstico. La presencia del potencial tardío ventricular en dichos pacientes es un indicador de riesgo de MI posterior o muerte cardíaca repentina. Antes, esta clasificación y el diagnóstico posterior solo eran posibles mediante técnicas invasivas o mínimamente invasivas.

Sin embargo, para hacer visibles las señales que a menudo son indetectables mediante un ECG, se requieren técnicas avanzadas de adquisición y procesamiento de señales que usan ADC Sigma-Delta (ƩΔ) de alta resolución.

Sistemas de conversión de alta resolución

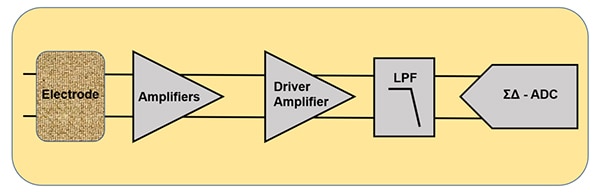

Un sistema típico de ECG tiene doce electrodos que se adhieren a la piel del paciente y detectan las señales cardíacas de milivoltios, divididas por 1,000 o microvoltios (mV). Cada una de las señales del electrodo llega al front-end de acondicionamiento de señales en el que los amplificadores de instrumentación obtienen la señal en microvoltios a fin de prepararse el controlador de amplificador y, en última instancia, el ADC ƩΔ de alta resolución (Figura 4).

Figura 4: Un diagrama de bloques de acondicionamiento de señal de front-end de ECG para un sistema de detección médica de alta resolución, que comienza con tres amplificadores operacionales de amplificadores de instrumentación. (Fuente de la imagen: DigiKey)

Figura 4: Un diagrama de bloques de acondicionamiento de señal de front-end de ECG para un sistema de detección médica de alta resolución, que comienza con tres amplificadores operacionales de amplificadores de instrumentación. (Fuente de la imagen: DigiKey)

Los primeros dispositivos de la cadena de señal son tres amplificadores de instrumentación de amplificadores de operacionales de precisión y quizás una segunda etapa de ganancia. Estos dispositivos establecen conexión a tierra y ganancia diferencial para las señales de bajo nivel de microvoltios. El amplificador de controlador y el LPF (filtro de paso bajo) adquieren la señal de ECG de ganancia diferencial obtenida que proporciona un amplio accionamiento y filtrado para el ADC ƩΔ de alta resolución.

Amplificador de controlador y ADC ƩΔ

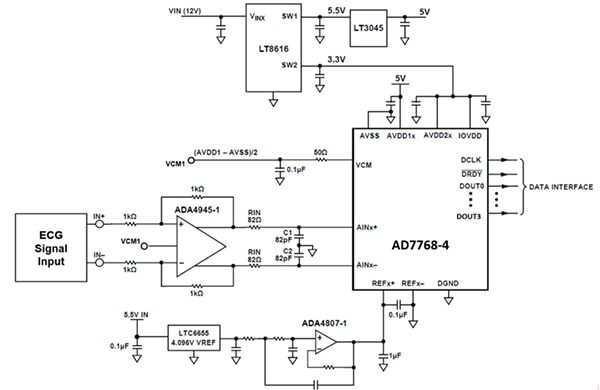

Una función crítica del diagrama de bloques de acondicionamiento de señales front-end es el amplificador de controlador y la relación ADC ƩΔ. Un controlador ADC ADA4945-1 totalmente diferencial estimula la entrada al ADC ƩΔ AD7768-4 de alta resolución (Figura 5).

Figura 5: Diagrama de conexión típico para el ADC ƩΔ AD7768-4 de alta resolución, con el ADA4945-1 como amplificador de controlador. (Fuente de la imagen: DigiKey Electronics, basado en material fuente de Analog Devices)

Figura 5: Diagrama de conexión típico para el ADC ƩΔ AD7768-4 de alta resolución, con el ADA4945-1 como amplificador de controlador. (Fuente de la imagen: DigiKey Electronics, basado en material fuente de Analog Devices)

El amplificador de controlador ADA4945-1 y la red de LPF, R/C (resistencia/condensador) envían la señal a la entrada del ADC ƩΔ (AD7768-4).

El AD7768-4 es un ADC ƩΔ de muestra simultánea de cuatro canales y 24 bits. El AD7768-4 se reconfigura con modos de potencia seleccionables y opciones de filtro digital para adaptarse a una amplia gama de aplicaciones, incluidos los ECG, módulos industriales de entrada/salida, instrumentación, pruebas de audio, bucles de control y monitoreo de condición.

Medición del desempeño

El ADA4945-1 tiene dos modos totalmente característicos de máxima potencia y baja potencia, lo que optimiza las compensaciones entre la potencia del sistema y el rendimiento. El ancho de banda de máxima potencia del ADA4945-1 es de 145 MHz (megahercios), mientras que en el modo de baja potencia el ancho de banda es de 80 MHz. Con una fuente de alimentación de 5 voltios, el ruido del voltaje de entrada a 100 kHz en el modo de máxima potencia es de 1.8 nV/√Hz frente a 3 nV/√Hz en el modo de baja potencia. Finalmente, la corriente de reposo operativa del ADA4945-1 en modo de máxima potencia es de 4 mA (miliamperios) (típico) y 4.2 mA (máximo). En modo de baja potencia, es de 1.4 mA (típico) y 1.6 mA (máximo).

El modo de baja potencia del AD7768-4 ofrece una velocidad de ODR (datos de salida) de 32 kSPS (kilosamples por segundo) y 12.8 kHz de ancho de banda cuando se usa el filtro digital de banda ancha. La entrada de onda sinusoidal aplicada de 1 kHz es -0.5 dB (decibelios) de la escala completa. El modo de potencia media cuenta con una ODR de 128 kSPS con 51.2 kHz de ancho de banda cuando se usa el filtro de banda ancha. La señal de onda sinusoidal aplicada de entrada de 1 kHz es de −0.5 dB de la escala completa. El modo de potencia rápida proporciona una ODR de 256 kSPS con 102.4 kHz de ancho de banda cuando se usa el filtro de banda ancha La Tabla 2 (a continuación) muestra el rendimiento y el consumo de energía de las combinaciones de energía ADA4945-1 y AD7768-4.

La respuesta configurada del filtro AD7768-4 tiene una frecuencia de corte de 0.433 × ODR. Una ondulación de banda de paso de ±0.005 dB permite que las mediciones del dominio de frecuencia determinen los amplificadores de accionamiento frente al rendimiento de la frecuencia de entrada.

En la Figura 5, hay una red de R/C entre la salida del amplificador y la entrada del ADC. La red de R/C realiza varias tareas. Por ejemplo, C1 y C2 son depósitos de carga del ADC y proporcionan al ADC una corriente de carga rápida para los condensadores de muestra.

Además, estos condensadores en combinación con la resistencia RIN forman un filtro de paso bajo para eliminar fallas relacionadas con la conmutación de entrada. La resistencia de entrada también estabiliza el amplificador cuando se manejan grandes cargas capacitivas y evita que el amplificador oscile (Tabla 1).

|

Tabla 1: Valores apropiados para RIN, C1 y C2. (Fuente de los datos: Analog Devices)

Con el sistema de la Figura 5, este dispositivo de evaluación produce una relación SNR (señal/ruido) de 106.7 dB y una THD (distorsión armónica total) de −114.8 dB con un subsistema de nivel de potencia tan bajo como 18.45 mW (milivatios) ( Tabla 2).

|

Tabla 2: Comparación de rendimiento mediante una combinación de dos modos del amplificador ADA4945-1 y tres modos del ADC AD7768-4. (Fuente de los datos: Analog Devices)

La SNR de la combinación amplificador operacional/ADC muestra que la resolución del sistema es la siguiente:

Resolución = (SNR - 1.76)/6.02

= 17.43 bits

Este amplificador de ADC de alta resolución y la combinación del ADC Σ-Δ producen una salida precisa y eliminan por completo la necesidad de procesamiento posterior.

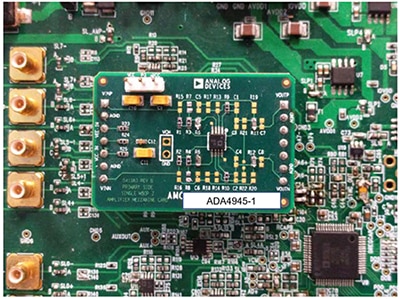

Para evaluar el hardware, los diseñadores pueden usar la placa de evaluación EVAL-AD7768-4FMCZ con el AD7768-4 y una AMC (tarjeta intermedia del amplificador) que lleva el ADA4945-1 (Figura 6).

Figura 6: La placa de evaluación EVAL-AD7768-4FMCZ para el AD7768-4 se puede usar para probar el diseño al agregar una AMC poblada por el ADA4945-1. (Fuente de la imagen: Analog Devices con leyenda ADA4945-1 añadida por DigiKey para mayor claridad)

Figura 6: La placa de evaluación EVAL-AD7768-4FMCZ para el AD7768-4 se puede usar para probar el diseño al agregar una AMC poblada por el ADA4945-1. (Fuente de la imagen: Analog Devices con leyenda ADA4945-1 añadida por DigiKey para mayor claridad)

Esta plataforma de evaluación se puede configurar para usar una tarjeta intermedia AMC-ADA4500-2ARMZ para controladores de ADC, de un solo canal, como entrada del controlador de amplificador. La placa de evaluación de diseño de alta velocidad EVAL-SDP-CH1Z se conecta a la plataforma de evaluación EVAL-AD7768-4FMCZ para utilizar el software de evaluación suministrado. Se utiliza una fuente de audio de precisión para el análisis AC.

Conclusión

Los ECG de alta resolución pueden detectar de forma no invasiva anomalías cardíacas que de otra manera pasarían desapercibidas o tienen indicadores que requerirían procedimientos de detección invasivos o mínimamente invasivos. Sin embargo, la resolución requerida para estos ECG puede verse comprometida por el ruido y otros inhibidores de rendimiento en el detector de ECG, el sistema del detector e incluso por la técnica de adquisición.

Como se explica, los diseñadores pueden evitar muchos problemas y desarrollar un ECG de alta precisión y de alta resolución combinando de forma eficaz el controlador de ADC de alta velocidad totalmente diferencial ADA4945-1ACPZ-R7 de Analog Devices y el ADC AD7768BSTZ de ocho canales y 24 bits de Analog Devices. La combinación también crea circuitos de filtrado búfer/digital que eliminan la necesidad de equipos de procesamiento posterior.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.