Cómo ahorrar espacio y tiempo de desarrollo al diseñar sistemas de adquisición de datos de precisión

Colaboración de Editores de DigiKey de América del Norte

2022-03-16

Los diseñadores de sistemas para la automatización industrial y la atención sanitaria emplean cada vez más la tecnología avanzada de detección y captura de imágenes y videos para su digitalización y análisis. Sin embargo, el análisis solo es tan bueno como los datos de entrada, cuya adquisición depende de bloques de conversión y acondicionamiento de señales precisos, estables, de rango altamente dinámico y de alto rendimiento. El diseño de estos bloques mediante métodos de circuitos discretos requiere considerables recursos de diseño, espacio en la placa y tiempo, todo lo cual se suma al costo total.

Al mismo tiempo, los diseñadores tienen que asegurarse de que sus sistemas finales sigan siendo competitivos, lo que significa reducir el costo y el tiempo de comercialización en la medida de lo posible, al tiempo que se garantiza un rendimiento excepcional.

Este artículo describe brevemente un sistema típico de adquisición de datos y sus elementos básicos. A continuación, presenta un módulo de adquisición de datos (DAQ) de Analog Devices Inc. que integra muchos de esos elementos críticos para proporcionar un rendimiento estable de 18 bits y 2 megamuestras por segundo (MS/s). También se presenta una placa de evaluación para ayudar a los diseñadores a familiarizarse con el módulo y su uso.

Elementos de un sistema DAQ

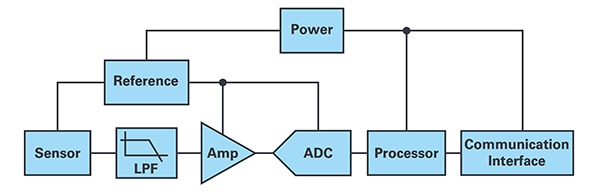

En la figura 1 se muestra un sistema típico de adquisición de datos. La señal de interés es captada por un sensor que emite una señal eléctrica en respuesta a algún fenómeno físico. Las salidas del sensor pueden ser no balanceadas o diferenciales y pueden requerir algún tipo de acondicionamiento de señales, como el filtrado. Para obtener el máximo rango dinámico posible del convertidor de analógico a digital (ADC), la señal debe amplificarse para ajustarse al rango de voltaje de entrada del ADC. La ganancia y la compensación del amplificador se controlan generalmente mediante resistencias de precisión que deben ser cuidadosamente ajustadas según consideraciones dinámicas y de desviación de la temperatura. Las dependencias de la temperatura suelen requerir que los componentes estén muy cerca físicamente. Las condiciones dinámicas incluyen niveles de ruido y distorsión que deben minimizarse.

Figura 1: Un sistema DAQ típico adquiere datos de un sensor, los acondiciona, optimiza la amplitud de la señal aplicada al ADC y comunica los datos digitales al procesador del sistema. (Fuente de la imagen: Analog Devices).

Figura 1: Un sistema DAQ típico adquiere datos de un sensor, los acondiciona, optimiza la amplitud de la señal aplicada al ADC y comunica los datos digitales al procesador del sistema. (Fuente de la imagen: Analog Devices).

El ADC de registro de aproximaciones sucesivas (SAR) debe tener un rango dinámico suficiente, indicado por el número de bits de resolución. También requiere una referencia de voltaje con búfer, estable y limpia.

Por último, los datos adquiridos deben ser accesibles a través de una interfaz de comunicaciones. La implementación de un sistema de adquisición de datos de este tipo mediante componentes discretos requiere más espacio físico y suele dar lugar a un rendimiento mucho menor que el obtenido con un dispositivo integrado. Como ejemplo, considere que los requisitos de rendimiento de un amplificador diferencial para manejar un ADC son tales que debe tener las resistencias de entrada y retroalimentación en ambas patas de la entrada del amplificador estrechamente emparejadas, ya que cualquier desequilibrio disminuirá la relación de rechazo al modo común (CMRR). Del mismo modo, las resistencias de entrada deben ajustarse con precisión a las resistencias de retroalimentación para establecer la ganancia de la etapa. Estas resistencias también deben hacer un seguimiento de la temperatura, lo que requiere que estén situadas cerca unas de otras. Además, el diseño general del circuito es fundamental para preservar la integridad de la señal y minimizar la respuesta parasitaria.

El módulo DAQ integrado ahorra tiempo y espacio

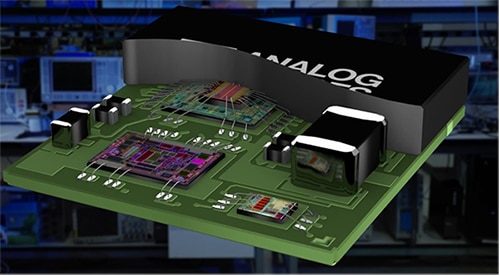

Para cumplir los requisitos de rendimiento y reducir al mismo tiempo el tamaño y el tiempo de diseño, los diseñadores pueden utilizar el Sistema en paquete (SIP) del ADAQ4003BBCZ µModule de Analog Devices como alternativa a las implementaciones discretas (Figura 2). Con unas dimensiones de 7 x 7 milímetros (mm), el ADAQ4003 se centra en la integración de las secciones más comunes de una cadena de señales, lo que incluye el acondicionamiento de señales y la digitalización, para ofrecer una solución de cadena de señales más completa con un rendimiento avanzado. De este modo, llena el vacío existente entre los componentes discretos estándar y los CI altamente integrados y específicos del cliente para resolver las necesidades de adquisición de datos.

Figura 2: Vista en corte de un SIP µModule que combina varios bloques de procesamiento de señales comunes en un único dispositivo de solo 7 mm de lado. (Fuente de la imagen: Analog Devices).

Figura 2: Vista en corte de un SIP µModule que combina varios bloques de procesamiento de señales comunes en un único dispositivo de solo 7 mm de lado. (Fuente de la imagen: Analog Devices).

El ADAQ4003 combina un ADC SAR de alta resolución de 18 bits que funciona a una velocidad de hasta 2 MS/s, un amplificador controlador de ADC (FDA) de bajo ruido y totalmente diferencial, un búfer de referencia de voltaje estable y todos los dispositivos pasivos críticos necesarios. Su pequeño paquete de matriz de malla de bolas (BGA) de 49 contactos cumple los requisitos de factor de forma compacto.

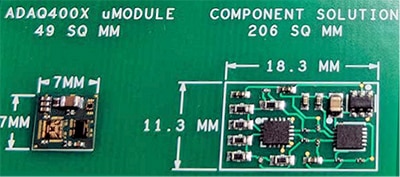

El ADAQ4003 ofrece una reducción de más de cuatro veces (4x) en el área de la placa de CI en comparación con un diseño discreto, como se muestra en la Figura 3.

Figura 3: El ADAQ4003 (a la izquierda) con la tapa retirada en comparación con un circuito idéntico instalado con componentes discretos ocupa menos de una cuarta parte de la superficie. (Fuente de la imagen: Analog Devices).

Figura 3: El ADAQ4003 (a la izquierda) con la tapa retirada en comparación con un circuito idéntico instalado con componentes discretos ocupa menos de una cuarta parte de la superficie. (Fuente de la imagen: Analog Devices).

Las ventajas del µModule en comparación con la implementación discreta son muchas. Espacio más pequeño, los componentes están físicamente cerca para un mejor seguimiento de la temperatura, así como la reducción de los efectos parásitos debido a la inductancia de la conexión y la capacitancia parásita.

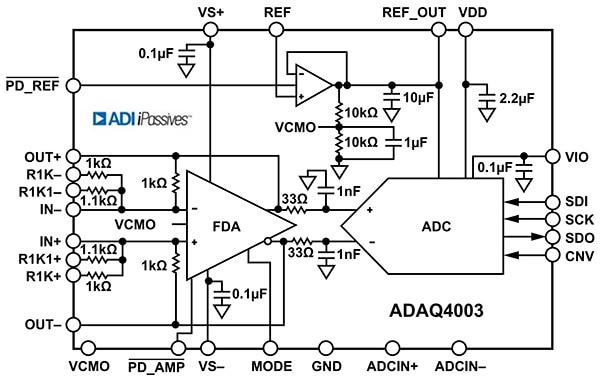

El diagrama de bloques funcional del ADAQ4033 muestra los cuatro componentes clave que se encuentran en todo sistema de adquisición de datos (Figura 4).

Figura 4: El diagrama de bloques funcional del ADAQ4003 muestra todo lo que cabe en su paquete BGA de 7 x 7 mm y 49 contactos. (Fuente de la imagen: Analog Devices).

Figura 4: El diagrama de bloques funcional del ADAQ4003 muestra todo lo que cabe en su paquete BGA de 7 x 7 mm y 49 contactos. (Fuente de la imagen: Analog Devices).

A pesar de su pequeño tamaño físico, el ADAQ4003 incorpora los componentes pasivos críticos mediante la tecnología iPassives de Analog Devices. Los pasivos integrados se fabrican en sustratos en los que se producen múltiples redes pasivas al mismo tiempo. En el proceso de fabricación se producen estas piezas con gran precisión. Por ejemplo, los componentes de la matriz de resistencias se ajustan con una precisión del 0.005 %. Los componentes adyacentes, separados por un espacio muy estrecho, se ajustan bien según el valor inicial, sin duda mucho mejor que los pasivos discretos. Al implementarse en un sustrato común, los valores de los componentes también harán un mejor seguimiento de temperatura, tensión mecánica y avance de la vida útil debido a la estructura integrada del componente.

Como ya se ha mencionado, el ADC SAR de 18 bits puede tener una velocidad de reloj de hasta 2 MS/s, pero funciona sin estados de código perdidos. El valor preciso y la adaptación de los componentes pasivos garantizan un excelente rendimiento del ADC. Tiene una relación típica de señal-ruido y distorsión (SINAD) de 99 decibelios (dB) con un ajuste de ganancia de 0.454. Su no linealidad integral suele ser de 3 partes por millón (ppm). La matriz de resistencias de entrada se puede conectar con pines, lo que permite ajustar la ganancia a 0.454, 0.909, 1.0 o 1.9 para adaptar la entrada al rango de escala completa del ADC, maximizando así su rango dinámico. La adaptación de los componentes críticos da como resultado una desviación del error de ganancia de ± 0.5 ppm/C° y una desviación del error de compensación de 0.7 ppm/C° en el rango de ganancia de 0.454.

El bloque ADC está precedido por el controlador FDA con una CMRR de 90 dB en todos los rangos de ganancia en la configuración diferencial. El amplificador tiene un rango de entrada en modo común muy amplio que depende de las configuraciones específicas del circuito y de los ajustes de ganancia. El FDA puede utilizarse como amplificador diferencial, pero también puede realizar la conversión de no balanceado a diferencial para entradas no balanceadas.

Hay un filtro RC unipolar, implementado diferencialmente usando componentes internos entre el controlador FDA y el ADC. Está diseñado para limitar el ruido en las entradas del ADC y reducir el efecto de los retrocesos de voltaje procedentes de la entrada del convertidor de digital a analógico (DAC) capacitivo de un ADC SAR.

El ADAQ4003 también alberga un búfer de referencia configurado con ganancia unitaria para controlar de forma óptima la impedancia de entrada dinámica del nodo de referencia del ADC SAR. También se incluyen todos los condensadores de desacoplamiento necesarios para el nodo de referencia de voltaje y los suministros de energía. Estos condensadores de desacoplamiento presentan una resistencia en serie equivalente (ESR) baja y una inductancia en serie equivalente (ESL) baja. El hecho de que sean internos en el ADAQ4003 permite simplificar aun más la lista de materiales (BOM).

La interfaz digital del ADAQ4003 utiliza una interfaz periférica serial (SPI) que es compatible con DSP, MICROWIRE y QSPI. Con un suministro VIO independiente, la interfaz de salida es compatible con la lógica de 1.8 voltios, 2.5 voltios, 3 voltios o 5 voltios.

El ADAQ4003 funciona con una baja disipación de potencia total —solo 51.5 milivatios (mW) a la máxima velocidad de reloj de 2 MS/s— y con una menor disipación de potencia a velocidades de reloj inferiores.

El diseño físico del ADAQ4003 ayuda a los diseñadores a mantener la integridad de la señal y el rendimiento mediante la separación de las señales analógicas y digitales. La distribución de pines tiene señales analógicas a la izquierda y señales digitales a la derecha, lo que permite a los diseñadores aislar las secciones analógicas y digitales sensibles para minimizar cualquier cruce.

Modelos de circuitos

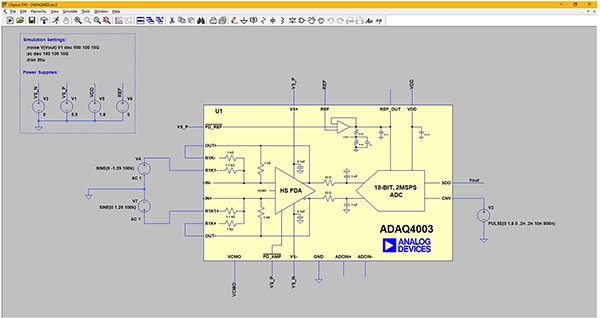

Analog Devices pone a disposición modelos de simulación, lo que proporciona un modelo para el ADAQ4003 en su simulador gratuito LTspice. Además, pone a disposición de otros simuladores de circuitos comerciales un modelo IBIS.

LTspice incluye un circuito de referencia básico con ADAQ4003, mostrado en la Figura 5. El dispositivo se utiliza en una configuración de entrada diferencial, y las resistencias de entrada están atadas para ajustar la ganancia del FDA a 0.454, lo que pone las resistencias de entrada de 1.0 y 1.1 kilohmios (kΩ) en serie. El ajuste del voltaje de referencia del modelo es de 5 voltios y utiliza un reloj de conversión de 2 MS/s.

Figura 5: ADI pone a disposición modelos de simulación LTspice para el ADAQ4003 con una configuración de entrada diferencial. (Fuente de la imagen: Art Pini)

Figura 5: ADI pone a disposición modelos de simulación LTspice para el ADAQ4003 con una configuración de entrada diferencial. (Fuente de la imagen: Art Pini)

El modelo LTspice es un punto de partida para cualquier diseño que puede verificarse posteriormente utilizando una placa de evaluación.

Placas de evaluación de VCO

Al considerar el ADAQ4003, es aconsejable probarlo con la placa de evaluación EVAL-ADAQ4003FMCZ. Este juego de placas múltiples incluye la placa de evaluación y una tarjeta mezzanine de matriz programable en campo. Funcionan con la plataforma de demostración del sistema EVAL-SDP-CH1Z de Analog Devices. ADI también provee el software de demostración de Análisis/Control/Evaluación (ACE) con complementos específicos para cada producto, lo que permite al usuario realizar pruebas detalladas del producto, incluido el análisis armónico y las mediciones de no linealidad integral y diferencial.

Conclusión:

Para los diseñadores que tienen que desarrollar rápidamente sistemas DAQ de alto rendimiento manteniendo el tamaño y el costo al mínimo, el ADAQ4003 µModule es una buena opción. El dispositivo reduce el ciclo de desarrollo de un sistema de medición de precisión al eliminar los retos de diseño de la cadena de señales en la selección, la optimización y la disposición de componentes discretos. El ADAQ4003 simplifica aun más el proceso de diseño al proporcionar un único componente con una solución de adquisición de datos optimizada y eficiente en términos de espacio como base para un diseño personalizado.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.