NXP Semiconductors ofrece la serie LPC80x que consta de una rentable familia de MCU de 32 bits basados en Arm Cortex-M0+, capaces de operar a frecuencias de CPU de hasta 15 MHz. La familia LPC80x forma parte de la plataforma de computación de borde EdgeVerse™ de NXP. La familia de MCU LPC80x admite hasta 32 KB de memoria Flash y hasta 4 KB de SRAM.

NXP Semiconductors ofrece la serie LPC80x que consta de una rentable familia de MCU de 32 bits basados en Arm Cortex-M0+, capaces de operar a frecuencias de CPU de hasta 15 MHz. La familia LPC80x forma parte de la plataforma de computación de borde EdgeVerse™ de NXP. La familia de MCU LPC80x admite hasta 32 KB de memoria Flash y hasta 4 KB de SRAM.

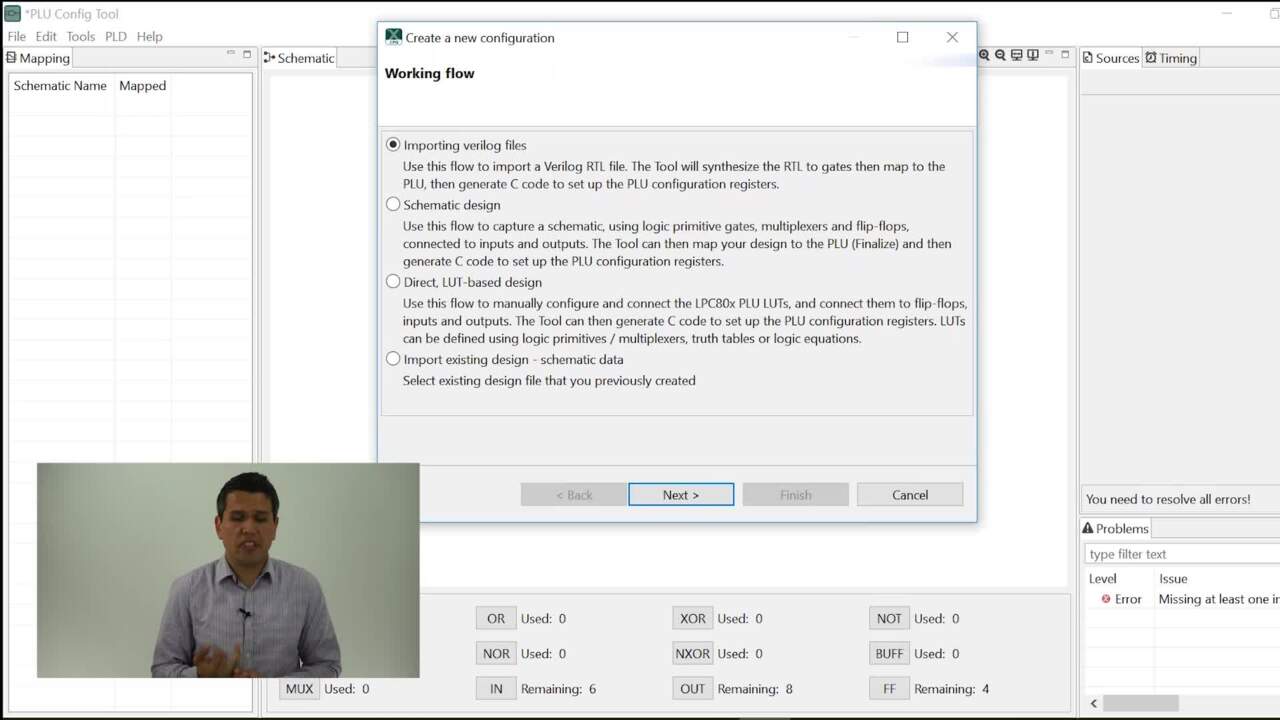

Esta familia cuenta con un consumo de energía optimizado, una pequeña huella en paquetes populares y opciones de nivel de desplazamiento gracias a sus carriles de alimentación separados. El complemento periférico de la serie LPC80x incluye un motor de CRC, interfaces de bus I2C, hasta dos USART, un SPI, interfaz táctil capacitiva, un temporizador de índice múltiple, un temporizador de autoactivación, un contador/temporizador de propósito general de 32 bits, un ADC de 12 bits, un DAC de 10 bits, un comparador analógico, puertos de E/S de función configurable a través de una matriz de interruptor, un motor de combinación modelo de entrada, unidad lógica programable (PLU) y hasta 30 pines de E/S para fines generales.

| Características |

- Sistema

- Procesador Arm Cortex-M0+ (revisión r0p1), que se ejecuta a frecuencias de hasta 15 MHz con multiplicador de ciclo simple y puerto de E/S de ciclo simple rápido; controlador de interrupciones vectorizadas y anidadas (NVIC) integrado.

- Contador de ticks de sistema

- Matriz de múltiples capas AHB

- Depurador de Cable Serial (SWD) con cuatro puntos de interrupción y dos puntos de vigilancia; soporte de JTAG de lenguaje de descripción de exploración de límite (BSDL)

- Periféricos digitales

- Interfaz GPIO de alta velocidad de conectada al bus de E/S Arm Cortex-M0+ con hasta 30 pines GPIO con resistencias de polarización configurables, modo de drenaje abierto programable e inversor de entrada; el control de dirección de GPIO apoya el ajuste independiente/borrado/conmutación de bits individuales

- Controlador de salida de fuente de alta corriente (20 mA) en tres pines

- Capacidad de generación de interrupción GPIO con función booleana de coincidencia en ocho entradas de GPIO (LPC804)

- Matriz de conmutador para la configuración flexible de cada función pin E/S

- Motor de CRC

- Capacidad táctil (LPC804)

- PLU para crear pequeñas redes de lógica combinatoria y secuencial como máquinas de estado simple (LPC804)

|

|

- Soporte ROM API

- Arranque del cargador

- Soporte para Flash en programación en aplicaciones (IAP)

- Apoya la programación en el sistema (ISP) a través de USART

- API ROM en chip para dividir enteros

- API de oscilador de libre ejecución FRO)

- Memoria

- Memoria de programación Flash de 32 KB en el chip

- Protección de lectura de código (CRP)

- Hasta 4 KB de SRAM

- Potencia de E/S doble (LPC802M011JDH20, LPC804M111JDH24):

- Fuentes independientes a cada lado del paquete que permiten cambiar de nivel señales desde un dominio de tensión fuera de chip a otro y/o conectarse directamente a periféricos fuera del chip que operan a diferentes niveles de suministro

|

| Aplicaciones |

- Puertas de enlace de sensores

- Industrial

- Controladores de juegos de azar

- Aplicaciones de 8 a 16 bits

- Aplicaciones de consumo

|

|

- Controles de clima

- Controles del motor

- Accesorios personales y portátiles

- Descargas eléctricas

- Aplicaciones de seguridad y de incendios

|

![]() NXP Semiconductors ofrece la serie LPC80x que consta de una rentable familia de MCU de 32 bits basados en Arm Cortex-M0+, capaces de operar a frecuencias de CPU de hasta 15 MHz. La familia LPC80x forma parte de la plataforma de computación de borde EdgeVerse™ de NXP. La familia de MCU LPC80x admite hasta 32 KB de memoria Flash y hasta 4 KB de SRAM.

NXP Semiconductors ofrece la serie LPC80x que consta de una rentable familia de MCU de 32 bits basados en Arm Cortex-M0+, capaces de operar a frecuencias de CPU de hasta 15 MHz. La familia LPC80x forma parte de la plataforma de computación de borde EdgeVerse™ de NXP. La familia de MCU LPC80x admite hasta 32 KB de memoria Flash y hasta 4 KB de SRAM.