La familia FPGA Cyclone 10 LP de Altera ofrece un equilibrio óptimo entre rentabilidad, bajo consumo de energía y rendimiento fiable, lo que la convierte en una excelente opción para aplicaciones sensibles a la energía como la automatización industrial, los sistemas automotrices y los dispositivos de IoT. Estas FPGA ofrecen hasta 120,000 elementos lógicos, admiten múltiples estándares de voltaje e integran funciones esenciales como memoria integrada, PLL, bloques DSP y terminación en chip (OCT) para una integridad de señal superior. La gestión avanzada de la energía con opciones de voltaje del núcleo de 1,2 V y 1,0 V garantiza un funcionamiento eficiente desde el punto de vista energético, mientras que las robustas redes de sincronización y la mitigación de SEU mejoran la fiabilidad del sistema. Las FPGA Cyclone 10 LP, compatibles con hot-socketing para una integración perfecta y configuraciones de E/S flexibles, ofrecen a los diseñadores una solución escalable y rentable sin comprometer el rendimiento, lo que las hace ideales para aplicaciones integradas sencillas y complejas.

La familia FPGA Cyclone 10 LP de Altera ofrece un equilibrio óptimo entre rentabilidad, bajo consumo de energía y rendimiento fiable, lo que la convierte en una excelente opción para aplicaciones sensibles a la energía como la automatización industrial, los sistemas automotrices y los dispositivos de IoT. Estas FPGA ofrecen hasta 120,000 elementos lógicos, admiten múltiples estándares de voltaje e integran funciones esenciales como memoria integrada, PLL, bloques DSP y terminación en chip (OCT) para una integridad de señal superior. La gestión avanzada de la energía con opciones de voltaje del núcleo de 1,2 V y 1,0 V garantiza un funcionamiento eficiente desde el punto de vista energético, mientras que las robustas redes de sincronización y la mitigación de SEU mejoran la fiabilidad del sistema. Las FPGA Cyclone 10 LP, compatibles con hot-socketing para una integración perfecta y configuraciones de E/S flexibles, ofrecen a los diseñadores una solución escalable y rentable sin comprometer el rendimiento, lo que las hace ideales para aplicaciones integradas sencillas y complejas.

- Rentabilidad: bajo costo por E/S y LE (elemento lógico) con una gama de densidades de dispositivos

- Muy bajo consumo: fabricado mediante un proceso de optimización de potencia ajustado para una baja potencia estática y adecuado para aplicaciones sensibles a la potencia que necesitan un alto rendimiento.

- Doble fuente de alimentación: solo se necesitan dos rieles de voltaje en el núcleo, lo que reduce el costo y el espacio de la placa

- Paquetes de formato reducido: facilita el diseño de la placa y reduce el costo total de propiedad.

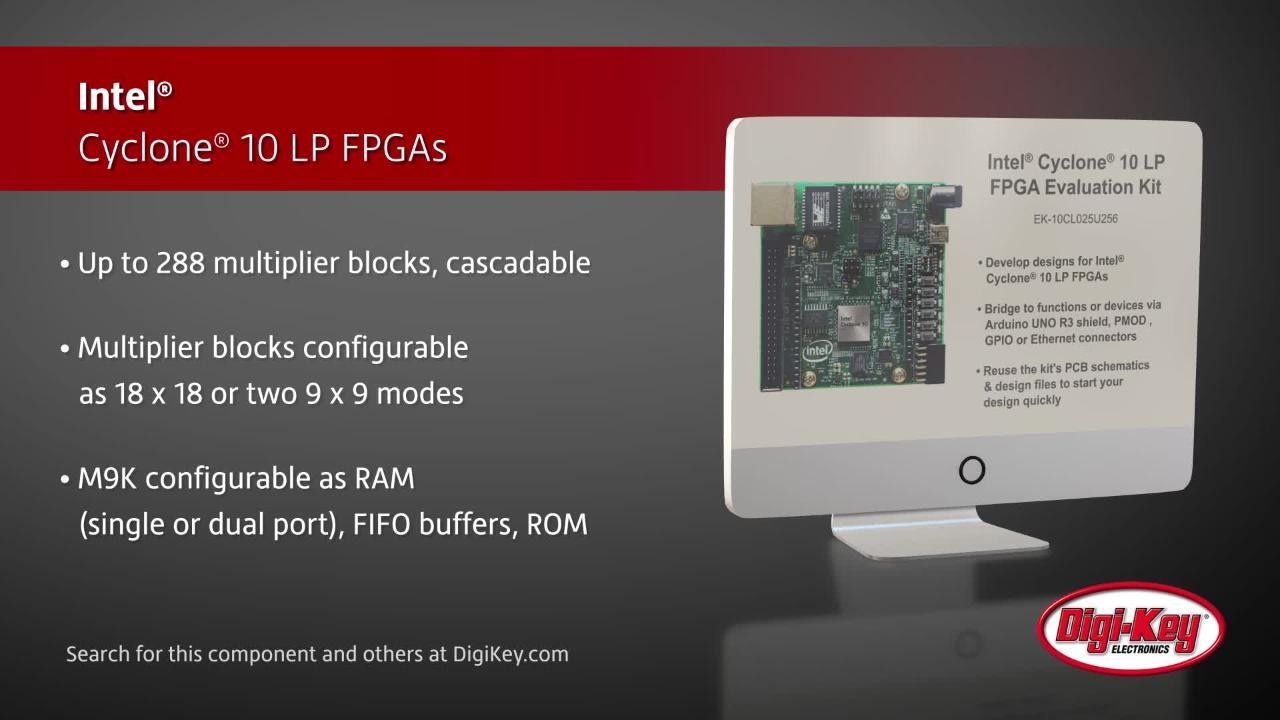

- Funciones aritméticas más rápidas con multiplicadores integrados: incluye multiplicadores endurecidos de 18 bits x 18 bits, lo que aumenta el rendimiento y la asequibilidad, al mismo tiempo que reduce los requisitos de potencia y lógica

Características

- Opciones de voltaje de base de 1.0 V y 1.2 V

- Elementos lógicos (LE): tabla de consulta de cuatro entradas (LUT) y registro

- Interconexión metálico/enrutamiento abundante entre todos los LE

- M9K: 9 Kb de bloques de memoria SRAM integrados, en cascada

- Un modo multiplicador de 18 × 18 o dos modos 9 × 9, en cascada

- Hasta 15 pines de reloj dedicados que pueden impulsar hasta 20 relojes globales

- Hasta cuatro PLL de propósito general

- Transmisores y receptores de LVDS verdadero y LVDS emulado

La familia FPGA Cyclone 10 LP de Altera ofrece un equilibrio óptimo entre rentabilidad, bajo consumo de energía y rendimiento fiable, lo que la convierte en una excelente opción para aplicaciones sensibles a la energía como la automatización industrial, los sistemas automotrices y los dispositivos de IoT. Estas FPGA ofrecen hasta 120,000 elementos lógicos, admiten múltiples estándares de voltaje e integran funciones esenciales como memoria integrada, PLL, bloques DSP y terminación en chip (OCT) para una integridad de señal superior. La gestión avanzada de la energía con opciones de voltaje del núcleo de 1,2 V y 1,0 V garantiza un funcionamiento eficiente desde el punto de vista energético, mientras que las robustas redes de sincronización y la mitigación de SEU mejoran la fiabilidad del sistema. Las FPGA Cyclone 10 LP, compatibles con hot-socketing para una integración perfecta y configuraciones de E/S flexibles, ofrecen a los diseñadores una solución escalable y rentable sin comprometer el rendimiento, lo que las hace ideales para aplicaciones integradas sencillas y complejas.

La familia FPGA Cyclone 10 LP de Altera ofrece un equilibrio óptimo entre rentabilidad, bajo consumo de energía y rendimiento fiable, lo que la convierte en una excelente opción para aplicaciones sensibles a la energía como la automatización industrial, los sistemas automotrices y los dispositivos de IoT. Estas FPGA ofrecen hasta 120,000 elementos lógicos, admiten múltiples estándares de voltaje e integran funciones esenciales como memoria integrada, PLL, bloques DSP y terminación en chip (OCT) para una integridad de señal superior. La gestión avanzada de la energía con opciones de voltaje del núcleo de 1,2 V y 1,0 V garantiza un funcionamiento eficiente desde el punto de vista energético, mientras que las robustas redes de sincronización y la mitigación de SEU mejoran la fiabilidad del sistema. Las FPGA Cyclone 10 LP, compatibles con hot-socketing para una integración perfecta y configuraciones de E/S flexibles, ofrecen a los diseñadores una solución escalable y rentable sin comprometer el rendimiento, lo que las hace ideales para aplicaciones integradas sencillas y complejas.