Estándares de voltaje de E/S y su papel para garantizar que los microcontroladores hablen el mismo idioma

Imagine que intenta comunicarse con un extranjero en su idioma nativo (Figura 1), solo para darse cuenta de que no solo no lo entiende, sino que el "sí" que usted dice en realidad significa "no" en su idioma. Esto es exactamente lo que sucede cuando dos circuitos integrados (CI) con estándares de E/S incompatibles intentan comunicarse. El resultado es confusión en el mejor de los casos y daños en el hardware en el peor.

Figura 1: Imagen generada por IA que simboliza la confusión de usar diferentes estándares de E/S. (Fuente: generado por IA)

Figura 1: Imagen generada por IA que simboliza la confusión de usar diferentes estándares de E/S. (Fuente: generado por IA)

Los microcontroladores funcionan en lógica binaria de 0 y 1. Hay rangos de voltaje que corresponden a estos niveles lógicos. Por ejemplo, un microcontrolador puede leer un '0' lógico como cualquier cosa inferior a 0.3 V, y un '1' como cualquier cosa que sea superior a 2.7 V y tan alta como 3.3 V. Pero el otro microcontrolador puede leer un '1' como cualquier cosa que comience en 1.2 V y sea tan alto como 1.8 V. Si el primer microcontrolador envía una señal de 3,3 V al segundo (Figura 2), podría exceder la tolerancia de voltaje del dispositivo receptor, lo que podría causar daños permanentes.

Figura 2: Representación de dos circuitos integrados de estándares de E/S incompatibles que se comunican. (Fuente: generado por IA)

Figura 2: Representación de dos circuitos integrados de estándares de E/S incompatibles que se comunican. (Fuente: generado por IA)

Esta es la razón por la que comprender y administrar la compatibilidad de voltaje de E/S es fundamental en el diseño de sistemas integrados. Sin un cambio de nivel adecuado o una traducción de voltaje, incluso una simple conexión entre dos chips puede provocar un comportamiento impredecible o una falla de hardware.

La función de los estándares de voltaje de E/S

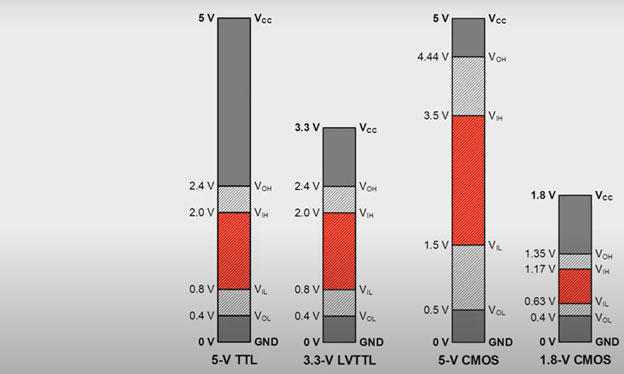

Los estándares de voltaje de E/S definen los niveles de voltaje aceptables para las señales lógicas digitales. Especifica lo que constituye un máximo lógico (1) o un mínimo (0). Estos estándares garantizan que los dispositivos puedan interpretar de manera correcta las señales y responder adecuadamente. Sin un estándar comúnmente acordado sobre estos niveles, los dispositivos pueden leer mal las señales o no comunicarse entre sí.

Terminologías definidas por las normas:

- VIH (voltaje de entrada alto): Voltaje mínimo reconocido como un alto lógico.

- VIL (voltaje de entrada bajo): Voltaje máximo reconocido como un bajo lógico.

- VOH (voltaje de salida bajo): Salida de voltaje mínimo como un alto lógico.

- VOL (voltaje de salida bajo): Salida de voltaje máximo como un bajo lógico.

Para una comunicación exitosa, los niveles de salida de un dispositivo deben estar dentro del rango de entrada aceptable del dispositivo receptor.

Estándares de E/S de un solo extremo

Los estándares de entrada-salida (SIO) de un solo extremo (Figura 3) son uno de los estándares de entrada-salida (E/S) más populares. Utilizan un solo cable referenciado a una puesta a tierra común para la transferencia de señales. Cuando se trata de diseños de menor velocidad y baja complejidad, los SIO son una alternativa rentable y más simple en comparación con los estándares de señalización diferencial, que utilizan dos señales complementarias.

El semiconductor complementario de óxido metálico de bajo voltaje (LVCMOS) es un estándar común de un solo extremo, a menudo denominado LVMOS en algunos contextos. LVCMOS generalmente funciona en 1.8 V, 2.4 V o 3.3 V y define umbrales específicos para máximos y mínimos lógicos. La simplicidad relacionada con los estándares SIO tiene un costo, los SIO como LVCMOS son susceptibles al ruido y la degradación de la señal a largas distancias o a altas frecuencias. Garantizar la compatibilidad de voltaje adecuada, utilizando desfasadores de nivel, es fundamental cuando se interactúa LVCMOS con dispositivos que operan en diferentes dominios de voltaje.

Figura 3: Niveles de voltaje de diferentes estándares de E/S. (Fuente: Texas Instruments)

Figura 3: Niveles de voltaje de diferentes estándares de E/S. (Fuente: Texas Instruments)

Desafíos en la interfaz de E/S

1. Desajuste de voltaje

El problema más común relacionado con los dispositivos de interfaz que funcionan a diferentes niveles de voltaje es el desajuste de voltaje. Por ejemplo, conectar una salida de 3.3 V a una entrada de 1.8 V sin cambio de nivel puede dañar el dispositivo de menor voltaje (Figura 2).

Para mitigar esto, se debe asegurar que los niveles de entrada de alto voltaje (VIH) y bajo voltaje de entrada (VIL) de un CI coincidan con los niveles de salida de voltaje alto (VOH) y salida de voltaje bajo (VOL) del otro.

2. Integridad de la señal

A altas velocidades, los reflejos, los timbres y la diafonía pueden corromper las señales. La terminación adecuada, la adaptación de impedancia y el enrutamiento de trazas son esenciales para mantener transiciones de señal limpias.

3. Dominios de la fuente de alimentación

En sistemas con múltiples rieles de voltaje, se debe tener cuidado de aislar o traducir señales entre dominios. Los desfasadores de nivel, los divisores de voltaje o las configuraciones de drenaje abierto con resistencias pull-up son soluciones comunes.

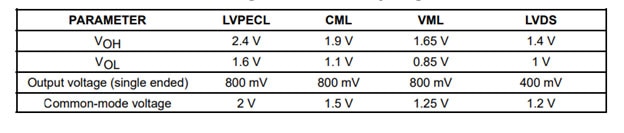

Familias lógicas avanzadas: LVPECL, CML, VML y LVDS

En los sistemas de comunicación de alta velocidad, se utilizan familias lógicas como LVPECL (Lógica de emisor acoplado de bajo voltaje y tensión positiva), CML (Lógica de modo de corriente) y VML (Lógica de modo de voltaje) (Tabla 1). Estos ofrecen transiciones más rápidas y una mejor inmunidad al ruido, pero requieren un diseño cuidadoso:

- LVPECL: Funciona alrededor de 3 V, con señalización diferencial y rendimiento de alta velocidad

- CML: Utiliza fuentes de corriente constante para una conmutación rápida y una baja fluctuación

- VML: Menos común, pero ofrece señalización en modo de voltaje con oscilación independiente de la carga

- LVDS: Ampliamente utilizado para señalización diferencial de velocidad moderada y baja potencia

Tabla 1: Parámetros de tensión por nivel lógico LVPECL, CML, VML y LVDS. (Fuente: Texas Instruments)

Tabla 1: Parámetros de tensión por nivel lógico LVPECL, CML, VML y LVDS. (Fuente: Texas Instruments)

Mejores prácticas para la interfaz de E/S

- Siempre verifique las hojas de datos para los valores VIH, VIL, VOH y VOL.

- Utilice desfasadores de nivel cuando interactúe entre dominios de voltaje.

- Pruebe temprano y con frecuencia con osciloscopios y analizadores lógicos.

La interfaz de E/S es más que solo conectar pines, se trata de garantizar que cada señal se entienda exactamente como se pretende. A medida que los sistemas integrados se vuelven más complejos y operan en múltiples dominios de voltaje y familias lógicas, dominar la compatibilidad de E/S se torna fundamental.

Al comprender los estándares de voltaje, anticipar los desajustes y aplicar las mejores prácticas, podemos diseñar sistemas sólidos y confiables que se comuniquen claramente sin errores de traducción. Sin embargo, si se requiere conectar los CI de diferentes estándares de E/S, una forma de mitigar el desajuste del nivel de la señal es mediante el uso de desfasadores de nivel.

Desfasador de nivel

Un desfasador de nivel (LS), (también conocido como traductor de voltaje), es un circuito utilizado en sistemas integrados para interactuar de manera segura entre componentes que operan a diferentes niveles de voltaje. Supongamos que un microcontrolador que funciona a 3.3 V necesita comunicarse con un sensor que funciona con una lógica de 1.8 V, el desfasador de nivel garantiza que las señales se traduzcan correctamente entre los dos, sin riesgo de daños o errores lógicos. Según el protocolo utilizado, los desfasadores de nivel se pueden clasificar como unidireccionales o bidireccionales. Los LS se implementan comúnmente utilizando MOSFET, circuitos integrados intermedios o chips traductores dedicados. Desempeñan un papel integral en el mantenimiento de la integridad de la señal y en la protección de componentes en entornos de voltaje mixto.

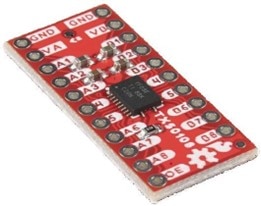

Figura 4: Módulo de desfasador de nivel de ocho canales. (Fuente: SparkFun)

Figura 4: Módulo de desfasador de nivel de ocho canales. (Fuente: SparkFun)

Recursos adicionales

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum