Por qué y cómo utilizar las FPGA Efinix para Imagen AI/ML Parte 2: Captura y Procesado de Imagen

Colaboración de Editores europeos de DigiKey

2023-05-05

Nota del editor: Los nuevos enfoques de las arquitecturas FPGA aportan un control más preciso y una mayor flexibilidad para responder a las necesidades del aprendizaje automático (ML) y la inteligencia artificial (AI). La primera parte de esta Serie en dos partes presenta una de estas arquitecturas de Efinix y cómo empezar a utilizarla con una placa de desarrollo. En la Parte 2 se analiza la interconexión de la placa de desarrollo con dispositivos y periféricos externos, como una cámara, y cómo aprovechar la FPGA para eliminar cuellos de botella en el procesamiento de imágenes.

Las FPGA desempeñan un papel fundamental en muchas aplicaciones, desde el control industrial y la seguridad hasta la robótica, la industria aeroespacial y la automoción. Gracias a la naturaleza flexible del núcleo lógico programable y a sus amplias capacidades de interconexión, un caso de uso cada vez más frecuente de las FPGA es el procesamiento de imágenes, donde puede desplegarse el aprendizaje automático (ML). Las FPGA son ideales para implementar soluciones que tienen varias interfaces de cámara de alta velocidad gracias a su estructura lógica paralela. Además, las FPGA también permiten utilizar un canal de procesamiento dedicado en la lógica, con lo que se eliminan los cuellos de botella de recursos compartidos que se asociarían a las soluciones basadas en CPU o GPU.

Este segundo vistazo a las FPGA Titanio de Efinix examinará la aplicación de procesamiento de imágenes de referencia que viene con la placa de desarrollo Ti180 M484 de la FPGA. El objetivo es comprender las partes constituyentes del diseño e identificar dónde la tecnología FPGA permite eliminar cuellos de botella o aporta otras ventajas a los desarrolladores.

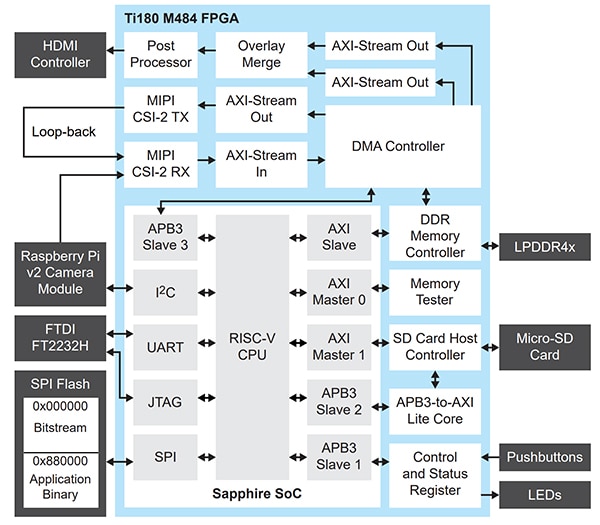

El diseño de referencia basado en Ti180 M484

Conceptualmente, el diseño de referencia (Figura 1) recibe imágenes de varias cámaras con interfaz de procesador industrial móvil (MIPI), realiza el búfer de fotogramas en LPDDR4x y, a continuación, envía las imágenes a una pantalla con interfaz multimedia de alta definición (HDMI). Se utiliza una tarjeta mezzanine FPGA (FMC) y cuatro interfaces Samtec QSE en la placa para proporcionar las entradas de la cámara y la salida HDMI.

Figura 1: Conceptualmente, el diseño de referencia Ti180 M484 recibe imágenes de varias cámaras MIPI, realiza el búfer de fotogramas en el LPDDR4x y, a continuación, emite las imágenes a una pantalla HDMI. >(Fuente de la imagen: Efinix)

Figura 1: Conceptualmente, el diseño de referencia Ti180 M484 recibe imágenes de varias cámaras MIPI, realiza el búfer de fotogramas en el LPDDR4x y, a continuación, emite las imágenes a una pantalla HDMI. >(Fuente de la imagen: Efinix)

La tarjeta de expansión FMC a QSE se utiliza junto con la tarjeta hija HDMI para proporcionar la ruta de vídeo de salida, mientras que los tres conectores QSE se utilizan para interactuar con las cámaras DFRobot SEN0494 MIPI. Si no se dispone de varias cámaras MIPI, se puede utilizar una sola cámara conectando en bucle el canal de una sola cámara para simular cámaras adicionales.

A primera vista, esta aplicación puede parecer sencilla. Sin embargo, recibir múltiples flujos MIPI de alta definición (HD) a una Velocidad de fotograma elevada es todo un reto. Aquí es donde la tecnología FPGA resulta beneficiosa porque permite a los diseñadores utilizar varios flujos MIPI en paralelo.

La arquitectura del diseño de referencia aprovecha las estructuras de procesamiento paralelo y secuencial con la FPGA. Las estructuras paralelas se utilizan para implementar el canal de procesamiento de imágenes, mientras que un procesador RISC-V proporciona el procesamiento secuencial utilizado para las tablas de consulta (LUT) de la FPGA.

En muchos sistemas de procesamiento de imágenes basados en FPGA, la cadena de procesamiento de imágenes puede dividirse en dos elementos: los flujos de entrada y de salida. El flujo de entrada se conecta a la interfaz cámara/sensor y las funciones de procesamiento se aplican a la salida del sensor. Estas funciones pueden incluir conversión Bayer, balance de blancos automático y otras mejoras. En el flujo de salida, la imagen se prepara para su visualización. Esto incluye el cambio de espacios de color (por ejemplo, de RGB a YUV) y el posprocesamiento para el formato de salida deseado, como HDMI.

A menudo, la cadena de procesamiento de imágenes de entrada funciona a la velocidad de reloj del píxel del sensor. Esto tiene una temporización diferente a la de la cadena de salida, que se procesa a la frecuencia de la pantalla de salida.

Se utiliza un búfer de trama para conectar la entrada con el canal de procesamiento de salida, que a menudo se almacena en una memoria externa de alto rendimiento, como LPDDR4x. Este búfer de trama se desacopla entre los canales de entrada y salida, lo que permite acceder al búfer de trama mediante un acceso directo a la memoria a la frecuencia de reloj adecuada.

El diseño de referencia Ti180 utiliza un enfoque similar a los conceptos expuestos anteriormente. El canal de procesamiento de imágenes de entrada implementa un núcleo de propiedad intelectual (IP) de receptor MIPI Camera Serial Interface 2 (CSI-2), que se basa en la capa física MIPI (MIPI D-PHY) de entrada/salida (E/S) de la FPGA Titanio. MIPI es una interfaz complicada porque utiliza señalización de un solo extremo y diferencial en el mismo par diferencial, además de comunicaciones de baja y alta velocidad. La integración de la MIPI D-PHY dentro de la E/S de la FPGA reduce la complejidad del diseño de la tarjeta de circuitos, así como la lista de materiales (BOM).

Una vez recibido el flujo de imágenes de la cámara, el diseño de referencia convierte la salida del MIPI CSI-2 RX en un flujo de Interfaz eXtensible avanzada (AXI). Un flujo AXI es una interfaz unidireccional de alta velocidad que proporciona un flujo de datos de un maestro a un esclavo. Se proporcionan señales de Handshaking para la transferencia entre un maestro y un esclavo (tvalid y tready) junto con señales de banda lateral. Estas señales de banda lateral pueden utilizarse para transmitir información de temporización de la imagen, como el inicio del fotograma y el final de línea.

AXI Stream es ideal para aplicaciones de procesamiento de imágenes y permite a Efinix proporcionar una gama de IP de procesamiento de imágenes que pueden integrarse fácilmente en la cadena de procesamiento según lo requiera la aplicación.

Tras su recepción, los datos de imagen MIPI CSI-2 y las señales de temporización se convierten en un flujo AXI y se introducen en un módulo de acceso directo a memoria (DMA), que escribe el fotograma de imagen en LPDDR4x y actúa como búfer del fotograma.

Este módulo DMA funciona bajo el control del núcleo RISC-V en la FPGA dentro de un sistema en chip (SoC) Sapphire. Este sistema en chip (SoC) proporciona control, como la detención y el inicio de las escrituras DMA, además de proporcionar al canal de escritura DMA la información necesaria para escribir correctamente los datos de imagen en LPDDR4x. Incluye información sobre la ubicación en memoria y la anchura y altura de la imagen definida en bytes.

El canal de salida del diseño de referencia lee la información de imagen del búfer de trama LPDDR4x bajo el control del sistema en chip (SoC) RISC-V. Los datos salen de la IP DMA como un flujo AXI, que se convierte del formato RAW proporcionado por el sensor al formato RGB (Figura 2), y se prepara para su salida a través del transmisor HDMI ADV7511 de Analog Devices.

Figura 2: Imágenes de muestra del diseño de referencia. (Fuente de la imagen: Adam Taylor)

Figura 2: Imágenes de muestra del diseño de referencia. (Fuente de la imagen: Adam Taylor)

El uso del DMA también permite al Sapphire SoC RISC-V acceder a las imágenes almacenadas en el búfer de fotogramas, así como a las estadísticas abstractas y a la información de la imagen. El sistema en chip (SoC) Sapphire también es capaz de escribir plantillas en LPDDR4x para fusionarlas con el flujo de video de salida.

Los modernos sensores de imagen CMOS (CIS) tienen varios modos de funcionamiento y pueden configurarse para proporcionar procesamiento en chip, así como varios formatos de salida y esquemas de sincronización diferentes. Esta configuración se realiza normalmente a través de una interfaz I²C. En el diseño de referencia de Efinix, el procesador Sapphire SoC RISC-V proporciona esta comunicación I²C a las cámaras MIPI.

La integración del procesador RISC-V dentro de la FPGA Titanio reduce el tamaño total de la solución final, ya que elimina la necesidad de implementar tanto complejas máquinas de estado FPGA que aumentan el riesgo de diseño, como procesadores externos que se suman a la lista de materiales.

La inclusión del procesador también permite la compatibilidad con IP adicionales para comunicarse con la tarjeta MicroSD. Esto permite aplicaciones reales en las que puede ser necesario almacenar imágenes para su posterior análisis.

En general, la arquitectura del diseño de referencia Ti180 está optimizada para ofrecer una solución compacta, de bajo coste y alto rendimiento que permita a los desarrolladores reducir el coste de la lista de materiales mediante la integración del sistema.

Una de las principales ventajas de los diseños de referencia es que pueden utilizarse para poner en marcha el desarrollo de aplicaciones en hardware personalizado, lo que permite a los desarrolladores tomar elementos críticos del diseño y basarse en ellos con las personalizaciones que necesiten. Esto incluye la posibilidad de utilizar el flujo TinyML de Efinix para implementar aplicaciones TinyML basadas en visión que se ejecuten en la FPGA. Esto puede aprovechar tanto la naturaleza paralela de la lógica FPGA como la capacidad de añadir fácilmente instrucciones personalizadas en los procesadores RISC-V, lo que permite la creación de aceleradores dentro de la lógica FPGA.

Implementación

Como se explica en la Parte 1, la arquitectura Efinix es única en el sentido de que utiliza celdas de lógica y enrutamiento intercambiables (XLR) para proporcionar funcionalidad tanto de enrutamiento como de lógica. Un sistema de video como el del diseño de referencia es un sistema mixto que requiere mucha lógica y mucho enrutamiento: se necesita mucha lógica para implementar las funciones de procesamiento de imágenes y mucho enrutamiento para conectar las células IP a las frecuencias necesarias.

El diseño de referencia utiliza aproximadamente el 42% de las celdas XLR del dispositivo, lo que deja un amplio margen para adiciones, incluidas aplicaciones personalizadas como ML de borde.

El uso de los bloques de RAM y Procesador de señal digital (DSP) también es muy eficiente, ya que solo se utilizan 4 de los 640 bloques DSP y el 40% de los bloques de memoria (Figura 3).

|

Figura 3: La asignación de recursos en la arquitectura Efinix muestra que solo se utiliza el 42% de las celdas XLR, lo que deja mucho espacio para procesos adicionales. (Fuente de la imagen: Adam Taylor)

En la E/S del dispositivo, la interfaz DDR para LPDDR4x se utiliza para proporcionar la memoria de aplicaciones para el SoC Sapphire y los búferes de fotogramas de imagen. Todos los recursos MIPI dedicados al dispositivo se utilizan junto con el 50% de los bucles de bloqueo de fase (Figura 4).

|

Figura 4: Instantánea de la interfaz y los recursos de E/S utilizados. (Fuente de la imagen: Adam Taylor)

La entrada y salida de uso general (GPIO) se utiliza para proporcionar las comunicaciones I²C junto con varias de las interfaces conectadas al Sapphire SoC, incluyendo NOR FLASH, USB UART, y tarjeta SD. El HSIO se utiliza para proporcionar la salida de vídeo de alta velocidad al transmisor HDMI ADC7511.

Uno de los elementos cruciales a la hora de diseñar con FPGA no es solo implementar y ajustar el diseño dentro de la FPGA, sino también ser capaz de colocar el diseño lógico dentro de la FPGA y lograr el rendimiento de temporización requerido cuando se enruta.

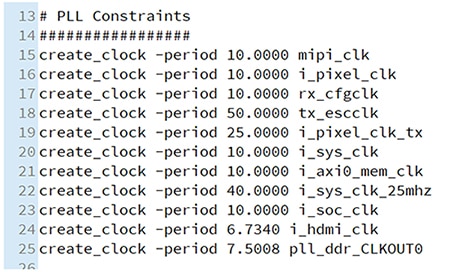

Atrás quedaron los diseños FPGA de dominio de reloj único. En el diseño de referencia Ti180 hay varios relojes diferentes, todos funcionando a altas frecuencias. La tabla de temporización final muestra las frecuencias máximas alcanzadas por los relojes del sistema. En las restricciones (Figura 5) también se aprecia el rendimiento de temporización solicitado, con una frecuencia de reloj máxima de 148,5 megahercios (MHz) para el reloj de salida HDMI.

Figura 5: Restricciones de reloj para el diseño de referencia. (Fuente de la imagen: Adam Taylor)

Figura 5: Restricciones de reloj para el diseño de referencia. (Fuente de la imagen: Adam Taylor)

La implementación de la temporización en función de las restricciones muestra el potencial de la estructura XLR de la FPGA Titanio, ya que reduce el posible retardo de enrutamiento, aumentando así el rendimiento del diseño (Figura 6).

|

Figura 6: La implementación de la temporización en función de las restricciones muestra el potencial de la estructura XLR de la FPGA Titanio para reducir el posible retardo del encaminamiento, aumentando así el rendimiento del diseño. (Fuente de la imagen: Adam Taylor)

Conclusión:

El diseño de referencia Ti180 M484 muestra claramente las capacidades de la FPGA Efinix y de la Ti180 en particular. El diseño aprovecha varias de las estructuras de E/S exclusivas para implementar una compleja ruta de procesamiento de imágenes que admite varios flujos MIPI entrantes. Este sistema de procesamiento de imágenes funciona bajo el control de un SoC Sapphire de núcleo blando, que implementa los elementos de procesamiento secuencial necesarios de la aplicación.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.