Por qué y cómo expandir la memoria del programa del microcontrolador con SPI XiP Flash

Colaboración de Editores de DigiKey de América del Norte

2019-05-08

A medida que las aplicaciones de microcontroladores se vuelven más complejas, los desarrolladores están utilizando más memoria de programa Flash para el firmware de la aplicación. Esto es especialmente cierto con los puntos finales del Internet de las cosas (IoT) que están comenzando a realizar una computación perimetral relativamente compleja. Sin embargo, a veces las aplicaciones pueden expandirse hasta el punto en que se requiera memoria de programa externa, en el momento en que los desarrolladores deben elegir entre Flash paralelo o en serie.

La adición de un chip de memoria Flash paralelo y externo une las líneas de E/S, agrega complejidad y consume espacio adicional en la placa. Este artículo describirá cómo expandir la memoria del programa Flash de un microcontrolador agregando un chip de memoria Flash en serie externo de Adesto Technologiesque admite una interfaz SPI eXecute in Place (XiP). También explicará cómo se asigna XiP Flash al espacio de memoria de un microcontrolador con Microchip Technology de modo que la ejecución del código es casi transparente para el firmware.

Razones para la expansión de la memoria externa

Cuando sea posible, los desarrolladores deben iniciar el desarrollo de aplicaciones seleccionando un microcontrolador que tenga una hoja de ruta de dispositivos compatibles con pin con más memoria. Si durante el desarrollo, el firmware de la aplicación se expande para exceder la memoria Flash en el dispositivo de destino, un dispositivo compatible con pin con más Flash puede sustituirse fácilmente durante el desarrollo. Esto permite que la memoria de la aplicación se expanda sin tener que rediseñar la placa de CI para un microcontrolador diferente.

Sin embargo, la aplicación puede requerir más memoria de programa que la que está disponible en el chip para una familia de microcontroladores compatibles con pin, lo que requiere el uso de memoria Flash fuera del chip. Esto se está volviendo más común y puede suceder por varias razones, lo que incluye:

- El alcance del sistema puede expandirse más allá de su concepto inicial durante la fase de desarrollo. Esto puede deberse a cambios de última hora en la aplicación, a la proliferación de funciones o a una predicción no precisa de las necesidades de memoria de la aplicación. Las opciones son actualizar con un microcontrolador compatible con pin que tenga más memoria de programa Flash o agregar memoria de programa Flash externa adicional, lo que puede retrasar el proyecto si el desarrollo ya está avanzado.

- Las futuras actualizaciones de firmware en el campo pueden requerir más memoria de programa Flash de la que está disponible en el microcontrolador que ya se encuentra en la placa del sistema. En esta situación, las opciones son limitadas: reemplazar los sistemas en el campo por otros que contengan más memoria de programa Flash o cancelar la actualización.

- El desarrollo de la familia de productos del sistema puede requerir un nuevo producto que necesite más memoria de programa Flash de la que ya está disponible para la familia de microcontroladores compatibles con pin. Las opciones son rediseñar el sistema utilizando una nueva familia de microcontroladores o agregar una memoria de programa Flash externa.

Claramente, es importante para un desarrollador anticipar las necesidades de los sistemas presentes y futuros para esta expansión de memoria, y planificar para ello. Si existe la posibilidad de que el proyecto necesite una memoria de programa Flash externa, el desarrollador debe establecer un lugar para la futura expansión de la placa de CI. Si bien no es necesario que el chip de memoria Flash se coloque en la placa, es mejor estar seguro y tener el espacio ya establecido.

La forma tradicional de ampliar la memoria del programa Flash ha sido utilizar una interfaz Flash paralela con líneas de direcciones y datos. Sin embargo, incluso el uso más eficiente de la memoria Flash paralela que no sacrifica la velocidad puede utilizar 16 bits de dirección, 16 bits de datos y cuatro o más señales de control. Esto requiere 36 o más pines del microcontrolador.

Además de ser un uso ineficiente de los recursos de un microcontrolador, esto limita la selección del microcontrolador a los dispositivos con un bus externo, lo que aumenta la cantidad de pines del microcontrolador. Un bus paralelo externo también consume mucho espacio en la placa de CI, mientras que la dirección de alta velocidad y el bus de datos aumentan la posibilidad de interferencias electromagnéticas (EMI).

Ejecución del código de SPI XiP

Una opción más efectiva es usar un dispositivo de memoria de programa Flash externa que admita una interfaz SPI XiP. Una interfaz SPI XiP puede usar solo seis pines para conectarse al microcontrolador host. A diferencia de una interfaz SPI convencional, a la memoria en el dispositivo de memoria Flash externa no se accede directamente con un controlador de firmware SPI, sino que se asigna en la memoria del programa del microcontrolador.

Un buen ejemplo de un dispositivo de memoria Flash en serie diseñado para interactuar utilizando una interfaz SPI XiP es el AT25SL321-UUE-T de Adesto Technologies (Figura 1). Esta es una memoria Flash de 32 megabits (Mbits) que admite modos de SPI simples, dobles y cuádruples. Admite un reloj de SPI de 104 megahertz (MHz), que en modo de SPI doble proporciona una velocidad de reloj equivalente de 266 MHz, y en modo de SPI cuádruple, una velocidad de reloj equivalente de 532 MHz.

Figura 1: El AT25SL321 de Adesto es una memoria Flash de 32 Mbits que admite los modos de SPI simples, dobles y cuádruples. Proporciona 32 Mbits de memoria Flash en un paquete SOIC, DFN8 o TSSOP8 de 8 pines. (Fuente de la imagen: Adesto Technologies)

Junto con los 32 Mbits de Flash, el dispositivo tiene registros de estado para configurar el dispositivo. La lectura de los registros de estado puede indicar al firmware si el dispositivo tiene una operación de escritura o borrado en curso. La escritura en los registros de estado permite que los bloques de la memoria Flash estén protegidos contra escritura.

El AT25SL321 de Adesto también tiene 4 kilobits (Kbits) de memoria programable una sola vez (OTP) que se puede usar para almacenar información de seguridad, como un número de serie único. Se presenta en un paquete SOIC, DFN8 o TSSOP8 de 8 pines.

Al igual que todos los dispositivos de memoria en serie que admiten SPI XiP, el AT25SL321 de Adesto se configura mediante un conjunto de instrucciones específico para los dispositivos de Adesto. El conjunto de instrucciones consta de 38 comandos que utiliza el microcontrolador host para controlar el Flash en serie. Un periférico de SPI XiP en un microcontrolador host incluirá una máquina de estado programable que se inicia en el encendido del microcontrolador con el conjunto de instrucciones del Flash en serie objetivo. Una vez iniciado, el funcionamiento del periférico de SPI es transparente para el firmware que ejecuta el código en la región de SPI XiP asignada de la memoria.

Por ejemplo, si el firmware del microcontrolador host lee datos de la región asignada a la memoria, el SPI XiP que se configura con el conjunto de instrucciones de Adesto envía un código de instrucciones de lectura de datos seguido de una dirección de byte de 24 bits a la memoria en serie de Adesto. La memoria en serie de Adesto luego envía el contenido de la memoria al microcontrolador host un byte a la vez. Para el firmware, esto aparece como una lectura normal de la memoria.

Además de un reloj de SPI, datos y pines de selección de chip, el AT25SL321 de Adesto tiene dos pines adicionales para una funcionalidad mejorada en el sistema. WP\ es un pin de protección contra escritura activo-bajo que evita la escritura en el registro de estado para proteger los bloques de código contra escritura. El microcontrolador puede usar este pin para evitar que las tareas de baja prioridad realicen cambios no autorizados. HOLD\ se utiliza para pausar una transferencia de datos en curso. Esto puede ser útil si el microcontrolador recibe una señal de interrupción de alta prioridad mientras se está realizando una transferencia de datos a la memoria y debe pausarse hasta que se repare la interrupción.

El dispositivo Flash de Adesto AT25SL321 de 32 Mbits admite cuatro modos de operación:

- Operación de SPI estándar: Se accede a la memoria Flash como un dispositivo de memoria SPI estándar con reloj de SPI (SCLK), selección de chip activo-bajo (CS\), datos de entrada en serie (SI) y datos de salida en serie (SO). Los modos de bus SPI estándar 0 y 3 son compatibles.

- Operación de SPI doble: Esto proporciona el doble de la velocidad de datos de la operación de SPI estándar al utilizar SI y SO como pines de datos bidireccionales, designados como IO0 e IO1.

- Operación de SPI cuádruple: Proporciona cuatro veces la velocidad de datos de la operación de SPI estándar. Además de IO0 e IO1, WP\ y HOLD\ se utilizan como pines de datos bidireccionales, IO2 e IO3. En la operación de SPI cuádruple, las funciones WP\ y HOLD\ no están disponibles.

- Operación de QPI: Solo se utiliza para la operación de SPI XiP. Mientras que los modos de SPI estándar, doble y cuádruple admiten el envío de comandos a la memoria SPI utilizando solo el pin IO0, la operación de QPI admite el envío de comandos usando los cuatro pines IO [0:3], lo que mejora significativamente el rendimiento de SPI XiP.

Si los 32 Mbits del AT25SL321 de Adesto no son suficientes, Adesto también ofrece el AT25QL641-UUE-Tde 64 Mbit. Los dos dispositivos son compatibles con pin, por lo que el AT25QL641 puede ser un reemplazo directo. Además de tener más memoria, la única diferencia entre los dos dispositivos es que el AT25QL641 está configurado en la operación de QPI por defecto en el encendido. Esto reduce el tiempo de configuración del dispositivo en sistemas de alto rendimiento. Ambos dispositivos consumen solo 5 miliamperios (mA) durante un ciclo de lectura de memoria. Ambos dispositivos de memoria de Adesto operan en un solo riel de 1.7 a 2.0 voltios y pueden conectarse a cualquier microcontrolador compatible con voltaje que tenga una interfaz SPI XiP.

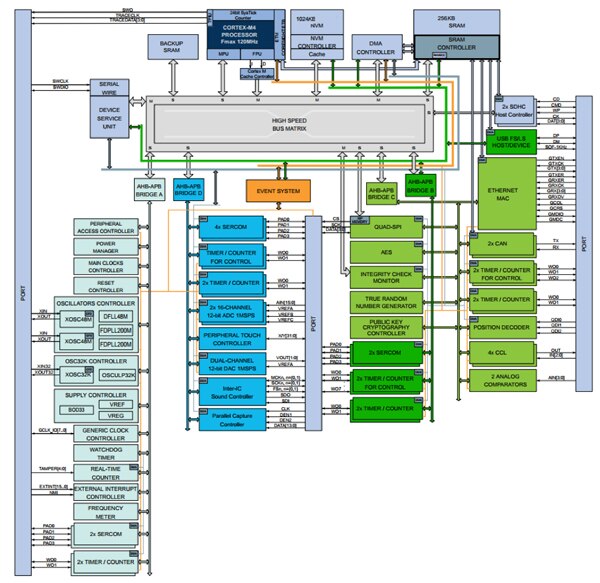

Para el microcontrolador host, Microchip Technology tiene interfaces SPI XiP en su serie de ATSAMD51 que incluye el microcontrolador de 120 MHz ATSAMD51J20A-UUT basado en Arm® Cortex®-M4F. Este dispositivo tiene 1 Mbyte de Flash y 256 kilobytes (Kbytes) de RAM. Tiene una gama completa de periféricos que incluyen un convertidor de analógico a digital (ADC), convertidor de digital a analógico (DAC), puerto USB e I2S. También tiene un periférico de cifrado de clave pública y un verdadero generador de números aleatorios (TRNG) para funciones de seguridad.

Figura 2: El ATSAMD51J20A de Microchip tiene un conjunto completo de periféricos, que incluyen una interfaz en serie SPI XiP, ADC, DAC y soporte para el cifrado de datos. (Fuente de la imagen: Microchip Technology)

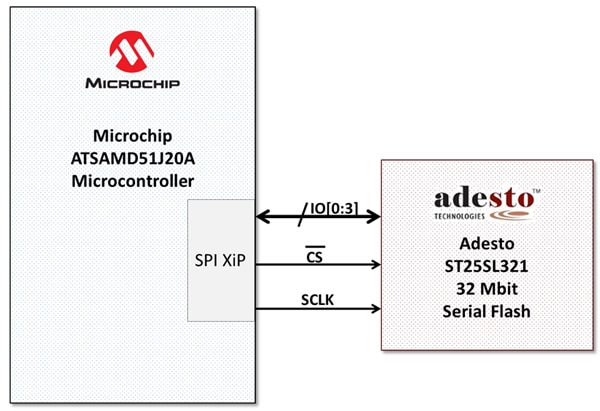

Para conectarse a una memoria Flash externa, los desarrolladores pueden usar el periférico de QSPI de ATSAMD51J20A que admite SPI XiP. Esto permite que el código se ejecute directamente desde la memoria Flash de Adesto. El ATSAMD51J20A asigna el Flash de Adesto al espacio de la memoria del programa del Bus de alto rendimiento avanzado (AHB) de Arm. Para proteger los datos en el Flash en serie, el SIP XiP de ATSAMD51J20A admite la codificación transparente de los datos escritos en la memoria externa SPI y la decodificación de los datos leídos desde la memoria externa SPI. Esto puede ayudar a evitar la copia no autorizada de firmware y la piratería del sistema.

Figura 3: El microcontrolador ATSAMD51J20A de 32 bits de Microchip tiene un periférico de QSPI que admite un puerto en serie de SPI XiP. Este puede interactuar fácilmente con el flash en serie de Adesto AT25SL321 usando solo seis pines. (Fuente de la imagen: DigiKey)

Uso del ATSAMD51J20A de Microchip con un dispositivo de memoria Flash en serie de Adesto

El periférico de SPI XiP ATSAMD51J20A de Microchip tiene tres registros que se utilizan para enviar comandos a un Flash XiP en serie externo. Dado que los dispositivos de memoria Flash XiP en serie de diferentes proveedores utilizan diferentes códigos de instrucción, estos registros deben ser configurados de la siguiente manera por el desarrollador para el proveedor de memoria específico utilizado:

- El Registro de códigos de instrucción contiene las instrucciones utilizadas para acceder al Flash en serie. Para un dispositivo de memoria Flash de Adesto que funciona en modo de SPI cuádruple, este registro contiene una instrucción de salida cuádruple de lectura rápida 0x6B si el firmware está ejecutando un código fuera de la región XiP asignada a la memoria. Este registro debe cambiarse al código de instrucción apropiado si se está realizando una operación de escritura, borrado o registro de estado.

- El Registro de direcciones de instrucción contiene la dirección de memoria Flash a la que se accede en la memoria Flash externa en serie. Cuando el SPI XiP de ATSAMD51J20A de Microchip está configurado para el modo de memoria en serie, el periférico de SPI XiP configura automáticamente esta dirección a la dirección que ejecuta el firmware en el rango de espacio de memoria del AHB asignado a la memoria 0x0400 0000 a 0x0500 0000.

- El Registro de cuadros de instrucción configura el SPI XiP para el formato del cuadro de instrucción específico para el dispositivo de memoria externa que se está utilizando. Esto incluye seleccionar la longitud de la dirección de 24 o 32 bits, habilitar la tasa de datos doble (DDR), si se admite el modo de lectura continua y la longitud del código de operación.

El resto de la interfaz SPI XiP de Microchip se configura fácilmente utilizando los controladores de SPI de Microchip.

Mientras el firmware de la aplicación en el microcontrolador esté ejecutando un código fuera de la región asignada a la memoria de SPI XiP, no es necesario reconfigurar el periférico de SPI XiP en el microcontrolador. La memoria Flash de Adesto también admite un modo de lectura con solo un pin SI con código de instrucción 0x03. Si solo se está utilizando el modo de SPI doble, el código de instrucción es 0x3B. Estos códigos están escritos por el firmware de la aplicación en el registro de códigos de instrucción.

Se considera una buena práctica vaciar cualquier caché asociada con el espacio de direcciones asignado a la memoria cuando se cambia el registro del código de instrucción. Al leer o escribir en los registros de estado de la memoria Flash en serie, la memoria caché debe vaciarse y luego deshabilitarse. Esto también se debe hacer al escribir en el Flash en las regiones asignadas a la memoria. La memoria caché debe volver a habilitarse una vez que se reanuden las operaciones de lectura de memoria.

Debido a las transferencias de datos de alta velocidad involucradas, el Flash en serie debe colocarse en la placa de CI lo más cerca posible del puerto de SPI XiP del microcontrolador. Si eso no es posible, ningún rastro debe ser mayor que 120 milímetros (mm). La señal del reloj debe tener al menos tres veces el ancho de los trazados de la placa de CI lejos de otras señales para evitar interferencias. Las señales de datos bidireccionales IO [0:3] deben estar todas a una distancia de 10 mm entre sí para evitar sesgos.

Conclusión

Los dispositivos de memoria Flash en serie externa pueden proporcionar una ejecución rápida de código de firmware sin la complejidad y el exceso del espacio de la placa de los chips Flash paralelos. Esto permite una fácil expansión del código del programa a lo largo del tiempo, así como actualizaciones de campo sin tener que volver a diseñar la placa del sistema.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.