Use HyperBus para expandir la memoria en diseños pequeños de IoT (internet de las cosas) y diseños ponibles para ahorrar espacio y costo.

Colaboración de Editores de DigiKey de América del Norte

2018-08-01

Con la reducción de los nodos IoT y los dispositivos ponibles, los diseñadores deben aprovechar al máximo la memoria integrada de sus microcontroladores para minimizar el espacio, la potencia y el costo de la placa. Sin embargo, a veces no se puede evitar la expansión de la memoria. En lugar de utilizar de forma predeterminada la estructura de bus de un controlador de 32 bits, los diseñadores deberían considerar HyperBus, una interfaz de alta velocidad de 333 Mbit/s, de 8 bits y de doble velocidad de datos (DDR) para direcciones y datos.

Aunque los diseñadores intentan evitar la expansión, a menudo es necesario debido a los mayores requisitos de memoria durante el desarrollo. O bien, los desarrolladores simplemente preparan el diseño para el futuro al anticipar futuras necesidades de expansión.

Con HyperBus, los microcontroladores pueden admitir flash externo y RAM en el mismo bus, en comparación con el bus de datos de 16 bits y de direcciones de 16 bits y los pines de control asociados de una interfaz típica de 32 bits. Funciona con cualquier dispositivo de memoria que tenga un puerto de interfaz HyperBus, y es una interfaz efectiva y fácil de usar para la expansión de memoria de bajo número de pines en aplicaciones con espacio limitado.

Si bien el funcionamiento del bus es transparente para el firmware, es importante que los desarrolladores nuevos en HyperBus se familiaricen con el funcionamiento de las señales del bus de alta velocidad para garantizar un diseño robusto. Este artículo primero describirá el funcionamiento de HyperBus. Luego introducirá microcontroladores que incorporan la interfaz y les mostrará a los usuarios cómo aplicarlo de manera efectiva y cómo probar su diseño.

Explicación de HyperBus

Como se mencionó, HyperBus utiliza una interfaz DDR de 8 bits de alta velocidad para direcciones y datos. Además, utiliza un reloj diferencial, una señal de cierre de lectura/escritura y una selección de chip para cada dispositivo de memoria. HyperBus admite flash externo y RAM en el mismo bus, y funciona con cualquier microcontrolador con una interfaz periférica compatible con HyperBus.

HyperBus se configura como una interfaz maestra/esclava, donde un hostmaster interactúa con uno o más dispositivos de memoria esclavos en el bus. Los dispositivos de memoria flash de HyperBus se conocen como HyperFlash™, y los dispositivos de memoria DRAM de HyperBus se conocen como HyperRAM™.

El bus utiliza un reloj diferencial con señales designadas CK y CK#. Como HyperBus es una interfaz DDR, los datos se transfieren tanto en el flanco ascendente como descendente del reloj. El reloj es manejado solo por el maestro, y su frecuencia no puede exceder la frecuencia de reloj nominal de la memoria HyperBus más lenta en el bus.

El bus bidireccional de 8 bits se designa DQ[0-7] y transfiere direcciones, datos y comandos entre los dispositivos maestros y esclavos. Se utiliza una señal estroboscópica bidireccional de datos de lectura/escritura, designada como RWDS, para bloquear los datos. La RWDS es controlada por cualquier dispositivo que esté leyendo datos, por lo que si el host del microcontrolador está escribiendo datos en HyperRAM, el HyperRAM controla la señal RWDS. Los datos que se leen en DQ[0-7] están alineados con ambos flancos del reloj.

Cada dispositivo esclavo se selecciona mediante una selección de chip baja activa, designada como CS0#, CS1#, CS2#, etc. Solo una selección de chip puede estar activa en cualquier momento. Todas las transacciones de bus se inician con la selección de chip designada de transición de alto a bajo. Todas las transacciones de bus se terminan con la selección de chip designada de transición de bajo a alto. Los desarrolladores deben asegurarse de que una selección de chip esté activa en cualquier momento. De lo contrario, es posible que más de un dispositivo esclavo HyperBus controle la RWDS al mismo tiempo, lo que puede provocar la corrupción de los datos.

Una señal de reinicio de hardware baja activa, designada como RESET#, es controlada por el maestro. Cuando se baja, restablece el estado de cualquier dispositivo de memoria de HyperBus externo conectado a la señal. Esto incluye restablecer los registros de configuración internos del dispositivo de memoria. Sin embargo, no afecta el estado de la memoria interna de los dispositivos de memoria de HyperBus. En la mayoría de las interfaces de microcontroladores maestros de HyperBus, RESET# no es parte del periférico de HyperBus, sino que es un pin de E/S general. Los dispositivos esclavos de HyperBus tienen una subida débil en el pin RESET#, por lo que si se deja flotando, se lleva a un estado alto.

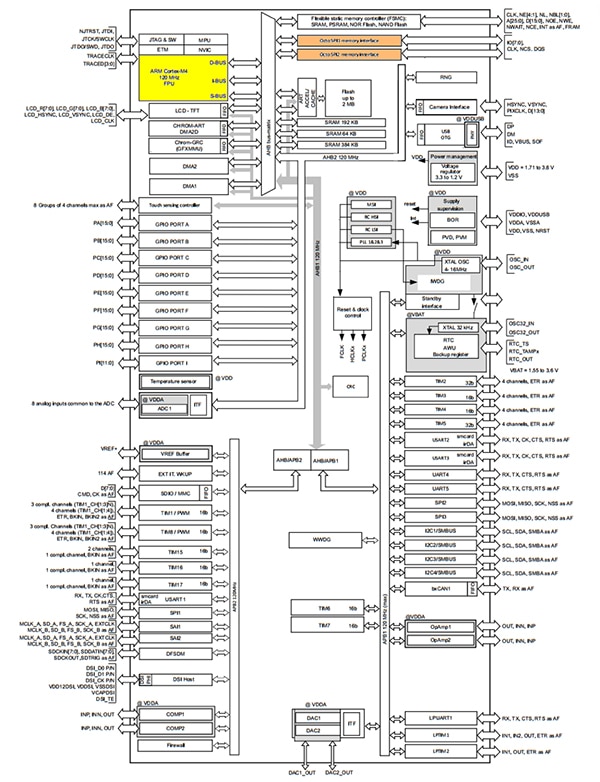

Cualquier periférico compatible con HyperBus en un microcontrolador debe cumplir con la especificación de HyperBus. Un buen ejemplo de un microcontrolador compatible con HyperBus es STM32L4R9 Arm® Cortex®-M4F de STMicroelectronics (Figura 1). El STM32L4R9 tiene 2 MB de memoria flash interna y 640 Kbytes de SRAM. Tiene una amplia variedad de periféricos, lo que incluye dos interfaces OctoSPI que pueden configurarse como interfaces de HyperBus.

Figura 1: El microcontrolador STM32F4L9 de STMicroelectronicsse basa en un núcleo Arm® Cortex®-M4 con FPU y tiene dos interfaces compatibles con HyperBus, que se ven aquí resaltadas en naranja. (Fuente de la imagen: STMicroelectronics)

El STM32L4R9 accede a las direcciones de memoria externa de HyperBus como memoria asignada al espacio de dirección del bus AHB del microcontrolador, por lo que el núcleo accede a las lecturas y escrituras en la memoria externa de la misma manera que la memoria interna. Una vez que los dispositivos de memoria externa estén configurados, el funcionamiento del HyperBus es transparente para el núcleo.

Las memorias de HyperBus son todas de 16 bits de ancho, por lo que todos los accesos desde el STM32L4R9 deben estar en los límites de la memoria de 16 bits. Los accesos de datos desde el maestro STM32L4R9 pueden ser de 16 bits o de 32 bits, y también deben estar en los límites alineados.

Una transacción de lectura o escritura típica en el HyperBus consiste en una serie secuencial de transferencias de datos de 16 bits de un ciclo de reloj a través de dos transferencias de datos correspondientes de 8 bits de ancho de medio ciclo de reloj, una en cada flanco del reloj de un solo extremo o cruce de reloj diferencial. Las transacciones de lectura y escritura siempre transfieren palabras completas de datos de 16 bits. Las palabras de lectura de datos siempre contienen dos bytes válidos. Las palabras de escritura de datos pueden tener uno o ambos bytes enmascarados para evitar la escritura de bytes individuales dentro de una ráfaga de escritura. Las transferencias de bytes no son compatibles con el protocolo HyperBus, tampoco admiten un funcionamiento de bits como la banda de bits.

Cada puerto compatible con HyperBus en el STM32L4R9 tiene un espacio de direcciones asignado en memoria, dedicado de 256 Mbytes, asignado de la siguiente manera:

HyperBus1 (OctoSPI1) 0x90000000 a 0x9FFFFFFF

HyperBus2 (OctoSPI2) 0x70000000 a 0x7FFFFFFF

La dirección interna del dispositivo de memoria HyperFlash o HyperRAM al que se accede está desplazada de la dirección de memoria base de la ubicación anterior. Por ejemplo, si el STM32F4L9 lee desde la ubicación de memoria 0x90000047, lee el valor almacenado en el dispositivo de memoria al que se accede en HyperBus1 en la ubicación de memoria 0x0047.

Cypress Semiconductor desarrolló la especificación de HyperBus, y también tiene una línea de productos de memorias de HyperBus. La memoria HyperFlash S26KS512SDPBHI020 de 64 MB x 8 de Cypress puede interactuar fácilmente con uno de los puertos OctoSPI. Admite accesos de ráfaga envuelta de hasta 32 palabras de 16 bits. Con una velocidad de reloj máxima de 166.6 MHz, el HyperFlash S26KS512 admite la velocidad de lectura sostenida de 333 Mbytes/s. En el reloj máximo OctoSPI de 60 MHz, el STM32L4R9 puede leer cualquier memoria de HyperBus externa a 120 Mbytes/s, máximo.

El STM32L4R9 puede ejecutar un código directamente desde esta memoria flash si se accede al HyperFlash a través del bus del sistema Cortex-M4. Cuando se utiliza para la memoria de códigos, OctoSPI admite eXecute In Place (XIP) con un búfer de captación previa integrado que carga la siguiente dirección de memoria desde la memoria externa.

La memoria HyperRAM S27KS0641DPBHI020 de 8 MB x 8 de Cypress Semiconductor es una DRAM que se puede actualizar automáticamente y que puede expandir la memoria de datos STM32L4R9. Admite accesos de ráfaga envuelta de hasta 64 palabras de 16 bits. El HyperRAM S27KS0641 también admite una velocidad de lectura sostenida de hasta 333 Mbytes/s y el STM32L4R9 puede leerlo a un máximo de 120 Mbytes/s.

Interfaz con memorias de HyperBus

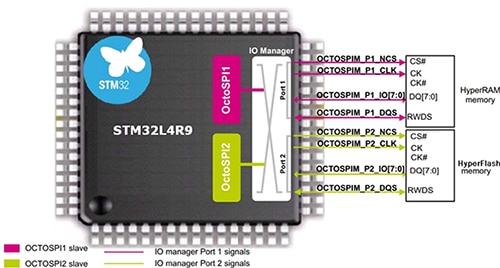

El STM32L4R9 tiene dos puertos compatibles con HyperBus, y cada uno puede conectarse por separado a los dispositivos de memoria externa de HyperRAM e HyperFlash (Figura 2). La señal RESET# es opcional y, por lo tanto, no se muestra en la figura. Tanto con el HyperFlash como con el HyperRAM de Cypress, el STM32L4R9 puede ampliar fácilmente su memoria interna con un impacto mínimo en el tamaño de la placa de CI y la complejidad del diseño.

Figura 2: El STM32L4R9 tiene dos puertos compatibles con HyperBus, y cada uno puede conectarse por separado a los dispositivos de memoria externa de HyperRAM e HyperFlash. (Fuente de la imagen: STMicroelectronics)

Las señales más importantes para el diseño son DQ[0-7] y RWDS. Para obtener el mejor rendimiento, estas señales deben tener la menor longitud posible en la placa de CI entre el microcontrolador y la memoria.

Las señales de reloj diferencial CK y CK# deben estar una al lado de la otra con un espacio constante entre ellas para la longitud de las señales. Si es posible, proteja CK y CK# con rastros de cubierta de seguridad VSS para minimizar la EMI. Para minimizar el desajuste de impedancia, rompa todas las señales en la capa superior de la placa de CI con una capa VSS sólida debajo.

Para el desarrollador nuevo de HyperBus, es una buena idea agregar puntos de prueba de la sonda. Para DQ[0-7] y RWDS, los puntos de prueba deben estar tanto en el microcontrolador STM32L4R9 como en el dispositivo de memoria. Cuando el STM32L4R9 escribe, es bueno mirar los puntos de prueba más cercanos al dispositivo de memoria. Cuando el STM32L4R9 lee, mire los puntos de prueba más cercanos al STM32L4R9. Para CK, CK# y CS, coloque los puntos de prueba más cerca del dispositivo de memoria.

Debido a las altas frecuencias de reloj involucradas en la interfaz DDR, es importante que el suministro de voltaje al STM32L4R9 y los dispositivos de memoria estén lo más limpios posible. Un suministro ruidoso afectará la temporización de la señal y puede causar errores de transferencia de bus, por lo que se recomienda el uso de condensadores de desacople. Los dispositivos de memoria de HyperBus tienen una alimentación y conexión a tierra separadas para los pines de E/S, y se deben agregar capacitores de 1 microfaradio (µF) y 0.1 µF en la capa superior o inferior a la potencia de E/S VCCQ.

Acceso de firmware a HyperBus

Los dispositivos de memoria de HyperBus tienen registros en chip que se utilizan para establecer opciones y tiempos para el dispositivo. HyperBus se refiere a estos como Registros de configuración (CR). Todos los dispositivos de HyperRAM tienen CR internos que permiten establecer ciertas características operativas. Para el HyperRAM S27KS0641, el firmware puede configurar sus modos de baja potencia, longitud de ráfaga envuelta, tipo de ráfaga envuelta, parámetros de tiempo R/W y potencia de la unidad de salida en el bus de datos externo de 8 bits.

HyperFlash no tiene CR, pero tiene registros de estado. El HyperFlash S26KS512 tiene tres registros de estado. Admite el código interno de corrección de errores (ECC) para validar el funcionamiento de escritura y tiene un registro de estado ECC para indicar errores de escritura. Otro registro contiene la dirección de cualquier error ECC. Un tercer registro cuenta las correcciones ECC y los errores incorregibles. Todos estos registros son de solo lectura.

Las transacciones de HyperBus admiten dos tipos de funcionamiento de memoria. El primero es leer o escribir en memoria externa. El segundo es leer o escribir en CR o leer registros de estado.

Una vez que el OctoSPI STM32L4L9 se configura como un puerto de HyperBus, el núcleo puede acceder a la memoria como cualquier otra ubicación asignada en la memoria. Cada funcionamiento de lectura o escritura en el espacio de HyperBus asignado en la memoria inicia una transacción entre el microcontrolador y la memoria externa. Cada transacción de HyperBus comienza cuando el microcontrolador envía tres palabras de 16 bits con instrucciones de Comando/Dirección al dispositivo de memoria externa. La secuencia de Comando/Dirección le dice al dispositivo de memoria externa si el funcionamiento es de lectura o escritura, si se están abordando los registros de configuración o espacio de memoria, si la transacción es una transacción de ráfaga envuelta o lineal, y proporciona la fila y la columna de la dirección de destino. Si bien todo esto es transparente para el microcontrolador con firmware operativo, la secuencia de Comando/Dirección es importante durante la depuración.

Introducción a HyperBus

Una vez que el desarrollador entienda el protocolo de HyperBus, se recomienda que se realice alguna programación experimental con una placa de evaluación, especialmente si el desarrollador es nuevo en la interfaz. La placa de evaluación STM32L4R9I-EVAL de STMicroelectronics para el microcontrolador STM32L4R9 es un buen punto de partida (Figura 3). El dispositivo de memoria de HyperRAM está en un círculo rojo, con los puntos de prueba del dispositivo ubicados en el conector cabecera a la derecha.

Figura 3: El STM32L4R9I-EVAL de STMicroelectronics se utiliza para evaluar el microcontrolador STM32L4R9. El dispositivo de memoria de HyperRAM está en un círculo rojo, con los puntos de prueba del dispositivo ubicados en el conector cabecera a la derecha. (Fuente de la imagen: STMicroelectronics)

El STM32L4R9I-EVAL tiene una amplia gama de características, que incluyen una interfaz de cámara, dos micrófonos MEMS, una palanca de mando y una pantalla TFT LCD a color de 4.3 pulgadas de 480 x 272 píxeles. La placa de evaluación admite la interfaz OctoSPI y tiene un dispositivo HyperRAM IS66WVH8M8BLL de 64 Mbit de ISSI soldado a la placa de CI.

Conclusión

El protocolo de HyperBus es una interfaz adecuada y fácil de usar para la expansión de memoria de bajo número de pines en aplicaciones de espacio crítico. Si bien el funcionamiento del bus es transparente para el firmware, es importante que el desarrollador nuevo de HyperBus se familiarice con el funcionamiento de las señales del bus de alta velocidad para asegurar un diseño robusto.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.