Usar un eficiente procesador multinúcleo para construir productos más inteligentes con capacidad de voz

Colaboración de Editores de DigiKey de América del Norte

2020-02-14

La demanda de productos más inteligentes se ha generalizado en casi todas las áreas de aplicación a medida que los usuarios se familiarizan y confían en asistentes digitales virtuales, como Amazon Alexa, Google Assistant, Apple Siri y Microsoft Cortana, entre otros. Además de ofrecer comodidad, estos asistentes desempeñan un papel cada vez más importante en la mejora de la seguridad en una amplia gama de productos para sistemas industriales y aplicaciones sanitarias. Sin embargo, para los desarrolladores, los diseños subyacentes de estos productos a veces plantean exigencias contradictorias en cuanto a los procesadores capaces de ofrecer un mejor rendimiento, un costo y una huella optimizados, y un funcionamiento eficiente.

Este artículo muestra cómo los desarrolladores pueden utilizar un procesador multinúcleo, en este caso el Nano i.MX 8M de NXP, para satisfacer los diversos requisitos de procesamiento e interfaz de los productos inteligentes emergentes en segmentos de aplicación que van desde la automatización inteligente del hogar y la industria hasta los sistemas médicos. En particular, este artículo muestra cómo los desarrolladores pueden utilizar este procesador para implementar más fácilmente soluciones de próxima generación basadas en la voz con capacidades avanzadas de procesamiento de audio.

La evolución de los productos inteligentes

El rápido auge de las tecnologías de asistente de voz ha hecho que los usuarios busquen más funcionalidad de los productos inteligentes. Los productos emergentes no sólo necesitan responder a comandos de voz, sino que también necesitan incorporar más inteligencia, utilizando una mayor variedad de datos de entrada de sensores, cámaras y otros productos. No basta con que los interruptores de luz inteligentes enciendan y apaguen las luces o que los lavavajillas funcionen en respuesta a comandos de voz. A medida que las aplicaciones crecen en sofisticación, sus dispositivos subyacentes tendrán que soportar combinaciones más diversas de sensores, capacidades de procesamiento mejoradas utilizando métodos de inteligencia artificial (IA) y pantallas gráficas en 3D.

La necesidad de productos más inteligentes va más allá del deseo de una mayor comodidad. En ámbitos de aplicación críticos como la automatización industrial y la atención sanitaria, la capacidad de un dispositivo para alertar proactivamente a sus usuarios sobre peligros o condiciones patológicas puede resultar esencial. Un trabajador de una fábrica que lleva un casco que puede vigilar los alrededores circundantes puede evitar con mayor facilidad los peligros; un paciente de riesgo que lleva un pequeño monitor de atención sanitaria que vigila continuamente los signos vitales puede recibir la intervención necesaria mucho antes de una crisis.

Estos y otros productos inteligentes imponen requisitos de diseño específicos tan variados como sus aplicaciones de destino, pero la mayoría comparte la necesidad de un procesamiento de alto rendimiento, capacidades multimedia y un funcionamiento seguro. Para los desarrolladores, estos requisitos funcionales se combinan con la necesidad fundamental de soluciones capaces de escalar para servir a aplicaciones más resistentes, mientras que la escala física se reduce para ajustarse a las expectativas del usuario en cuanto a tamaño, costo y consumo de energía reducidos. Al basarse en una arquitectura heterogénea de múltiples núcleos, la familia de procesadores de aplicaciones Nano NXP i.MX 8M cumple con los amplios y diversos requisitos de los diseños de los productos inteligentes emergentes.

Núcleos de alto rendimiento

El Nano NXP i.MX 8M es el miembro más reciente de la familia de procesadores NXP i.MX 8M diseñados para proporcionar una plataforma de procesamiento multinúcleo escalable. Para aplicaciones de video de alta gama, los procesadores insignia de NXP i.MX 8M, como el MIMX8MQ5DVAJZAB, proporcionan una resolución de pantalla de hasta 4K con decodificación por hardware de video de alto rango dinámico (HDR) de 4K. Para video 1080p, los procesadores NXP i.MX 8M Mini, como el MIMX8MM6CVTKZAA, proveen soporte de decodificación de hardware 1080p. Tanto la serie i.MX 8M como la 8M Mini combinan hasta cuatro núcleos de procesador de aplicaciones Arm® Cortex®-A53 con un núcleo de microcontrolador Arm Cortex-M4F.

Por el contrario, el procesador Nano NXP i.MX 8M MIMX8MN6CVTIZAA combina cuatro núcleos de Arm Cortex-A53 con un núcleo de Arm Cortex-M7, que proporciona el mayor rendimiento entre otros núcleos de la serie Arm Cortex-M, incluido el Cortex-M4F.

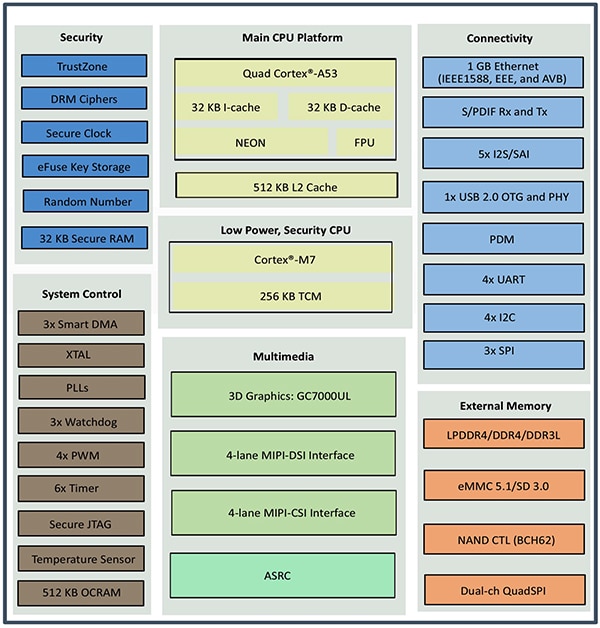

Además de su complemento de núcleos de procesador, los nano procesadores i.MX 8M son compatibles con una amplia variedad de dispositivos de memoria externa y proporcionan una gama completa de interfaces periféricas externas que son requeridas generalmente en aplicaciones de consumo e industriales (Figura 1).

Figura 1: El procesador Nano NXP i.MX 8M combina hasta cuatro procesadores de aplicación Arm Cortex-A53, un microcontrolador Arm Cortex-M7, subsistemas de hardware especializados e interfaces periféricas externas completas que se utilizan normalmente en aplicaciones de consumo e industriales. (Fuente de la imagen: NXP)

Figura 1: El procesador Nano NXP i.MX 8M combina hasta cuatro procesadores de aplicación Arm Cortex-A53, un microcontrolador Arm Cortex-M7, subsistemas de hardware especializados e interfaces periféricas externas completas que se utilizan normalmente en aplicaciones de consumo e industriales. (Fuente de la imagen: NXP)

Las diferentes variantes disponibles de la serie de procesadores Nano i.MX 8M permiten a los desarrolladores cumplir fácilmente sus requisitos específicos de costo y rendimiento. Por ejemplo, los miembros de alto rendimiento integran una amplia gama de subsistemas especializados en seguridad, pantallas gráficas en 3D, procesamiento de audio y más. Otros miembros de Nano procesadores de la serie i.MX 8M ofrecen opciones con menos núcleos de Cortex-A53, y versiones "Lite" con capacidades gráficas reducidas.

No obstante, todos los miembros de la serie de Nano procesadores i.MX 8M ofrecen la capacidad de ofrecer la combinación de rendimiento de aplicaciones y capacidad en tiempo real que se requiere en los productos inteligentes emergentes.

Diseñado para proporcionar un funcionamiento de alto rendimiento del software de aplicación, cada núcleo del procesador de aplicaciones Arm Cortex-A53 puede funcionar a frecuencias de reloj de hasta 1.5 gigahercios (GHz) mientras trabaja desde una caché de instrucciones dedicada de nivel 1 (L1) de 32 kilobytes (Kbytes) (caché I), una caché de datos de 32 Kbytes (caché D) y una caché unificada compartida de L2 512 Kbytes. Junto con su unidad de punto flotante (FPU) integrada, estos núcleos soportan la tecnología de Neón del brazo para operaciones avanzadas de datos múltiples de una sola instrucción (SIMD) utilizadas en el procesamiento de señales digitales y otros algoritmos avanzados en aplicaciones de datos intensivos.

Para los requisitos del sistema incorporado, el núcleo del microcontrolador Arm Cortex-M7 funciona a frecuencias de hasta 750 megahercios (MHz), al tiempo que proporciona una ejecución de alto rendimiento de los procesos en tiempo real que requieren una baja latencia y un funcionamiento determinista. Para acelerar aún más el procesamiento, el núcleo incluye una FPU integrada y 256 Kbytes de memoria estrechamente acoplada (TCM) utilizada para la instrucción y la caché de datos.

Sin embargo, para las complejas tareas de procesamiento en tiempo real, la capacidad de reconocer rápidamente fuentes de interrupción separadas puede ser tan crítica como la potencia de procesamiento en bruto. En los nano procesadores i.MX 8M, un controlador de interrupción global (GIC) incorporado en cada núcleo Arm Cortex-A53 y un controlador de interrupción vectorial anidado (NVIC) en el núcleo Arm Cortex-M7, permiten el manejo de interrupciones de grano fino de casi 128 fuentes distintas de solicitud de interrupción correspondientes a estados del núcleo, temporizadores, eventos de interfaz periférica, operaciones de acceso directo a la memoria (DMA), procesos de hardware especializados y muchos más.

Procesamiento multinúcleo heterogéneo

Por separado, cada núcleo del Nano procesador i.MX 8M proporciona un sólido recurso informático. Utilizados conjuntamente, los múltiples núcleos del procesador ofrecen una plataforma informática poderosa capaz de gestionar los requisitos conflictivos tanto para el rendimiento en tiempo real como para la ejecución del software de aplicación que puede confundir el diseño de productos inteligentes. Un producto inteligente basado en este procesador puede, por ejemplo, utilizar el núcleo Cortex-M7 para procesar flujos de audio en tiempo real, mientras que utiliza algoritmos que se ejecutan en uno o más núcleos del Cortex-A53 para analizar los datos resultantes y proporcionar a los usuarios una visualización gráfica en 3D de los resultados.

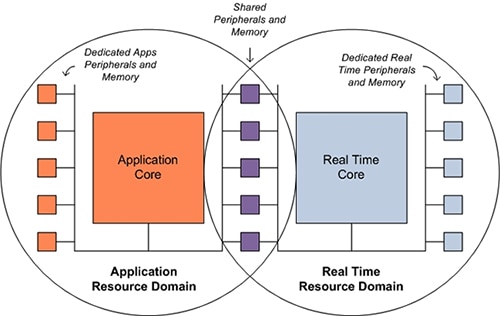

Sin embargo, para realizar de manera fiable este tipo de procesamiento heterogéneo y coordinado de núcleos múltiples, un sistema de núcleos múltiples requiere un manejo cuidadoso de las operaciones de procesamiento y el intercambio de datos entre los diversos núcleos, los bloques de hardware especializados y los periféricos. En el Nano procesador i.MX 8M este manejo está incorporado en mecanismos basados en hardware para semáforos y mensajería que suelen ser utilizados por servicios de software de bajo nivel en entornos de multiprocesamiento.

En los sistemas embebidos, esta ejecución orquestada también se extiende a los recursos de hardware como la memoria y los periféricos. Para esta tarea, el procesador integra un controlador de dominio de recursos (RDC) dedicado, diseñado para garantizar el intercambio seguro de recursos cuando sea apropiado, o el aislamiento fiable cuando sea necesario. Como resultado, el software de aplicaciones y el código en tiempo real pueden controlar cada uno de los recursos dedicados a su dominio y al mismo tiempo compartir un conjunto de recursos comunes (figura 2).

Figura 2: Los mecanismos basados en hardware en el Nano procesador NXP i.MX 8M aseguran el aislamiento de los recursos dedicados al dominio de aplicación Cortex-A53 o al dominio en tiempo real Cortex-M7, al tiempo que permiten compartir recursos de forma segura cuando es necesario. (Fuente de la imagen: NXP)

Figura 2: Los mecanismos basados en hardware en el Nano procesador NXP i.MX 8M aseguran el aislamiento de los recursos dedicados al dominio de aplicación Cortex-A53 o al dominio en tiempo real Cortex-M7, al tiempo que permiten compartir recursos de forma segura cuando es necesario. (Fuente de la imagen: NXP)

Soporte especializado para productos inteligentes

Utilizando sólo los múltiples núcleos y las capacidades de intercambio de recursos del Nano procesador i.MX 8M, los desarrolladores pueden crear aplicaciones sofisticadas para los productos inteligentes emergentes construidos con asistentes de voz y gráficos 3D. Estas aplicaciones obtienen un mayor rendimiento y reducen su huella en el software gracias al soporte de hardware especializado para los productos inteligentes incorporados en los nano Nano procesadores i.MX 8M.

En cuanto a los gráficos, la unidad de procesamiento gráfico (GPU) integrada del procesador proporciona aceleración de gráficos en 2D y 3D, y es compatible con las bibliotecas gráficas estándar, incluyendo Vulkan, Open Computing Language (OpenCL) y Open Graphics Library (OpenGL). Un controlador integrado de interfaz de pantalla de cristal líquido (LCDIF) soporta pantallas a 1080p60 (1080 progresivas de 60 fotogramas por segundo).

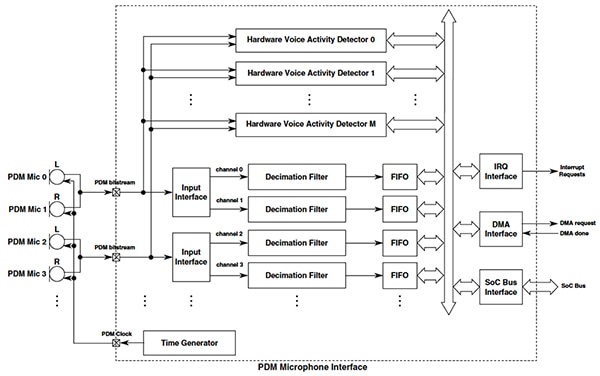

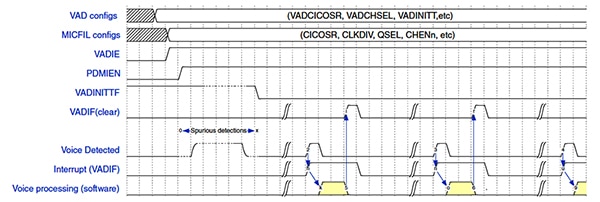

Mientras que la GPU en el chip descarga el procesamiento de la pantalla de los núcleos, otro conjunto de subsistemas de hardware descarga una variedad de tareas de procesamiento de audio que normalmente ralentizan los sistemas basados en procesadores convencionales. Para procesar las entradas de los micrófonos, la interfaz de micrófono de modulación de densidad de pulso (PDM) del procesador (MICFIL) proporciona un conducto de varias etapas diseñado para generar datos filtrados de modulación de código de pulso (PCM) de 16 bits a partir de la entrada de 1 bit recibida de los micrófonos PDM (Figura 3).

Figura 3: El subsistema de interfaz del Nano procesador NXP i.MX 8M para la entrada de micrófono PDM combina conductos de hardware separados para el procesamiento de la señal de audio y la detección de la actividad de la voz. (Fuente de la imagen: NXP)

Figura 3: El subsistema de interfaz del Nano procesador NXP i.MX 8M para la entrada de micrófono PDM combina conductos de hardware separados para el procesamiento de la señal de audio y la detección de la actividad de la voz. (Fuente de la imagen: NXP)

Para una aplicación típica basada en la voz, los diseñadores solo tienen que conectar un micrófono PDM a uno de los ocho canales PDM compatibles con el procesador. Dentro del subsistema de interfaz de micrófono PDM, una interfaz de entrada combina datos PDM multiplexados en el tiempo de un par de micrófonos para formar un carril que comprende canales izquierdo y derecho.

En la siguiente etapa para cada canal, un filtro de diezmado programable dedicado proporciona diferentes bandas de paso dependiendo de la tasa de salida deseada y uno de los seis ajustes de selección de calidad (QSEL) incluyendo alta, media y baja calidad, así como tres niveles adicionales de muy baja calidad. Por ejemplo, a una velocidad de salida de 48 kilohercios (kHz), los modos de muy baja calidad establecen la banda de paso del filtro en 10.5 Hz a 11.25 kHz en comparación con una banda de paso de 21 Hz a 22.5 kHz para los modos de alta, media y baja calidad. Por último, los resultados de cada canal se ponen a disposición en memorias separadas de primera entrada, primera salida (FIFO) para cada canal para generar interrupciones, transferencia mediante DMA o acceso al bus.

Detección de la actividad de la voz basada en el hardware

En paralelo con este conducto de acondicionamiento de la señal de audio, la interfaz de micrófono PDM proporciona un conjunto de detectores de actividad de voz de hardware (HWVAD) que supervisan los canales de entrada de micrófono deseados. (Nota: La figura de arriba sugiere que cada HWVAD está asociado a un carril, pero la documentación dice canales, y el nombre de un registro, VADCHSEL, lo apoya). Para apoyar el funcionamiento del HWVAD, el procesador proporciona un rico conjunto de registros de dispositivos que permiten a los desarrolladores definir la configuración específica del HWVAD necesaria para su aplicación (Tabla 1).

|

Tabla 1: Registros del Nano procesador NXP i.MX 8M que se utilizan normalmente para configurar los detectores de actividad de voz de hardware integrados en la interfaz de micrófono PDM del procesador (MICFIL). (Fuente de la tabla: DigiKey, basada en los datos de NXP)

Basándose en estos ajustes de registro, el HWVAD utiliza algoritmos de detección de voz incorporados para identificar la actividad de la voz. Al ser detectado, el HWVAD genera una interrupción para despertar un núcleo, generalmente la Cortex-M7, para su posterior procesamiento (Figura 4).

Figura 4: Utilizando los ajustes de configuración programados por el desarrollador, los detectores de actividad de voz del hardware del Nano procesador NXP i.MX 8M permiten que los núcleos del procesador queden inactivos o realicen otro tipo de procesamiento hasta que se detecte una voz y se requiera un mayor procesamiento de la misma. (Fuente de la imagen: NXP)

Figura 4: Utilizando los ajustes de configuración programados por el desarrollador, los detectores de actividad de voz del hardware del Nano procesador NXP i.MX 8M permiten que los núcleos del procesador queden inactivos o realicen otro tipo de procesamiento hasta que se detecte una voz y se requiera un mayor procesamiento de la misma. (Fuente de la imagen: NXP)

En una aplicación de asistente de voz, el núcleo comprobaría el flujo de audio para encontrar la palabra apropiada para la activación. Si se detecta la palabra de activación, el núcleo normalmente proporciona el flujo de audio a los servicios de asistencia de voz basados en la nube que soporta la aplicación.

Además del subsistema de interfaz de micrófono PDM, el Nano procesador i.MX 8M también proporciona cinco módulos de interfaz de audio síncrono (SAI) que admiten una serie de formatos de audio estándar, entre ellos Sonido Inter-IC (I2S), códec de audio 97 (AC97), audio multiplexado por división de tiempo (TDM) y Direct Stream Digital (DSD), así como datos de códec o procesamiento de señales digitales (DSP).

Para cumplir con sus requisitos específicos de aplicación, los desarrolladores a menudo se ven obligados a convertir las muestras de entrada de audio a alguna otra frecuencia de muestreo y resolución requeridas. En lugar de utilizar ciclos de procesador para realizar esta tarea común, el Nano procesador i.MX 8M integra un subsistema dedicado de convertidor de frecuencia de muestreo asíncrono (ASRC).

Al poder procesar simultáneamente hasta 32 canales de audio, el ASRC convierte automáticamente las muestras de la fuente a la frecuencia de muestreo deseada (entre 8 kHz y 384 kHz) y a la resolución (formato de punto flotante o punto fijo de precisión única del IEEE a 16, 20, 24 o 32 bits por muestra). En el proceso, el ASRC convierte todos los datos de entrada a un formato de punto flotante de 64 bits del IEEE para asegurar una conversión precisa hacia arriba o hacia abajo de los datos de las muestras de audio según sea necesario para lograr el resultado deseado.

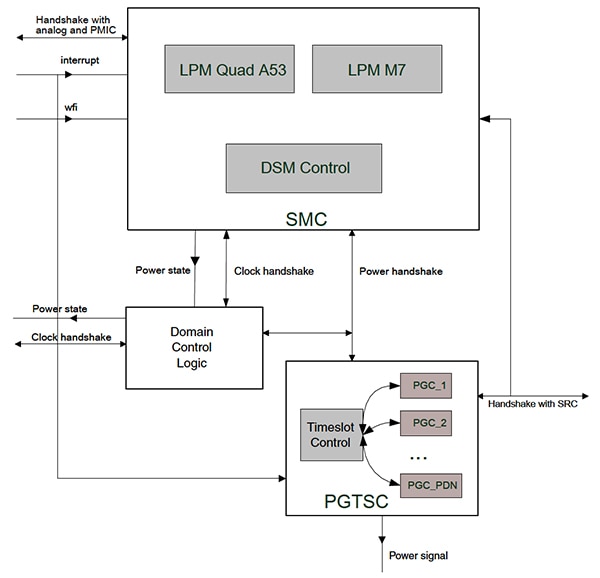

Administración de la energía usando un controlador general de energía

Con su amplia integración de núcleos de procesador y subsistemas de hardware, la arquitectura del Nano procesador NXP i.MX 8M combina una serie de dominios de potencia y modos de potencia separados incorporados en los núcleos y subsistemas individuales. Para gestionar la energía de este conjunto de núcleos y bloques especializados, el Nano procesador i.MX 8M incluye un sofisticado controlador general de energía (GPC) diseñado para coordinar múltiples características de gestión de la energía. Dentro del GPC, el controlador de modo del sistema (SMC) gestiona el modo de baja potencia (LPM) de cada núcleo y el modo de inactivadad profunda (DSM) en general, mientras que un controlador de intervalos de tiempo de compuerta de potencia (PGTSC) gestiona las características de compuerta de reloj utilizadas para reducir la potencia del sistema al desactivar la potencia de los subsistemas inactivos (Figura 5).

Figura 5: Para mejorar la optimización de la potencia a nivel de sistema, el Nano procesador NXP i.MX 8M integra un completo controlador de potencia que gestiona las funciones de compuerta de potencia y los modos de baja potencia incorporados en los núcleos del procesador. (Fuente de la imagen: NXP)

Figura 5: Para mejorar la optimización de la potencia a nivel de sistema, el Nano procesador NXP i.MX 8M integra un completo controlador de potencia que gestiona las funciones de compuerta de potencia y los modos de baja potencia incorporados en los núcleos del procesador. (Fuente de la imagen: NXP)

Bajo el control del software o del hardware, el GPC utiliza 20 franjas horarias diferentes en el PGTSC para encender o apagar cualquiera de los múltiples dominios de potencia de reloj en el procesador. Aquí, el controlador de la franja horaria trabaja secuencialmente a través de estas franjas horarias, activando cualquier petición de encendido o apagado antes de proceder a la siguiente franja. Además de cumplir con los requisitos específicos de secuenciación de energía, este enfoque permite a los desarrolladores reducir la corriente de rampa durante el encendido del sistema, o cuando se activa el sistema de un modo de bajo consumo o de inactivdad profunda.

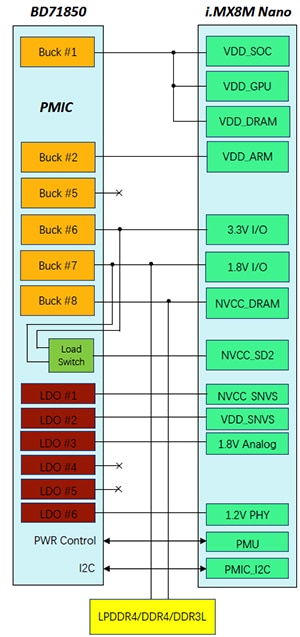

Suministrar los múltiples dominios de potencia del Nano procesador i.MX 8M es sencillo. Diseñado específicamente para ser compatible con el Nano procesador NXP i.MX 8M, el circuito integrado de gestión de energía (PMIC) BD71850MWV de ROHM Semiconductor proporciona todos los rieles de energía requeridos por el procesador así como otros periféricos del sistema. De hecho, el PMIC BD71850MWV integra su propio secuenciador de potencia, simplificando aún más la ejecución segura del encendido y apagado, no sólo para el procesador sino también para la memoria externa, los sensores u otros dispositivos del sistema (Figura 6). Para los desarrolladores, la incorporación del PMIC BD71850MWV en un diseño no requiere ningún componente adicional, más allá de los condensadores de desacoplamiento habituales (no se muestra).

Figura 6: Los múltiples núcleos y subsistemas de hardware del Nano procesador NXP iMX 8M impulsan la necesidad de múltiples carriles de suministro, pero el circuito integrado de gestión de energía (PMIC) ROHM BD71850MWV proporciona una solución lista. (Fuente de la imagen: NXP)

Figura 6: Los múltiples núcleos y subsistemas de hardware del Nano procesador NXP iMX 8M impulsan la necesidad de múltiples carriles de suministro, pero el circuito integrado de gestión de energía (PMIC) ROHM BD71850MWV proporciona una solución lista. (Fuente de la imagen: NXP)

Apoyo al desarrollo

Aunque los requisitos de la interfaz de hardware para los diseños basados en la nanotecnología i.MX 8M son relativamente simples, NXP permite a los desarrolladores evitar incluso esta tarea de diseño relativamente sencilla para evaluar el procesador o crear prototipos de nuevos productos inteligentes. Proporcionando un kit de desarrollo completamente implementado y un diseño de referencia para el procesador Nano i.MX 8M, el kit de evaluación 8MNANOD4-EVK combina el procesador Nano i.MX 8M y el PMIC BD71850MWV con el módulo transceptor Wi-Fi/Bluetooth LBEE5HY1MW de Murata Electronics para proporcionar una plataforma para la evaluación inmediata y el desarrollo de prototipos. Junto con las múltiples opciones de interfaz y los conectores asociados, el kit de evaluación incluye un conjunto completo de dispositivos de memoria externa, incluyendo la memoria RAM estática y dinámica (SDRAM), el flash NOR y el flash NAND. Usando el kit de evaluación, los desarrolladores pueden explorar diferentes modos operativos y configuraciones, incluyendo el arranque desde una flash externa o el arranque seguro usando imágenes de arranque firmadas.

Cuando los desarrolladores están listos para proceder con su propio desarrollo de software personalizado, NXP proporciona controladores, paquetes de soporte de placas (BSP) y middleware diseñados para trabajar con su propio entorno de desarrollo integrado (IDE) MCUXpresso, así como IDE de terceros. Para construir aplicaciones diseñadas para aprovechar los métodos de aprendizaje automático, los desarrolladores pueden recurrir al entorno de desarrollo de software de aprendizaje automático NXP eIQ y a las bibliotecas de inferencia optimizadas i.MX, como eIQ para TensorFlow Lite para la inferencia basada en Cortex-M7, o el puerto de NXP del kit de desarrollo de software de red neural de Arm (NN SDK) para la inferencia basada en Cortex-A53.

Conclusión

Impulsados por la rápida aceptación de los productos de asistencia de voz, los productos inteligentes de la próxima generación se enfrentan a crecientes expectativas no sólo de un mejor soporte de audio, sino también de un mayor rendimiento, mejores gráficos y un funcionamiento eficiente de la energía. Sin embargo, para los desarrolladores, el diseño de sistemas eficaces para estos productos requiere una combinación de ejecución de software de aplicaciones de alto rendimiento y capacidades en tiempo real de baja latencia que ha sido difícil de lograr dentro de sus limitaciones de tamaño, costo y potencia asociadas. Gracias a la disponibilidad de una familia escalable de procesadores multinúcleo de NXP, los desarrolladores pueden cumplir fácilmente los requisitos de diseño de productos inteligentes en una amplia gama de segmentos de aplicación, como el consumidor, el industrial y el médico, entre otros.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.