Utilice un único procesador de HMP de potencia ultra baja para cargas de trabajo de procesamiento de aplicaciones y en tiempo real

Colaboración de Editores de DigiKey de América del Norte

2019-08-06

Los consumidores esperan que los componentes electrónicos personales y otros dispositivos móviles brinden tanto una respuesta más rápida y una mayor funcionalidad como una duración de la batería más prolongada. Sin embargo, para los desarrolladores, los requisitos de respuesta en tiempo real y rendimiento de muchas aplicaciones dictaron el uso de procesadores separados a fin de satisfacer estas conflictivas demandas. Esto agrega costo, potencia y espacio, así como también la distribución del hardware y la complejidad del software.

Un mejor enfoque sería integrar el hardware requerido en un solo chip. Ingrese dispositivos de HMP (procesamiento heterogéneo multinúcleo). Con múltiples núcleos de diferentes tipos, estos procesadores pueden ofrecer ventajas tales como la optimización del rendimiento, la reducción del consumo de potencia y la mejora de la seguridad y de la confiabilidad del sistema.

Este artículo describe cómo los desarrolladores pueden usar un HMP de NXP Semiconductors para satisfacer la demanda de estas cargas de trabajo mixtas sin que se vean comprometidos los requisitos de potencia baja y complejidad reducida del diseño.

Requisitos cambiantes

Los avances en la tecnología de sensores y los algoritmos de procesamiento de datos crearon oportunidades significativas para que los desarrolladores gestionen las demandas conflictivas de adquisición de datos en tiempo real y de ejecución de algoritmos computacionalmente intensivos. En el pasado, los desarrolladores generalmente dividían estas cargas de trabajo en sistemas separados.

En el nivel más bajo de jerarquía de la red, los procesadores integrados, tales como los basados en el núcleo Arm® Cortex®-M4, recogían los datos mediante la ejecución del código optimizado en un RTOS (sistema operativo en tiempo real) o sin sistema operativo. En un nivel superior de jerarquía, los procesadores de aplicaciones de alto rendimiento como los basados en el núcleo Arm Cortex-A7 ejecutaban, en cambio, algoritmos de análisis de datos, mediante la ejecución del código de aplicaciones en sistemas operativos familiares como Linux o Android.

El auge de los sistemas informáticos periféricos ha acercado la ejecución del código de aplicación a la fuente de datos. De hecho, la demanda de una respuesta más rápida por parte de algoritmos de análisis más complejos ha llevado a los requisitos de procesamiento de aplicaciones a ser dispositivos finales en sí mismos. Con mayor frecuencia, los consumidores esperan capacidades de análisis sofisticadas, incluida la incorporación de los métodos de inteligencia artificial en dispositivos como sensores de la IoT (Internet de las cosas), tecnología vestible y otros productos de baja potencia.

El rol del procesamiento heterogéneo multinúcleo

La aparición de los dispositivos HMP que combinan núcleos de procesadores integrados y de aplicaciones ha ayudado a los desarrolladores a manejar cargas de trabajo mixtas de manera más eficiente en muchas aplicaciones. Los procesadores HMP integran diferentes núcleos, y cada uno de ellos está optimizado para cumplir con los diferentes requisitos asociados con la carga de trabajo del producto objetivo. Con la familia de procesadores NXP i.MX 7ULP (potencia ultra baja), los desarrolladores pueden aprovechar las capacidades de rendimiento de la arquitectura de un HMP para satisfacer la demanda intransigente de alto rendimiento y larga duración de la batería por parte de los consumidores en los productos ULP de próxima generación.

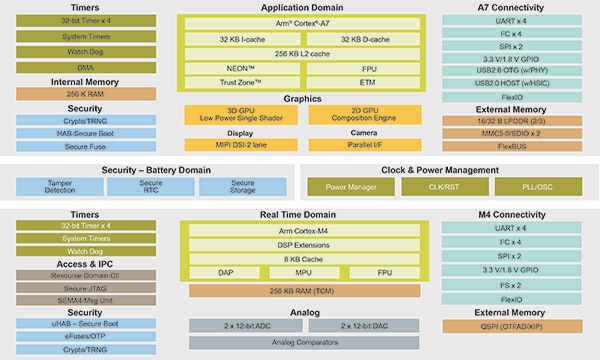

Disponibles en la versión para consumidores (MCIMX7U5DVP07SC) y en la versión industrial (MCIMX7U5CVP06SC), los procesadores i.MX 7ULP integran sus núcleos heterogéneos con unidades de procesamiento de gráficos, aceleradores de seguridad, controladores de memoria y un conjunto completo de interfaces periféricas (Figura 1).

Figura 1: Junto con un amplio complemento de módulos y periféricos, la familia de procesadores de aplicaciones NXP i.MX 7ULP combina un núcleo Arm Cortex-M4 para el procesamiento en tiempo real con un núcleo Arm Cortex-A7 para el procesamiento de aplicaciones. Utiliza dominios de potencia separados para optimizar la potencia y el rendimiento. (Fuente de la imagen: NXP)

Figura 1: Junto con un amplio complemento de módulos y periféricos, la familia de procesadores de aplicaciones NXP i.MX 7ULP combina un núcleo Arm Cortex-M4 para el procesamiento en tiempo real con un núcleo Arm Cortex-A7 para el procesamiento de aplicaciones. Utiliza dominios de potencia separados para optimizar la potencia y el rendimiento. (Fuente de la imagen: NXP)

La familia de los NXP i.MX 7ULP, creada específicamente para diseños portátiles con limitaciones de potencia, aborda los requisitos emergentes mediante la combinación de un núcleo Arm Cortex-A7 y un núcleo Cortex-M4, cada uno suministrado por un dominio de potencia separado. Además, el uso de diferentes islas de potencia permite que distintos módulos se apaguen de manera selectiva cuando no se necesitan. Como se describe a continuación, las características sofisticadas de administración de potencia integradas en los dispositivos i.MX 7ULP les permiten a los desarrolladores usar estos dominios e islas de potencia para ajustar el rendimiento y el consumo de potencia según lo requieran las aplicaciones.

Optimización de la potencia

Al diseñar la familia de los i.MX 7ULP, NXP incorporó características de optimización de potencia y rendimiento en los dispositivos en toda la arquitectura comenzando por el diseño del chip.

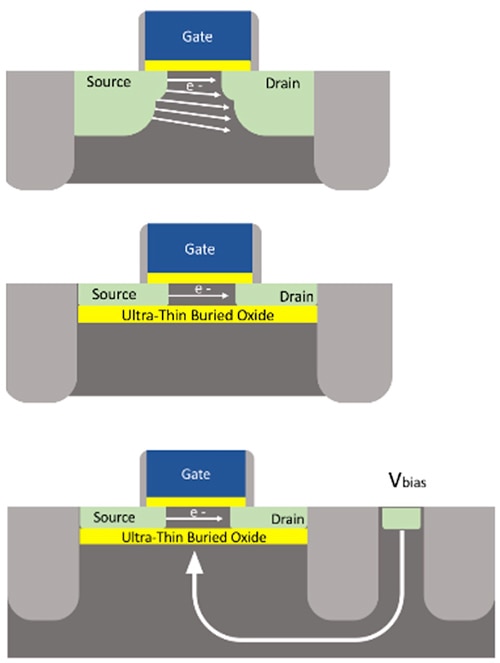

En el nivel más fundamental, la familia de los i.MX 7ULP combina métodos de fabricación que reducen la corriente de fuga con geometrías de transistores que reducen los elementos parásitos y, así, disminuyen el consumo dinámico de potencia. A diferencia de las estructuras de transistores convencionales (Figura 2, arriba), los dispositivos i.MX 7ULP están fabricados con un óxido enterrado ultra fino (Figura 2, centro) que reduce el flujo de electrones desde la fuente hasta el drenaje y, de este modo, se reduce la corriente de fuga; una mejora adicional les permite a los diseñadores agregar FBB (polarización hacia adelante) o RBB (polarización hacia atrás) (Figura 2, abajo).

Figura 2: Un transistor convencional puede exhibir una fuga considerable a medida que los electrones fluyen desde la fuente hasta el drenaje (arriba), pero la familia de los NXP i.MX 7ULP está fabricada con un óxido enterrado ultra fino que impide el flujo de electrones (medio) y con una estructura que acelera o ralentiza el flujo de electrones con FBB o RBB (abajo). (Fuente de la imagen: NXP)

Figura 2: Un transistor convencional puede exhibir una fuga considerable a medida que los electrones fluyen desde la fuente hasta el drenaje (arriba), pero la familia de los NXP i.MX 7ULP está fabricada con un óxido enterrado ultra fino que impide el flujo de electrones (medio) y con una estructura que acelera o ralentiza el flujo de electrones con FBB o RBB (abajo). (Fuente de la imagen: NXP)

Cuando la eficiencia energética es una prioridad, los desarrolladores pueden usar la RBB para reducir el flujo de electrones y reducir aún más la corriente de fuga y el consumo general de potencia del dispositivo a expensas de un rendimiento más bajo. Por el contrario, los desarrolladores pueden usar la FBB, que mejora el flujo de electrones, para aumentar el rendimiento a expensas de un mayor consumo de potencia debido a una mayor corriente de fuga.

En el nivel de diseño del chip, la familia de los i.MX 7ULP incorpora múltiples técnicas que incluyen el escalado dinámico de frecuencia (DFS) y el escalado dinámico de voltaje (DVS), la conmutación de reloj basada en software y la conmutación de potencia basada en software. Además de reducir el consumo de potencia de diferentes periféricos, los desarrolladores pueden usar estas características para cerrar, de manera selectiva, bloques de memoria interna o colocar la memoria en distintos modos de ahorro de potencia.

A nivel arquitectónico, la capacidad de sintonizar la potencia y el rendimiento se amplía aún más con el uso de múltiples dominios de potencia, incluidos los dominios de potencia separados, mencionados anteriormente, para los subsistemas Cortex-A7 y Cortex-M4.

Cada uno de los dominios de potencia del núcleo del procesador incluye controladores de FBB y RBB, reguladores de LDO (caída baja) y monitores de HVD (detección de alto nivel) y LVD (detección de bajo nivel) diseñados para señalizar variaciones de suministro por encima o por debajo de los umbrales designados. Un monitor separado de PoR (reinicio por activación) rastrea el nivel de voltaje en el dominio de potencia permanentemente activo.

Junto con los dominios de potencia de núcleo separados, los dominios de potencia individuales también controlan las funciones del sistema, como el hardware permanentemente activo, mientras que un dominio con batería administra la potencia para las funciones críticas, incluido el reloj en tiempo real y un módulo de almacenamiento seguro no volátil, entre otros. Al igual que con los dominios de potencia de núcleo, cada uno de estos dominios de potencia especializados admite un conjunto integral de características especializadas de ahorro de potencia (de las que hay demasiadas como para abordarlas individualmente en un solo artículo).

Para dar un ejemplo, el dominio de potencia para la funcionalidad permanentemente activa incluye un módulo de LLWU (unidad de activación de fuga baja) que les permite a los desarrolladores utilizar múltiples pines externos o módulos internos como fuente de activación para los modos especiales de potencia de fuga baja descritos a continuación.

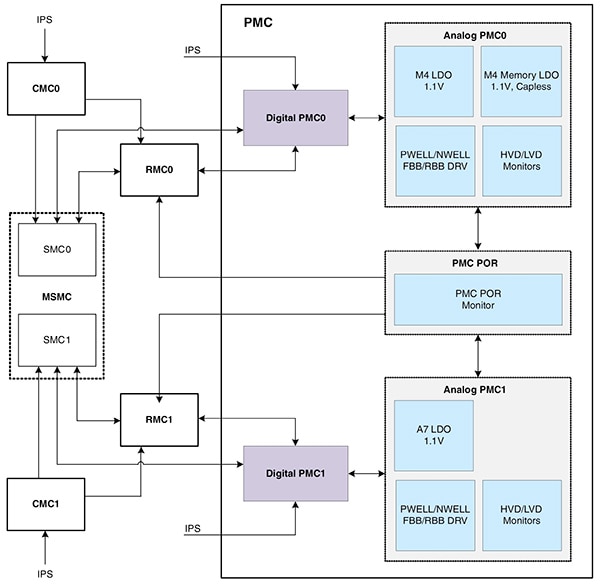

Estas características de la arquitectura se unen en el PMC (controlador de administración de potencia) integrado del dispositivo, que maneja estos dominios de potencia separados y las islas de potencia del dispositivo (Figura 3).

Figura 3: La familia de los NXP i.MX 7ULP integra una sofisticada capacidad de control que les permite a los desarrolladores configurar de manera programática los dominios y las islas de potencia para ajustar la potencia y el rendimiento a fin de cumplir con los requisitos cambiantes de las aplicaciones. (Fuente de la imagen: NXP)

Figura 3: La familia de los NXP i.MX 7ULP integra una sofisticada capacidad de control que les permite a los desarrolladores configurar de manera programática los dominios y las islas de potencia para ajustar la potencia y el rendimiento a fin de cumplir con los requisitos cambiantes de las aplicaciones. (Fuente de la imagen: NXP)

En este enfoque, los desarrolladores inician las transiciones de modo de potencia mediante el envío de órdenes a través del bus de IPS (subsistema periférico inteligente) normal a una unidad de control que comprende tres módulos estrechamente relacionados:

- CMC (controlador de modo núcleo), que admite múltiples funciones principales

- MSMC (controlador de modo del sistema multinúcleo), que comprende el 0SMC0 (controlador de modo del sistema) para el dominio de potencia Cortex-M4 y SMC1 para el dominio de potencia Cortex-A7, que maneja la secuenciación entre diferentes modos de potencia, controla eventos utilizados para iniciar las transiciones de modo de potencia y, generalmente, controla las características de la potencia, el reloj y la memoria asociadas con la optimización de la potencia

- RMC (controlador de modo de reinicio), que maneja las funciones de reinicio del chip

Ajuste del rendimiento y de la potencia

Para todas sus capacidades de administración de potencia, la familia de los i.MX 7ULP presenta un modelo de programación familiar para los desarrolladores. Al igual que con otros procesadores avanzados, los dispositivos i.MX 7ULP alcanzan diferentes estados de operación de baja potencia a través de una serie de modos programables de baja potencia. De hecho, los núcleos del procesador i.MX 7ULP admiten varios modos de baja potencia controlados por software que les permiten a los desarrolladores reducir el consumo de potencia al nivel más bajo posible de acuerdo con la funcionalidad requerida.

Al utilizar estos distintos modos de baja potencia, los desarrolladores pueden configurar uno o ambos núcleos y sus subsistemas en diferentes variaciones de un modo RUN normal, modo WAIT y modo STOP.

El modo RUN normal y el modo HSRUN de alta velocidad proporcionan un funcionamiento de alto rendimiento para admitir partes de una aplicación de cálculo intensivo. En el modo HSRUN, el subsistema de núcleo funciona a su frecuencia más alta. Si la aplicación puede tolerar un rendimiento inferior, los desarrolladores pueden configurar el núcleo en modo de ejecución de VLPR (muy baja potencia) para que funcione a una frecuencia máxima de 48 MHz (megahercios) con un consumo de potencia menor correspondiente.

En el modo WAIT normal, los periféricos funcionan en su totalidad, pero el núcleo se encuentra con un bloqueo de reloj, esperando en un estado estático, pero listo para activarse al recibir una señal de WFI (espera por interrupción). Con este modo, los desarrolladores pueden permitir que las operaciones periféricas autónomas llenen los búferes o utilicen transacciones de DMA (acceso directo a la memoria) para llenar la memoria del sistema antes de emitir una interrupción que saque al núcleo de su estado WAIT. El modo de espera de VLPW permite que los periféricos continúen las operaciones a la frecuencia reducida, pero bloquea los relojes del núcleo.

En aplicaciones de tecnología vestible o dispositivos portátiles, el sistema puede enfrentar largos períodos de inactividad, y puede interrumpirse periódicamente por estallidos de actividad. En estos casos, la capacidad de ahorrar potencia es crítica para la vida útil de la batería. Cuando la aplicación puede tolerar un tiempo de activación más lento para el núcleo, la capacidad de colocar el dispositivo en estados de suspensión aún más profundos que RUN, WAIT o variaciones de muy baja potencia es una opción particularmente efectiva. Para respaldar este enfoque, los desarrolladores pueden colocar cada subsistema de núcleo i.MX 7ULP en un estado de suspensión más profundo que requiere de diferentes cantidades de tiempo de activación:

- En el estado STOP, algunos periféricos pueden funcionar de forma asíncrona, pero el núcleo permanece en un estado estático con tiempos de activación de 7 μs (microsegundos) para el Cortex-A7 o 7 μs para el Cortex-M4

- En el modo de parada de VLPS, las operaciones periféricas están aún más limitadas, pero el núcleo permanece en un estado estático con tiempos de activación de 21.5 μs (Cortex-A7) o de 9 μs (Cortex-M4).

Para las aplicaciones con requisitos de potencia aún más estrictos, los desarrolladores pueden configurar cada núcleo en los siguientes modos especiales de fuga baja que apagan más subsistemas de los dispositivos:

- LLS (parada de fuga baja), que bloquea el reloj del núcleo, el bus y los periféricos y deja al núcleo en un estado de WFI, lo que resulta en un tiempo de activación de 40 μs (Cortex-A7) o 58 μs (Cortex-M4)

- VLLS (parada de fuga muy baja), que bloquea el reloj del dominio de potencia completo del núcleo, lo que lleva a tiempos de activación más prolongados, como 60 μs para el Cortex-A7 o 375 μs para el Cortex-M4

Para un ahorro de potencia aún mayor, los desarrolladores pueden usar RBB en algunos modos de potencia, incluidos el de VLPS y de LLS con una reducción correspondiente en el rendimiento y un aumento incremental en el tiempo de activación de aproximadamente 2 a 4 μs.

Por el contrario, cuando se necesita lidiar con cargas de trabajo informáticas intensivas, los desarrolladores pueden ejecutar los núcleos en un modo especial de HSRUN (ejecución de alta velocidad). El modo HSRUN cambia la frecuencia normal de operación del núcleo Cortex-A7 de 500 MHz a un modo de sobremarcha que funciona a 720 MHz.

Con este excelente nivel de control, los desarrolladores pueden configurar el i.MX 7ULP para cumplir incluso con los requisitos de potencia extremos sin sacrificar la funcionalidad esencial. Por ejemplo, una aplicación puede necesitar el menor consumo de potencia posible, pero requiere tanto de la funcionalidad en tiempo real del núcleo Cortex-M4 como del uso de periféricos específicos o de la memoria del subsistema Cortex-A7. En este caso, el desarrollador puede colocar al subsistema Cortex-A7 en estado STOP o VLPS y acceder a su memoria o periféricos desde el Cortex-M4 a medida que ese núcleo realiza sus operaciones en tiempo real. Para un mayor ahorro de potencia, los desarrolladores pueden usar el reloj Cortex-M4 para controlar los periféricos del Cortex-A7.

Implementación simple del sistema

Para implementar un sistema de baja potencia con el i.MX 7ULP, los desarrolladores pueden elegir entre los modos y configuraciones de potencia programables por software disponibles para que coincidan con los requisitos de potencia y rendimiento. Con respecto al hardware, el diseño del sistema es aún más simple.

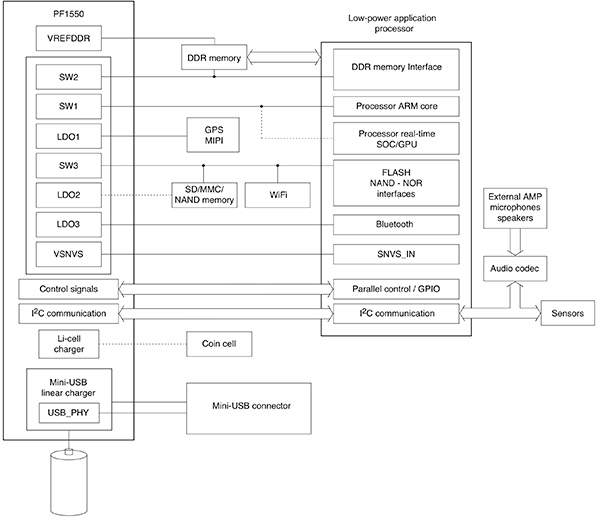

Para las aplicaciones típicas, los desarrolladores pueden simplemente combinar un procesador i.MX 7ULP con el circuito integrado de PMIC (administración de potencia) NXP MC32PF1550A3EPR2 para completar un diseño capaz de manejar cargas de trabajo mixtas sin comprometer los presupuestos de potencia limitados (Figura 4).

Figura 4: El circuito integrado de administración de potencia NXP MC32PF1550A3EPR2 proporciona el conjunto completo de fuentes de suministro requeridas por el procesador NXP i.MX 7ULP, y así reduce el diseño del hardware a una combinación directa de estos dos dispositivos y de algunos componentes pasivos. (Fuente de la imagen: NXP)

Figura 4: El circuito integrado de administración de potencia NXP MC32PF1550A3EPR2 proporciona el conjunto completo de fuentes de suministro requeridas por el procesador NXP i.MX 7ULP, y así reduce el diseño del hardware a una combinación directa de estos dos dispositivos y de algunos componentes pasivos. (Fuente de la imagen: NXP)

Diseñado específicamente para cumplir con los requisitos de suministro de procesadores NXP tales como los de la familia i.MX 7ULP, el MC32PF1550A3EPR2 integra tres reguladores buck de modo conmutado (SW1, SW2, SW3), tres reguladores de baja caída (LDO1, LDO2, LDO3), una fuente de voltaje de referencia de memoria, un cargador completo de batería de litio con una única celda y una memoria OTP (programable una sola vez) para la configuración del dispositivo.

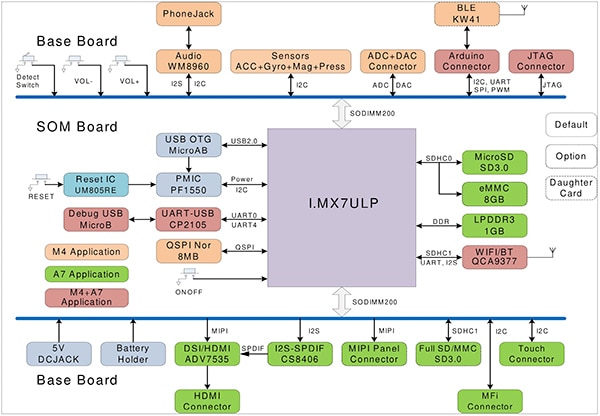

Con el kit de evaluación MCIMX7ULP-EVK , NXP demuestra la simple interfaz de hardware necesaria para combinar el MC32PF1550A3EPR2 PMIC y el dispositivo i.MX 7ULP. Junto con una placa de SOM (sistema en módulo) que contiene el procesador i.MX 7ULP y el MC32PF1550A3EPR2 PMIC, el kit incluye una placa base con múltiples sensores, capacidad inalámbrica, un CODEC de audio, un conector SD y otros conectores, incluidos el JTAG y el Arduino (Figura 5).

Figura 5: El kit de evaluación MCIMX7ULP-EVK combina una placa de sistema en módulo que contiene un procesador i.MX 7ULP y un MC32PF1550A3EPR2 PMIC con una placa base con sensores, conectores y otros componentes necesarios para acelerar el desarrollo del software con dispositivos i.MX 7ULP. (Fuente de la imagen: NXP)

Figura 5: El kit de evaluación MCIMX7ULP-EVK combina una placa de sistema en módulo que contiene un procesador i.MX 7ULP y un MC32PF1550A3EPR2 PMIC con una placa base con sensores, conectores y otros componentes necesarios para acelerar el desarrollo del software con dispositivos i.MX 7ULP. (Fuente de la imagen: NXP)

Si bien el kit de evaluación proporciona una funcionalidad lista para el uso, NXP también les brinda a los desarrolladores archivos de diseño descargables, herramientas y paquetes de soporte de placa para un software personalizado que utiliza FreeRTOS para códigos en tiempo real y Linux o Android para códigos de aplicaciones.

Conclusión

La demanda de una funcionalidad más sofisticada y de una mayor duración de la batería en los productos móviles ha obligado, tradicionalmente, a los desarrolladores a un cierto nivel de negociación entre la potencia y el rendimiento. Además, las crecientes expectativas de datos oportunos de más sensores en dispositivos IoT, tecnología vestible y otros productos portátiles ha obligado a una mayor negociación entre las capacidades en tiempo real y el rendimiento a nivel de las aplicaciones.

Sin embargo, como se muestra, los desarrolladores pueden recurrir a arquitecturas HMP como las utilizadas en la familia de procesadores i.MX 7ULP de NXP para cumplir con los estrictos requisitos de potencia ultra baja sin sacrificar las capacidades.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.