Comprender y minimizar el impacto de las fluctuaciones en los enlaces de alta velocidad

Colaboración de Editores de DigiKey de América del Norte

2023-12-21

Los osciladores de reloj marcan el ritmo de los circuitos modernos al marcar el paso de los componentes del sistema. A medida que la velocidad del sistema aumenta a cientos de megahercios (MHz) y más, estos relojes deben ser más rápidos y proporcionar fluctuaciones muy bajas, normalmente inferiores a 100 femtosegundos (fs), para mantener el rendimiento del sistema. También deben mantener sus especificaciones de fluctuaciones bajas a lo largo del tiempo, a pesar de las variaciones de temperatura y voltaje.

El ruido y la distorsión del trayecto de la señal provocan algunas fluctuaciones que pueden reducirse mediante técnicas de reclocking y retemporizador. Sin embargo, las fluctuaciones también las genera la fuente de reloj, que suele ser un oscilador. Esto se debe a diversos fenómenos físicos, como el ruido térmico, las imperfecciones del proceso, el ruido de la fuente de alimentación, otros ruidos externos que penetran en el oscilador del reloj, las tensiones de los materiales y muchos otros factores sutiles. Independientemente de la fuente, corresponde al diseñador hacer todo lo posible para minimizar las fluctuaciones de reloj inherentes, ya que las deficiencias no son reversibles.

En este artículo se analizan las fluctuaciones desde distintos puntos de vista. A continuación, presenta diferentes osciladores de reloj de Abracon LLC y muestra cómo se pueden minimizar las fluctuaciones adaptando el rendimiento del oscilador de reloj a la aplicación.

Conceptos básicos sobre fluctuaciones

Las fluctuaciones de reloj son la desviación de un flanco de reloj de su posición ideal en el tiempo. Estas fluctuaciones afectan a la precisión de la temporización y a la exactitud de la transmisión de las señales de datos que la señal de reloj está marcando, lo que provoca una degradación de la relación señal/ruido (SNR) en los circuitos de decodificación/demodulación del receptor u otros CI del sistema. El resultado es una mayor tasa de error de bit (BER), un aumento de las retransmisiones y una reducción de la producción efectiva de datos.

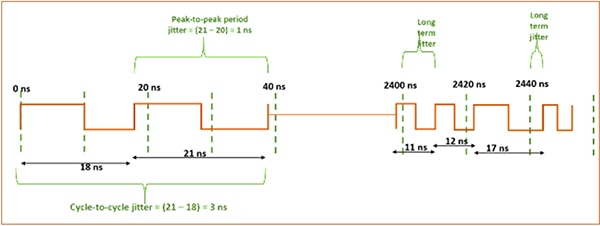

Dada su criticidad, las fluctuaciones del reloj se analizan ampliamente en sistemas que pasan una señal de una fuente transmisora a un receptor a través de cables, conectores o placas de circuitos. Dependiendo de la aplicación, puede caracterizarse de muchas formas, como ciclo a ciclo, periodo y fluctuaciones a largo plazo (Figura 1).

Figura 1: El término "fluctuación" engloba muchas variaciones de temporización, como la fluctuación ciclo a ciclo, la fluctuación de periodo y la fluctuación a largo plazo. (Fuente de la imagen: VLSI Universe)

Figura 1: El término "fluctuación" engloba muchas variaciones de temporización, como la fluctuación ciclo a ciclo, la fluctuación de periodo y la fluctuación a largo plazo. (Fuente de la imagen: VLSI Universe)

- Las fluctuaciones de ciclo a ciclo significan el cambio en el periodo de reloj a lo largo de dos ciclos consecutivos y no están relacionadas con la variación de la frecuencia en el tiempo.

- Las fluctuaciones de periodo son la desviación de cualquier periodo de reloj con respecto a su periodo medio. Es la diferencia entre los periodos de reloj ideal y real, y se puede especificar como fluctuaciones del periodo cuadrático medio (RMS) o fluctuaciones del periodo pico a pico.

- Las fluctuaciones a largo plazo son la desviación del flanco de reloj de su posición ideal durante un periodo de tiempo más largo. Es algo análogo a la deriva.

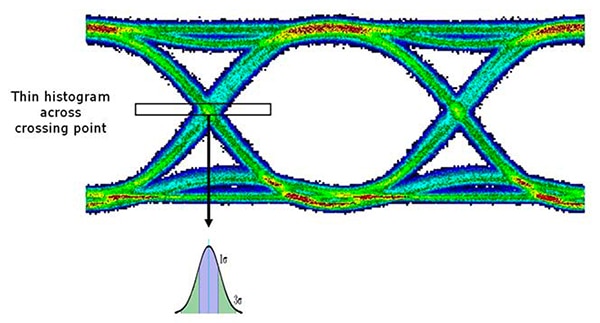

Las fluctuaciones pueden corromper la temporización empleada por otras subfunciones, componentes o sistemas utilizados para lograr una recuperación de datos de baja BER, o componentes de paso como elementos de memoria o procesadores en un sistema síncrono. En el diagrama ocular de la figura 2 se aprecia como un ensanchamiento del punto de cruce en la temporización de bits.

Figura 2: En un diagrama ocular, las fluctuaciones se ven como un ensanchamiento del punto crítico de cruce temporal en el flujo de datos. (Fuente de la imagen: Kevin K. Gifford/Univ. de Colorado)

Figura 2: En un diagrama ocular, las fluctuaciones se ven como un ensanchamiento del punto crítico de cruce temporal en el flujo de datos. (Fuente de la imagen: Kevin K. Gifford/Univ. de Colorado)

En los enlaces de datos en serie, los circuitos del extremo receptor deben intentar restablecer su propio reloj para una descodificación óptima del flujo de datos. Para ello, debe sincronizarse y bloquearse con el reloj de origen, a menudo mediante un bucle de fase cerrado (PLL). Las fluctuaciones afectan a la capacidad del sistema para hacer esto con precisión, comprometiendo su capacidad para recuperar los datos con una BER baja.

Obsérvese que las fluctuaciones pueden medirse tanto en el dominio temporal como en el frecuencial; ambos son perspectivas igualmente válidas del mismo fenómeno. El ruido de fase es una visión en el dominio de la frecuencia del espectro de ruido en torno a la señal del oscilador, mientras que las fluctuaciones son una medida en el dominio del tiempo de la precisión temporal del periodo del oscilador.

Las mediciones de fluctuaciones pueden expresarse de varias formas. Se suele citar utilizando unidades de tiempo como "fluctuaciones de 10 picosegundos" (ps). La fluctuación de fase cuadrática media cuadrática (RMS) es un parámetro en el dominio del tiempo que se deriva de la medición del ruido de fase (dominio de la frecuencia). A veces también se denomina fluctuaciones de fase, lo que puede resultar confuso, pero sigue siendo el parámetro de fluctuaciones en el dominio temporal.

A medida que las frecuencias de funcionamiento de los enlaces y sus relojes aumentan de unas decenas de MHz a cientos de MHz o más, las fluctuaciones permitidas en la fuente de reloj disminuyen a unos 100 fs o menos. Estas frecuencias se aplican a módulos ópticos, computación en nube, redes y Ethernet de alta velocidad, todas ellas son funciones y aplicaciones que requieren una frecuencia portadora de entre 100 y 212/215 MHz y velocidades de datos de hasta 400 gigabits por segundo (Gbps).

Gestionar el cristal

La forma más común de crear una señal de reloj estable, consistente y de frecuencia precisa es utilizar un oscilador de cristal de cuarzo. Un circuito oscilador asociado soporta el cristal. Existen muchas familias de circuitos de este tipo, cada una de ellas con distintas ventajas y desventajas. Los cristales se utilizan desde los años 30 para las comunicaciones inalámbricas en las bandas de radiofrecuencia de media frecuencia (300 kilohertz (kHz) a 3 MHz) y alta frecuencia (3 a 30 MHz).

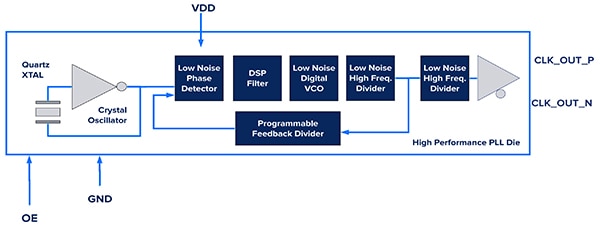

Un método muy utilizado para generar relojes de bajas fluctuaciones es utilizar una de las muchas variaciones de arquitecturas basadas en PLL. Por ejemplo, los dispositivos de las familias AX5 y AX7 ClearClock™ de Abracon se presentan en encapsulados de 5 × 3.2 milímetros (mm) y 5 × 7 mm, respectivamente, y utilizan una sofisticada tecnología PLL para obtener un rendimiento superior con bajas fluctuaciones (Figura 3).

Figura 3: Los osciladores de reloj AX5 y AX7 de Abracon utilizan uno de los muchos diseños basados en PLL, pero con sutiles mejoras para minimizar las fluctuaciones. (Fuente de la imagen: Abracon)

Figura 3: Los osciladores de reloj AX5 y AX7 de Abracon utilizan uno de los muchos diseños basados en PLL, pero con sutiles mejoras para minimizar las fluctuaciones. (Fuente de la imagen: Abracon)

Junto con la frecuencia de funcionamiento y el diseño del oscilador, el rendimiento en fluctuaciones se ve afectado por el tamaño físico del cristal de cuarzo en el núcleo del oscilador. A medida que se reduce el tamaño de este cristal, resulta más difícil ofrecer un rendimiento superior de fluctuaciones RMS.

Para soluciones de reloj en la banda de 100 a 200 MHz y en factores de forma más pequeños que los dispositivos AX5 y AX7 basados en PLL, se necesita una nueva arquitectura de oscilador. Estos requisitos de menor tamaño suelen asociarse a los transceptores y módulos ópticos de última generación. Hay cuatro formas establecidas de diseñar un oscilador de reloj en el rango de 100 a 200 MHz:

- Utilizar un oscilador de cuarzo con una pieza bruta de cuarzo de mesa invertida como elemento resonador.

- Utilizar un oscilador de cuarzo con una pieza bruta de cuarzo de tercer sobretono como elemento resonador.

- Utilizar un bucle oscilador basado en un blanco de cuarzo de sub-50 MHz, tercer sobretono/modo fundamental, o un oscilador con cristal controlado y temperatura compensada de sub-50 MHz acoplado con un CI PLL de modo entero o fraccionario.

- Utiliza un bucle oscilador basado en un resonador MEMS de menos de 50 MHz acoplado a un CI PLL de modo entero o fraccionario.

La opción 1 no ofrece el mejor rendimiento de fluctuaciones RMS ni es la solución más rentable. La opción 3 se complica y presenta deficiencias de rendimiento, mientras que el enfoque del resonador MEMS de la opción 4 no cumple el criterio principal de rendimiento de 200 fs de fluctuaciones RMS máximas. Por el contrario, la opción 2 utiliza una pieza bruta de cuarzo de tercer sobretono diseñada de forma óptima, teniendo en cuenta la geometría de los electrodos y la optimización del ángulo de corte. Esta combinación es óptima en términos de costo, rendimiento y tamaño.

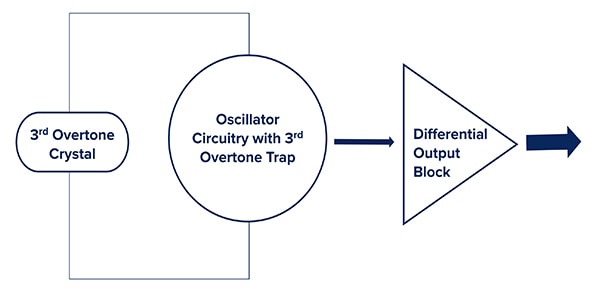

Utilizando este enfoque, Abracon desarrolló soluciones ClearClock de "tercer tono" (Figura 4). Estos dispositivos utilizan una arquitectura más silenciosa para ofrecer un rendimiento superior con fluctuaciones RMS ultrabajas y una eficiencia energética extrema en encapsulados en miniatura de tan solo 2.5 × 2.0 x 1.0 mm.

Figura 4: La solución ClearClock de "tercer tono" de Abracon utiliza una arquitectura más silenciosa para mejorar el rendimiento general y la eficiencia energética. (Fuente de la imagen: Abracon)

Figura 4: La solución ClearClock de "tercer tono" de Abracon utiliza una arquitectura más silenciosa para mejorar el rendimiento general y la eficiencia energética. (Fuente de la imagen: Abracon)

En este esquema, el cuidadoso diseño del cristal de tercer sobretono en blanco, junto con el filtrado y "atrapamiento" adecuados de la señal portadora deseada, garantizan un excelente rendimiento de fluctuaciones RMS en las frecuencias portadoras deseadas.

Esta arquitectura no utiliza un enfoque PLL típico, por lo que no hay conversión ascendente. Por consiguiente, no es necesaria la multiplicación fraccionaria o entera estándar del PLL, y la frecuencia de salida final tiene una correlación uno a uno con la frecuencia de resonancia del cristal de cuarzo de tercer armónico. La ausencia de multiplicación fraccionaria o entera simplifica el diseño y permite obtener fluctuaciones mínimas en el tamaño más pequeño posible.

Especificaciones y rendimiento en la realidad

Los osciladores de reloj son algo más que un cristal y su circuito analógico. Incluyen búfer para garantizar que la carga de salida del oscilador y sus variaciones a corto y largo plazo no afecten al rendimiento de la unidad. También admiten varios niveles de salida lógica digital diferencial para la compatibilidad de circuitos. Esta compatibilidad elimina la necesidad de un CI de transmisión de nivel lógico externo. Un CI de este tipo aumentaría el coste, la huella y las fluctuaciones.

Dado que los osciladores de reloj se utilizan en una gran variedad de aplicaciones con distintas tensiones de carril, deben ofrecerse con distintas tensiones de alimentación, como +1.8 voltios, +2.5 voltios o +3.3 voltios, así como con valores personalizados que suelen oscilar entre 2.25 y 3.63 voltios. También deben estar disponibles con diferentes opciones de formato de salida, como lógica positiva de bajo voltaje/pseudo acoplada a emisor(LVPECL) y señal diferencial de bajo voltaje (LVDS), así como otros formatos.

El estudio de dos familias de osciladores de reloj de cristal, el AK2A y el AK3A, demuestra lo que se puede conseguir mediante una sofisticada comprensión e integración de materiales, diseño, arquitectura y pruebas. Las dos familias son similares, y sus diferencias más destacadas son el tamaño y la frecuencia máxima.

La familia AK2A: Esta familia de osciladores de cristal se ofrece a frecuencias nominales de 100 a 200 MHz y está disponible con tensiones de funcionamiento de 2.5 voltios, 3.3 voltios y 2.25 a 3.63 voltios con lógica de salida diferencial LVPECL, LVDS y HSL.

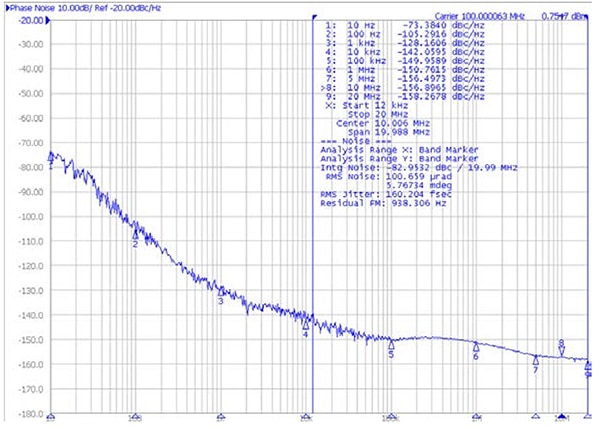

Todos los miembros de la familia tienen un rendimiento similar, incluidas unas fluctuaciones RMS bajas. Por ejemplo, el AK2ADDF1-100.000T es un dispositivo de 100.00 MHz y 3.3 voltios con salidas LVDS y una fluctuación RMS de 160.2 fs (Figura 5). Su estabilidad de frecuencia es excelente, mejor que ±15 partes por millón (ppm) a lo largo de la temperatura, y se presenta en un encapsulado de dispositivo de montaje superficial monolítico (SMD) de seis terminales que mide 2.5 × 2.0 × 1.0 mm.

Figura 5: Se muestran fluctuaciones de 160 fs para el AK2ADDF1-100.000T, un dispositivo de 3.3 voltios y 100 MHz con salidas LVDS. (Fuente de la imagen: Abracon)

Figura 5: Se muestran fluctuaciones de 160 fs para el AK2ADDF1-100.000T, un dispositivo de 3.3 voltios y 100 MHz con salidas LVDS. (Fuente de la imagen: Abracon)

Sin embargo, a medida que aumentan las frecuencias de reloj, las fluctuaciones deben disminuir para mantener el rendimiento del sistema. En el caso del AK2ADDF1-156.2500T, un oscilador LVDS de 156.25 MHz, las fluctuaciones RMS típicas descienden a 83 fs.

La familia AK3A: Los dispositivos de la familia AK3A son ligeramente más grandes que los de la familia AK2A, con una huella de 3.2 × 2.5 × 1.0 mm (Figura 6). Hay versiones disponibles y especificadas hasta 212.5 MHz, algo por encima del límite de 200 MHz de la familia AK2A.

Figura 6: Los osciladores de cristal AK3A (derecha) son ligeramente más largos y anchos que los de la serie AK2A (izquierda); hay versiones para frecuencias de hasta 212.5 MHz, frente a los 200 MHz del AK2A. (Fuente de la imagen: Abracon)

Figura 6: Los osciladores de cristal AK3A (derecha) son ligeramente más largos y anchos que los de la serie AK2A (izquierda); hay versiones para frecuencias de hasta 212.5 MHz, frente a los 200 MHz del AK2A. (Fuente de la imagen: Abracon)

Las especificaciones generales de este dispositivo AK3A son similares a las del miembro correspondiente de la familia AK2A. Un ejemplo es el AK3ADDF1-156.2500T3, un oscilador LVDS de 156,25 MHz que tiene una fluctuación RMS típica de 81 fs, ligeramente mejor que el miembro correspondiente de la familia AK2A.

Las fluctuaciones de ambas familias varían según la frecuencia de funcionamiento, el voltaje de funcionamiento, el tamaño del encapsulado y la elección de las salidas.

Consideraciones adicionales sobre el mundo real

No basta con tener un oscilador de reloj que cumpla las especificaciones solo el día que sale de fábrica. Como ocurre con todos los componentes, especialmente los analógicos y pasivos, estos osciladores están sujetos a desviaciones con el paso del tiempo debido al envejecimiento de los materiales que los componen y a las tensiones internas.

Esta realidad es especialmente difícil para los osciladores de reloj de alto rendimiento, ya que no hay formas cómodas o sencillas de corregir o compensar esta deriva añadiendo software o circuitos inteligentes. Sin embargo, hay algunas formas de mitigar los efectos de la deriva. Entre ellos se incluyen largos periodos de rodaje por parte del usuario final para acelerar el envejecimiento del oscilador, o el uso de un oscilador de temperatura estabilizada en un gabinete controlado por horno. El primero requiere mucho tiempo y supone un reto para la cadena de suministro, mientras que el segundo es grande, costoso y consume mucha energía.

Reconociendo que el envejecimiento es un parámetro crítico, la familia ClearClock de Abracon ofrece una precisión de frecuencia estricta e integral durante toda la vida útil del producto final, de 10 a 20 años. Abracon garantiza el cumplimiento de una estabilidad de frecuencia superior a ±50 ppm durante este periodo. Esto se consigue mediante una cuidadosa selección y fabricación del cristal de tercer armónico y acondicionándolo para que tenga una estabilidad de ±15 ppm entre -20 °C y +70 °C y de ±25 ppm entre -40 °C y +85 °C.

Como siempre, la ingeniería consiste en hacer concesiones. Las series AK2A y AK3A de Abracon proporcionan un rendimiento mejorado de fluctuaciones-ruido en comparación con sus series predecesoras (Gen I AK2 y AX3, respectivamente) mediante el uso de un oscilador ASIC de nueva generación (Gen II), garantizando así un rendimiento de fluctuaciones RMS ultrabajo.

Esta mejora se consigue a costa de un ligero aumento del consumo de energía. El consumo máximo de corriente aumenta de 50 miliamperios (mA) para Gen I a 60 mA para Gen II, aunque los dispositivos de bajo voltaje funcionan aproximadamente a la mitad de ese valor. Por lo tanto, los osciladores ClearClock de segunda generación proporcionan fluctuaciones RMS ultrabajas manteniendo un bajo consumo de energía.

Conclusión:

Los osciladores de temporización son el corazón de un enlace de datos o de una función de sincronización, y su precisión, fluctuación y estabilidad son parámetros críticos para lograr el rendimiento requerido a nivel de sistema, incluida una SNR alta y una BER baja. Se pueden conseguir frecuencias de reloj más altas con innovadoras selecciones de materiales y arquitecturas que cumplen las estrictas especificaciones de rendimiento exigidas por el sector y sus diversos estándares. Las series AK2A y AK3A de Abracon presentan fluctuaciones por debajo de 100 fs en el rango de 100 a 200 MHz en encapsulados SMD de unos pocos milímetros de lado.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.