Cree rápidamente relojes de baja fluctuación y alta frecuencia con un módulo de bucle de conversión

Colaboración de Editores de DigiKey de América del Norte

2021-08-04

Los diseñadores de sistemas de instrumentación y medición requieren señales de baja fluctuación y sin espurias para proporcionar las relaciones señal-ruido (SNR) o las magnitudes del vector de error (EVM) necesarias para satisfacer los requisitos cada vez más exigentes de los clientes. Al mismo tiempo, también se enfrentan a una importante presión para reducir el espacio de la placa, así como el costo del diseño y la complejidad. Esto último es fundamental para acortar el tiempo de desarrollo y cumplir con los plazos de comercialización, cada vez más reducidos.

Para hacer frente a los numerosos retos que plantean las aplicaciones, los ingenieros tienen que hacer la transición de sus soluciones de relojería de instrumentación y medición desde diseños tradicionalmente discretos hechos a medida a soluciones más integradas. Un paso importante en este sentido es utilizar un bucle de bloqueo de fase (PLL) traslacional integrado. Esto permite la conversión ascendente de la frecuencia de una señal de oscilador controlado por tensión (VCO) tradicional, manteniendo sustancialmente la fluctuación y el ruido de fase de un oscilador local (LO) externo fijo.

Este artículo analiza el papel de los bucles de traslación para conseguir el ruido de fase integrado más bajo del sector. A modo de ejemplo, presenta el sistema en paquete de bucle de traslación (TL SiP) ADF4401A de Analog Devices y muestra cómo aborda los requisitos de rendimiento a través de una señal de salida con capacidad de fluctuación integrada de banda ancha por debajo de 10 femtosegundos (fs) rms y un aislamiento mejorado para atenuar los componentes espurios, al tiempo que satisface las necesidades de integración, costo, complejidad y tiempo de comercialización de los diseñadores.

Operaciones tradicionales de PLL frente a las de bucle de traslación

El objetivo principal de un bucle de traslación es generar una señal de salida bloqueada a una señal de referencia de entrada con un ruido de fase en banda significativamente reducido en comparación con los PLL tradicionales.

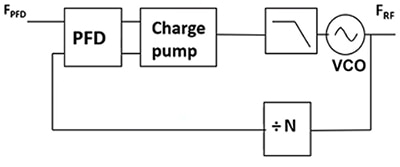

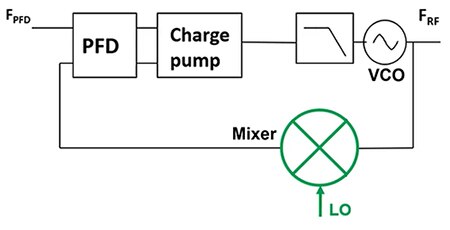

Un PLL estándar consiste en un sistema de retroalimentación que contiene un detector de frecuencia de fase (PFD), una bomba de carga, un filtro de paso bajo (LPF), un VCO y un divisor de frecuencia de retroalimentación N (Figura 1).

Figura 1: El PLL estándar se bloquea en una referencia de frecuencia inferior (FPFD) y genera una frecuencia de salida (FRF). (Fuente de la imagen: Bonnie Baker)

Figura 1: El PLL estándar se bloquea en una referencia de frecuencia inferior (FPFD) y genera una frecuencia de salida (FRF). (Fuente de la imagen: Bonnie Baker)

El PFD compara la fase de la referencia de entrada y la fase de la señal de retroalimentación y genera una serie de pulsos proporcionales al error de fase entre ellos. La bomba de carga recibe los pulsos del PFD y los convierte en pulsos de fuente o sumidero de corriente que, a su vez, sintonizarán el VCO hacia arriba o hacia abajo en la frecuencia. El LPF elimina toda la energía de alta frecuencia de los pulsos y los convierte en una tensión que el VCO puede utilizar. La señal de salida del VCO se devuelve al bloque PFD a través del divisor N para completar el bucle.

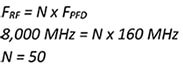

La función de transferencia de frecuencia de la figura 1 se calcula mediante la ecuación 1:

![]() Ecuación 1

Ecuación 1

Donde FRF es la frecuencia de salida

N es la relación del divisor de retroalimentación (puede ser entero o fraccionario)

FPFD es la frecuencia PFD

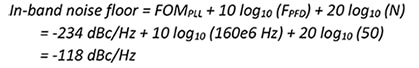

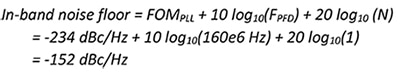

El suelo de ruido en banda de la figura 1 se calcula mediante la ecuación 2:

![]() Ecuación 2

Ecuación 2

Donde FOMPLL es la figura de mérito del ruido de fase en banda del PLL (FOM)

Consideremos un ejemplo con un piso de ruido de fase en banda FOM de -234 decibelios por Hertz (dB/Hz); una frecuencia PFD (FPFD) de 160 megahercios (MHz), y una frecuencia de salida (FRF) de 8 gigahercios (GHz).

Para este sistema, se utiliza la ecuación 1 para calcular el valor de N:

La ecuación 2 se utiliza para calcular el ruido de fondo en banda:

En el cálculo anterior, el divisor N contribuye en gran medida a la base de ruido global dentro de la banda, con 20 log10 (50), lo que equivale a 34 dB. Un valor N más pequeño disminuiría el piso de ruido en la banda; sin embargo, también disminuiría la frecuencia de salida. Entonces, ¿cómo generamos una frecuencia de salida alta y mantenemos una ganancia de bucle (N) más baja?

Figura 2: Para un PLL estándar en este ejemplo, el ruido del divisor de realimentación (20 log10(N)) tiene un ruido en banda 34 dB mayor comparado con el gráfico amarillo inferior donde N = 1. (Fuente de la imagen: Bonnie Baker)

Figura 2: Para un PLL estándar en este ejemplo, el ruido del divisor de realimentación (20 log10(N)) tiene un ruido en banda 34 dB mayor comparado con el gráfico amarillo inferior donde N = 1. (Fuente de la imagen: Bonnie Baker)

La solución a este problema es sustituir el divisor N por una etapa de mezcla de conversión descendente (figura 3).

Figura 3: Un bucle de traslación utiliza un mezclador para convertir la frecuencia del VCO a la frecuencia del PFD en lugar de utilizar un divisor de retroalimentación tradicional. (Fuente de la imagen: Bonnie Baker)

Figura 3: Un bucle de traslación utiliza un mezclador para convertir la frecuencia del VCO a la frecuencia del PFD en lugar de utilizar un divisor de retroalimentación tradicional. (Fuente de la imagen: Bonnie Baker)

En la figura 3, el mezclador sustituye al divisor de realimentación N, lo que da lugar a una ganancia de bucle igual a 1 (N=1). Esta operación disminuirá en gran medida la contribución del bucle de retroalimentación al piso de ruido en la banda. Para el cálculo del ruido en la banda, el valor de N es ahora igual a 1. Utilizando la ecuación 2, el suelo de ruido en banda para el sistema modificado es el siguiente:

El nuevo ruido en banda muestra una mejora de 34 dBc/Hz.

En la Figura 3, el mezclador depende de un LO de muy bajo ruido, llamado Offset LO. FLO ±FRF debe ser igual a FPFD para lograr el bloqueo.

Con la arquitectura de bucle de traslación, el ruido de fase del LO de compensación es muy importante para conseguir el mejor rendimiento en la salida de RF. Por esta razón, los ingenieros suelen diseñar un LO de compensación basado en ondas acústicas de superficie (SAW) controladas por tensión, u osciladores (VCSO), o generadores de peine, u osciladores de resonador dieléctrico (DRO). NOTA: Para obtener ayuda con el diseño de un LO de compensación, póngase en contacto con Analog Devices.

Retos del bucle de traslación

Tradicionalmente, el diseño de un bucle de traslación de bajo ruido implica la implementación de numerosos bloques de circuitos, lo que da lugar a un diseño complejo, normalmente de gran tamaño, y con una flexibilidad limitada. Además, todo el circuito debe ser validado y caracterizado para el funcionamiento del objetivo. Por ejemplo, una de las principales preocupaciones de diseño es la fuga de LO (aislamiento de LO a RF) a la señal de salida de RF. Se trata de un reto importante para los ingenieros. Con los diseños tradicionales, los ingenieros suelen proceder a múltiples iteraciones de diseño para lograr un rendimiento optimizado y un aislamiento adecuado.

La figura 3 muestra cómo el ADF4401A integra los principales bloques de circuitos para proporcionar una solución totalmente caracterizada y elimina las áreas tradicionalmente difíciles relacionadas con el rendimiento y el aislamiento en los diseños de bucles de traslación. Esta solución programable permite a los ingenieros conseguir un rendimiento optimizado a la primera y reducir el tiempo de comercialización.

Evaluación del ADF4401A

El ADF4401A está diseñado para ayudar a los ingenieros a reducir el tiempo de comercialización de la instrumentación de alto rendimiento, utilizando una solución de generación de frecuencia con un ancho de banda de RF de 62.5 MHz a 8 GHz. Al utilizar un mezclador de conversión descendente, el ADF4401A tiene un ruido en banda muy bajo con una fluctuación de banda ancha de ~9 femtosegundos (fs) integrada de 100 Hz a 100 MHz. Las técnicas de diseño y disposición del ADF4401A permiten un rango dinámico típico sin espurias de 90 dBc. El tamaño del paquete de 18 x 18 x 2.018 milímetros (mm) reduce considerablemente el espacio de la placa en comparación con un diseño discreto tradicional.

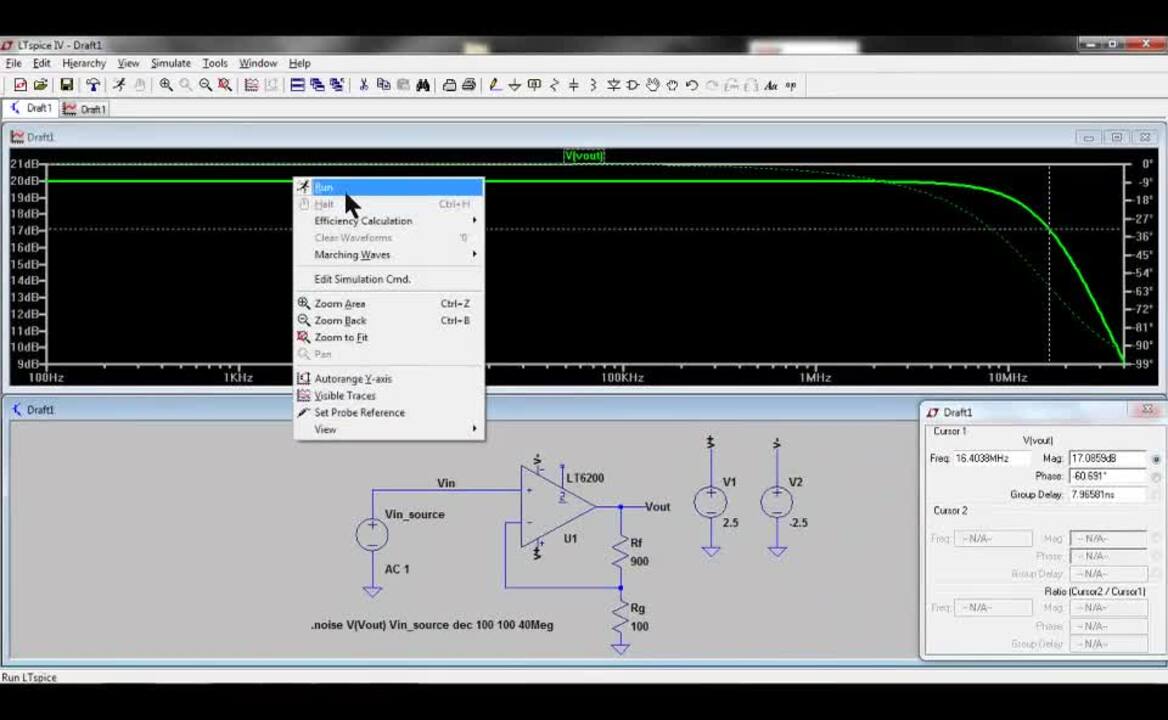

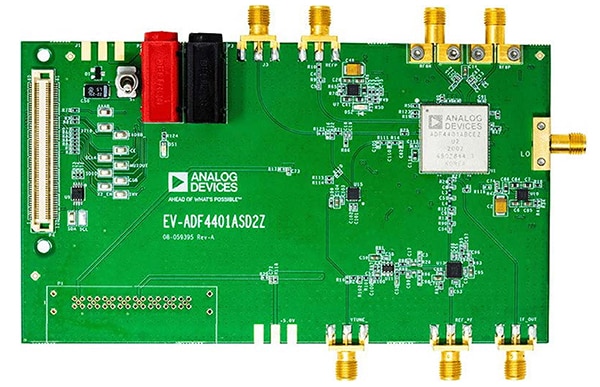

Para evaluar el rendimiento del dispositivo, los diseñadores pueden utilizar la placa de evaluación EV-ADF4401ASD2Z (Figura 4). La placa incluye un bucle de traslación completo, que incluye un PFD externo (HMC3716), un filtro activo (LT6200) y un multiplexor (ADG1609).

Figura 4: La placa de evaluación EV-ADF4401ASD2Z para el módulo de bucle de traslación ADF4401A incluye un PFD externo, una interfaz USB y reguladores de tensión. (Fuente de la imagen: Analog Devices).

Figura 4: La placa de evaluación EV-ADF4401ASD2Z para el módulo de bucle de traslación ADF4401A incluye un PFD externo, una interfaz USB y reguladores de tensión. (Fuente de la imagen: Analog Devices).

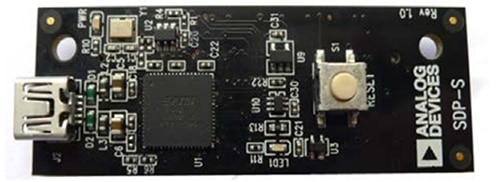

El EV-ADF4401ASD2Z incluye el SiP ADF4401A TL con VCO integrado, un filtro de bucle (5 MHz), un PFD, una interfaz USB y reguladores de tensión. Además, el EV-ADF4401ASD2Z requiere la tarjeta controladora (serie) de la plataforma de demostración del sistema (SDP-S) EVAL-SDP-CS1Z (Figura 5). La placa proporciona una conexión USB desde un PC al EV-ADF4401ASD2Z para poder programarlo. La placa controladora no se suministra en el kit EV-ADF4401ASD2Z.

Figura 5: La tarjeta controladora EVAL-SDP-CS1Z (o SDP-S) es necesaria para proporcionar una conexión USB desde el EV-ADF4401ASD2Z a un PC para su programación. (Fuente de la imagen: Analog Devices).

Figura 5: La tarjeta controladora EVAL-SDP-CS1Z (o SDP-S) es necesaria para proporcionar una conexión USB desde el EV-ADF4401ASD2Z a un PC para su programación. (Fuente de la imagen: Analog Devices).

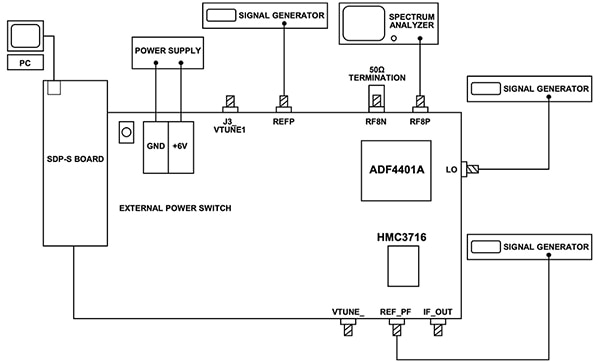

La Figura 6 muestra las conexiones físicas del sistema EV-ADF4401ASD2Z. El software de análisis | control | evaluación (ACE) asociado controla las funciones de la TL SiP. La alimentación proviene de una fuente de alimentación de 6 voltios aplicada externamente.

Figura 6: Un diagrama de configuración del EV-ADF4401ASD2Z muestra el equipo y las conexiones necesarias para evaluar el ADF4401A, incluyendo la tarjeta de control SDP-S, el PC, la fuente de alimentación, los generadores de señales y el analizador de espectro. (Fuente de la imagen: Analog Devices)

Figura 6: Un diagrama de configuración del EV-ADF4401ASD2Z muestra el equipo y las conexiones necesarias para evaluar el ADF4401A, incluyendo la tarjeta de control SDP-S, el PC, la fuente de alimentación, los generadores de señales y el analizador de espectro. (Fuente de la imagen: Analog Devices)

El equipo sugerido para utilizar con esta placa de evaluación incluye un PC con Windows, un analizador de espectro o un analizador de fuentes de señal, y tres generadores de señal.

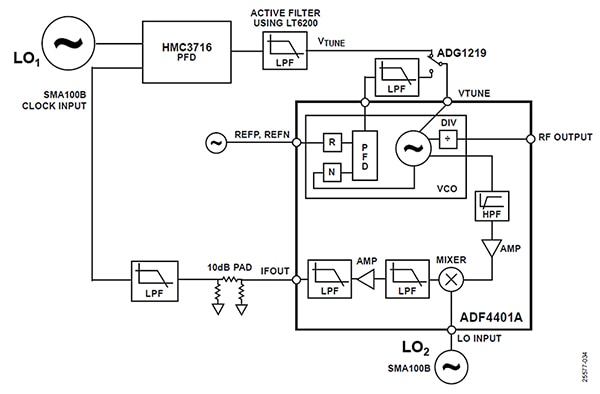

El diagrama de bloques del EV-ADF4401ASD2Z muestra el módulo ADF4401A, junto con el PFD HMC3716 de Analog Devices, el op-amp LT6200 y el interruptor SPDT ADG1219 (Figura 7).

Figura 7: El diagrama de bloques de la placa de evaluación EV-ADF4401ASD2Z muestra los componentes clave que soportan el bucle de traslación AD4401A. (Fuente de la imagen: Analog Devices)

Figura 7: El diagrama de bloques de la placa de evaluación EV-ADF4401ASD2Z muestra los componentes clave que soportan el bucle de traslación AD4401A. (Fuente de la imagen: Analog Devices)

Es fundamental utilizar un PFD que pueda funcionar a altas frecuencias, ya que así se minimiza la necesidad de utilizar divisores, que pueden degradar la respuesta de ruido en la banda. La capacidad de frecuencia de comparación de fase de 1.3 GHz del HMC3716 de Analog Devices lo hace ideal para su uso en el rango de FI del ADF4401A. La capacidad de un circuito de este tipo para comparar tanto la frecuencia como la fase elimina la necesidad de circuitos adicionales para dirigir la frecuencia a la frecuencia de salida prevista. El HMC3716 se convierte en el PFD externo para completar el bucle de compensación. El rango de funcionamiento de alta frecuencia y el ruido de fase mínimo del HMC3716 permiten diseñar filtros de bucle de gran ancho de banda.

En la Figura 7, el op-amp LT6200 con una configuración LPF atenúa los espolones de alta frecuencia, mientras que el interruptor ADG1219 completa el bucle de traslación del sistema.

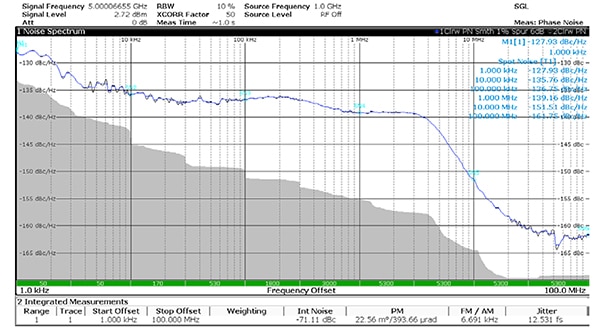

El dispositivo de evaluación EV-ADF4401ASD2Z crea gráficos de ruido en banda y mediciones de fluctuación como se muestra en la Figura 8.

Figura 8: Ruido de fase de banda lateral única a la salida de 5 GHz, con una referencia externa HMC3716 de 500 MHz y un LO externo a 4.5 GHz. (Fuente de la imagen: Analog Devices)

Figura 8: Ruido de fase de banda lateral única a la salida de 5 GHz, con una referencia externa HMC3716 de 500 MHz y un LO externo a 4.5 GHz. (Fuente de la imagen: Analog Devices)

En la Figura 8, la entrada de LO2 y HMC3716 es un generador de señales de RF y microondas SMA100B. El ruido en banda del LO2 de la placa de evaluación es de aproximadamente -135 dBc/Hz, lo que es evidente a bajas compensaciones hasta 300 kHz. El LO2, el módulo ADF4401A, el HMC3716 PFD y el filtro de bucle contribuyen a un ruido en banda de unos -140 dBc/Hz. El ruido de fase interno aparece entre 5 MHz y 50 MHz, y el piso de ruido de fase del aparato es de aproximadamente -160 dBc/Hz. Todo ello da unu fluctuación rms de 12.53 fs en total.

Conclusión:

Los sistemas de instrumentación de alta velocidad requieren relojes de muy baja fluctuación para garantizar que los datos de salida no se vean comprometidos. El reto para los ingenieros es encontrar dispositivos adecuados que puedan construir el sistema de reloj de alta velocidad a gigahercios. El bucle de traslación ADF4401A simplifica en gran medida la selección de dispositivos para construir el sistema de reloj, proporcionando un módulo compacto que garantiza una baja fluctuación a frecuencias más altas, al tiempo que reduce el espacio de la placa, el costo y el tiempo de comercialización.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.