Elija el ADC correcto para minimizar el parpadeo de la pantalla

Colaboración de Editores de DigiKey de América del Norte

2018-02-22

Los diseñadores necesitan minimizar el parpadeo en los números de pantalla, en especial para aplicaciones médicas y de instrumentación, donde los usuarios esperan una lectura estable y sin parpadeos. Como la fuente principal del parpadeo de la pantalla es el ruido del convertidor de analógico a digital (ADC), los diseñadores deben elegir este componente con cuidado.

Un diseño de excesiva complejidad mediante la selección de demasiados bits libres de ruido de ADC delta-sigma aumentará innecesariamente el costo y la potencia de los componentes. Por otro lado, un diseño demasiado simple con muy pocos bits libres de ruido creará un parpadeo de pantalla inaceptable.

Este artículo explica brevemente cómo utilizar la teoría del factor de cresta para determinar el convertidor apropiado. A través de un ejemplo y de una fórmula, se dará una estimación precisa de los bits de número disponibles para lograr un nivel preestablecido de parpadeo.

Ruido de convertidor aleatorio

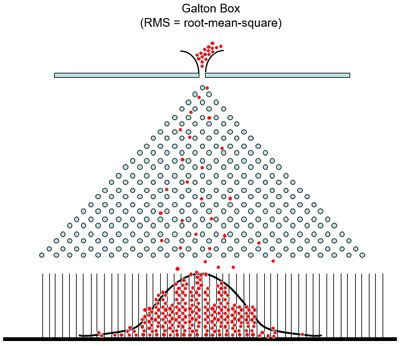

En la naturaleza, siempre se percibe algún tipo de ruido. Un roble tiene millones de hojas que por lo general son parecidas, pero tienen diferentes detalles. Uno puede describir las variaciones del patrón de las hojas como ruido. Debido al ruido, cada medición de la cantidad física es incierta, pero existe un patrón general esperado. Una caja de Galton ilustra este fenómeno (Figura 1).

Figura 1: Se dejan caer varias bolas en una caja de Galton individualmente para crear una distribución normal o gaussiana en el fondo. (Fuente de la imagen: DigiKey)

Una bola que cae en la parte superior de la caja de Galton tiene una probabilidad del 50% de ir hacia la derecha o hacia la izquierda. Estas estadísticas se interpretan cuando varias bolas caen en el lugar de descanso final en el fondo de la caja. Es imposible determinar el lugar de descanso de una bola específica; sin embargo, con el tiempo, varias bolas crean una notable distribución normal.

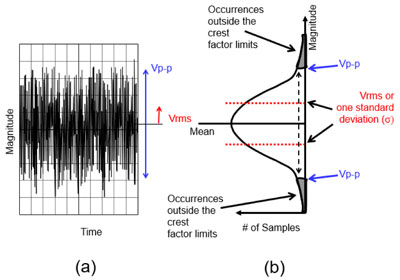

El ADC también crea una cierta incertidumbre al producir la muestra digital de salida. Esta incertidumbre refleja el ruido de silicio interno del convertidor. Si bien el ruido parece un evento totalmente aleatorio, con el tiempo, el patrón de distribución normal proporciona una descripción (Figura 2).

Figura 2: La salida de un ADC (a) con un voltaje de entrada único, con el tiempo, muestra el ruido que limita la distribución normal o gaussiana (b). (Fuente de la imagen: DigiKey)

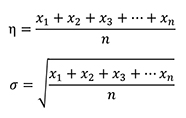

Cuando un proveedor define el valor cuadrático medio (RMS) o la desviación estándar (s) y la calidad pico a pico (pk-pk) de un convertidor, en realidad, se refiere al ruido. Estadísticamente, el ruido del código de salida del ADC se puede describir en términos de desviación promedio (h), valor cuadrático medio (RMS) o desviación estándar (s) y pico a pico (pk-pk). La ecuación 1 describe h y la ecuación 2 describe s.

Donde x1, x2, x3, xn son muestras de ADC en voltios o bits, y n es el número total de muestras de ADC.

Las hojas de datos del convertidor tienen dos formas de describir la cantidad de ruido de salida aleatorio con un solo valor. El primer método usa el RMS o la desviación estándar de una distribución ruidosa de datos. El segundo método describe el ruido de un convertidor con un valor pk-pk.

Control del ruido mediante un factor de cresta

En teoría, uno tendría que esperar una cantidad infinita de tiempo para determinar si el sistema diseñado permanecerá dentro de un conjunto de límites de ruido pico a pico. En la práctica, se requiere un enfoque más razonable.

Dado que el ruido sigue un patrón de distribución gaussiana, los diseñadores pueden usar un modelo estadístico para predecir el ruido pico a pico con gran certeza. Esta técnica de predecir los niveles máximos de ruido es relativamente simple de calcular mediante un factor de cresta. El factor de cresta para las ocurrencias de ruido es una estimación estadística que determina la probabilidad de que la ocurrencia de un evento ruidoso permanezca dentro de un límite definido.

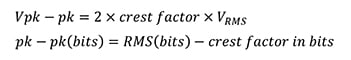

La técnica de predecir la fluctuación permitida en la visualización de datos es relativamente simple. Después de elegir un factor de cresta, que se basa en el porcentaje de eventos de ruido que permanecerán dentro de los límites definidos, multiplique el valor de dos desviaciones estándar por el factor de cresta seleccionado (Ecuaciones 3 y 4).

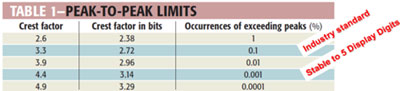

Esta técnica determina el porcentaje de resultados de datos de salida que irán más allá de los dígitos de la pantalla y estarán fuera de la vista. El factor de cresta estándar industrial es 3.3, que es apropiado para una pantalla de tres dígitos. Para mantener una pantalla de cinco dígitos sin parpadeos, es apropiado un valor de factor de cresta de 4.4 (Figura 3).

Figura 3. Para mantener una pantalla de cinco dígitos sin parpadeos, es apropiado un factor de cresta de 4.4. (Fuente de la imagen: DigiKey)

En la Figura 3, el ruido de voltaje pico a pico es igual al factor de cresta 2 (RMS) de ruido de voltaje de salida equivalente. Los bits de ruido pico a pico equivalen al ruido en bits (RMS): factor de cresta, en bits. A partir del factor de cresta seleccionado, la Figura 3 define la probabilidad de una ocurrencia que exceda los límites pico a pico definidos.

Derivación de la solución adecuada de ADC

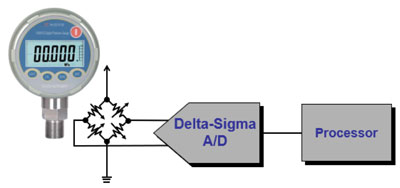

En entornos de aplicaciones médicas o de instrumentación, los usuarios esperan pantallas numéricas estables y sin parpadeos. Como el principal impulsor del parpadeo es el ruido, los diseñadores deben elegir con cuidado el sistema de detección de ADC. Un ejemplo de indicador de presión de pantalla de cinco dígitos utiliza un sensor de presión y un ADC delta-sigma para detectar la presión bruta. El desafío es elegir el ADC óptimo para esta aplicación (Figura 4).

Figura 4: La instrumentación Front End para un manómetro incluye un sensor de presión, un ADC delta-sigma y un procesador o microcontrolador. (Fuente de la imagen: DigiKey y Huaxin Instrument)

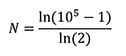

La cantidad de bits que pueden entrar en una pantalla de 5 dígitos es igual a 99,999, o 105 – 1. La ecuación 5 calcula la resolución adecuada (N) de un ADC para este sistema.

Donde N = la resolución del ADC

De acuerdo con la Ecuación 5, la resolución del ADC delta-sigma correcta para una pantalla de 5 bits es de 16,6 bits. En otras palabras, la resolución sin ruido del convertidor debe ser igual o superior a 16,6.

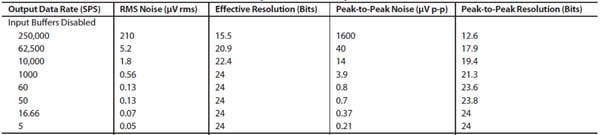

Las hojas de datos de un convertidor delta-sigma, como el de AD7175-2BRUZ-RL7 de Analog Devices, tienen especificaciones de ruido que permiten al diseñador determinar la aptitud del convertidor para una aplicación específica. La hoja de datos de AD7175-2 especifica varias condiciones. En general, las especificaciones disponibles para cada condición son el ruido RMS, la resolución efectiva, el ruido pico a pico y la resolución pico a pico (Figura 5).

Figura 5: El ruido RMS y la resolución pico a pico de AD7175-2 frente a la velocidad de salida de datos con el filtro Sinc3. (Fuente de la imagen: Analog Devices)

Los únicos valores que son muy útiles en la Figura 5 son el ruido RMS y la resolución efectiva. El ruido pico a pico y la resolución pico a pico en general representan valores de ruido con un factor de cresta de 3,3.

Si se aplica el factor de cresta en bits de 3,14 de la Figura 3 a la Ecuación 4, se obtiene:

pk-pk (bits) = 20,9 bits-3.14 bits

pk-pk (bits) = 17,76 bits

En la tabla de la Figura 5, la velocidad máxima de salida de datos de ADC7175-2 para esta aplicación es de 62.500 muestras por segundo (SPS). Una resolución más alta significa velocidades de salida de datos más bajas, por lo que la única velocidad de datos que no producirá una pantalla de 5 dígitos es de 250.000 SPS.

Conclusión

Para la estabilidad en la pantalla médica o de instrumentación, los diseñadores deben minimizar el parpadeo de la pantalla. La principal fuente de ruido de parpadeo de la pantalla es el ADC interno. Este artículo presenta el uso adecuado de la teoría del factor de cresta para determinar el convertidor apropiado y aplica esta teoría al ADC AD7175-2BRUZ-RL7 de Analog Devices.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.