Microprocesadores con IA visual de gama media para aplicaciones periféricas

Colaboración de Editores de DigiKey de América del Norte

2025-07-17

Las aplicaciones de IA en el borde (Edge AI) utilizan algoritmos de visión artificial para detectar personas, objetos o anomalías, como defectos, en tiempo real. El procesamiento de imágenes y videos en el borde suele requerir un microprocesador (MPU) de IA visual que pueda interactuar con cámaras, ejecutar modelos de IA y, a menudo, incluye un acelerador de IA específico.

La integración de las capacidades de IA visual en un solo dispositivo reduce el costo y el volumen que supone el uso de componentes separados, lo que hace que las MPU con IA visual de última generación sean ideales para aplicaciones integradas compactas.

La MPU RZ/V2N (Figura 1) de Renesas Electronics Corporation es una MPU de IA visual que se caracteriza por su bajo consumo energético, alto rendimiento de inferencia de IA, cuatro núcleos de CPU Arm® Cortex-® A55 (1.8 GHz), un Arm Cortex-M33 (200 MHz) y dos entradas de cámara a través de conexión MIPI.

Figura 1: La MPU RZ/V2N de Renesas ofrece a los diseñadores nuevas opciones para incluir IA visual en aplicaciones periféricas. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 1: La MPU RZ/V2N de Renesas ofrece a los diseñadores nuevas opciones para incluir IA visual en aplicaciones periféricas. (Fuente de la imagen: Renesas Electronics Corporation)

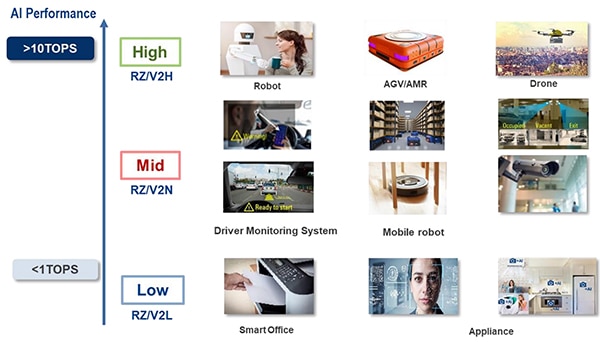

Este MPU de Renesas es una solución rentable para aplicaciones periféricas que requieren capacidades de IA moderadas a altas a un precio asequible. Forma parte de la serie RZ/V de la empresa, cuyo objetivo es ofrecer una amplia gama de escalabilidad, desde oficinas inteligentes hasta drones (Figura 2).

Figura 2: Posicionado como una oferta de gama media en la línea RZ/V, el RZ/V2N permite aplicaciones tales como robots móviles para uso doméstico y sistemas de supervisión del conductor. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 2: Posicionado como una oferta de gama media en la línea RZ/V, el RZ/V2N permite aplicaciones tales como robots móviles para uso doméstico y sistemas de supervisión del conductor. (Fuente de la imagen: Renesas Electronics Corporation)

Requisitos de un microprocesador de IA visual

Las aplicaciones de IA en el borde suelen ejecutarse en dispositivos integrados, que pueden funcionar con baterías o con reservas de energía muy bajas. Como resultado, las MPU de visión deben ofrecer altas capacidades de inferencia y, al mismo tiempo, consumir menos energía que los dispositivos informáticos tradicionales de alto rendimiento.

La MPU ideal de IA visual equilibra rendimiento, eficiencia energética, integración, facilidad de desarrollo y seguridad. A continuación, se ofrece una descripción general de algunas de las características clave a tener en cuenta a la hora de seleccionar una MPU:

- Rendimiento de inferencia: El RZ/V2N ofrece hasta 15 TOPS gracias a su acelerador DRP-AI3 integrado, lo que lo hace adecuado para aplicaciones de gama media, como cámaras inteligentes, inspección industrial y robótica periférica. Mientras que algunos sistemas de alto rendimiento, como los robots colaborativos y los drones autónomos, pueden requerir entre 80 y 100 TOPS, muchas aplicaciones de IA en el borde funcionan bien con entre 1 y 15 TOPS, dependiendo de su complejidad. TOPS por vatio (TOPS/W) define la eficiencia del producto, que es una medida de cuántas operaciones puede realizar por segundo por vatio.

Aunque TOPS ofrece una indicación básica del rendimiento, la velocidad de inferencia real puede mejorarse significativamente con la incorporación de un acelerador de IA dedicado, que descarga las cargas de trabajo de IA visual que dependen de cálculos intensivos de matrices y tensores. Esto permite que los sistemas funcionen más rápido y de manera más eficiente, con menos ciclos de reloj y un menor consumo de energía.

- Funcionamiento con bajo consumo: Muchos dispositivos periféricos funcionan con baterías o dentro de límites térmicos estrictos. Las MPU de visión diseñadas para IA en el borde suelen incluir escalado dinámico de voltaje y frecuencia (DVFS), que ajusta el consumo de energía en función de las demandas de la carga de trabajo. En combinación con técnicas como la poda de redes neuronales, que comprime el tamaño del modelo y reduce los cálculos innecesarios, DVFS ayuda a conseguir una mayor relación TOPS/W, lo que mejora tanto el tiempo de ejecución como la duración de la batería. El acelerador DRP-AI3 ayuda a evitar la necesidad de GPU que consumen mucha energía, lo que contribuye a obtener un mayor TOPS/W en el borde.

- Procesamiento de imágenes en chip: Los microprocesadores de visión con procesadores de señal de imagen (ISP) integrados opcionales pueden realizar tareas rutinarias de limpieza de imágenes, como la corrección del nivel de negro, la corrección del color, el recorte y la corrección del sombreado. En aplicaciones de seguridad o vigilancia, el ISP también puede prefiltrar tramas. Por ejemplo, en una transmisión de video continua, el sistema puede descartar fotogramas estáticos y enviar solo fotogramas con movimiento o actividad (por ejemplo, detección de intrusos) al procesador de IA, lo que reduce las inferencias innecesarias y ahorra energía.

- Memoria integrada en el chip: La memoria también es un factor importante para el rendimiento y la eficiencia. Mantener los datos locales evita la latencia y el costo energético que supone acceder a la memoria externa, lo cual puede ser significativo durante la inferencia de IA en tiempo real. Con 1.5 MB de SRAM integrada y compatibilidad con memoria LPDDR4X, el RZ/V2N equilibra la velocidad de procesamiento interno con opciones de memoria ampliables.

- Aceleración de la implementación de la IA: Los kits de herramientas de IA y las placas de evaluación que incluyen aplicaciones e interfaces preprogramadas pueden ayudar a los desarrolladores a crear rápidamente prototipos e implementar aplicaciones de IA visual. Además, la MPU debería ser compatible con los formatos estándar de modelos de IA. El RZ/V2N es compatible con formatos de modelos estándar, como ONNX y TensorFlow Lite.

- Seguridad: En entornos de borde, cada sensor o punto final puede representar un vector de ataque potencial. Por lo tanto, es importante que las MPU de visión puedan admitir funciones de seguridad integradas, como el arranque seguro y las rutas de datos cifradas. El RZ/V2N incluye funciones de arranque seguro y cifrado a nivel de hardware y aprovecha Arm TrustZone para aislar las operaciones seguras, lo que ayuda a proteger tanto la integridad del modelo como los datos de entrada confidenciales.

Características del MPU RZ/V2N que facilitan el diseño con IA

El acelerador de IA patentado por Renesas, el DRP-AI3 (procesador reconfigurable dinámicamente), tiene una potencia nominal de 10 TOPS/W, pero puede mejorarse hasta 15 TOPS/W con una poda avanzada, que comprime el tamaño de los modelos que el sistema debe procesar. Esto puede eliminar la necesidad de una unidad de procesamiento gráfico (GPU) o una matriz de puertas programables en campo (FPGA) independientes.

El RZ/V2N mide solo 15 mm², lo que lo convierte en una buena opción para dispositivos compactos. La combinación de una CPU de cuatro núcleos, un acelerador de IA dedicado y la compatibilidad con entradas de doble cámara en un solo dispositivo abre nuevas oportunidades para que los diseñadores integren la IA visual en aplicaciones como cámaras inteligentes, dispositivos de seguridad, robots e incluso electrodomésticos.

La MPU funciona con bajo consumo, lo que reduce la cantidad de calor generado, eliminando la necesidad de sistemas de refrigeración y ventiladores adicionales, y reduciendo así el tamaño y el costo de los sistemas integrados. Con capacidad para alojar dos cámaras, permite a las aplicaciones capturar imágenes desde dos ángulos y mejorar el reconocimiento espacial. Un sistema puede realizar múltiples operaciones, como contar simultáneamente los coches en un aparcamiento y reconocer las matrículas.

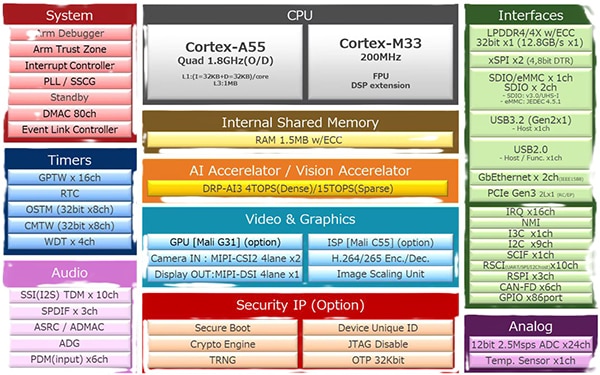

La arquitectura de la MPU RZ/V2N

La MPU RZ/V2N ofrece una amplia gama de características y funciones diseñadas para crear aplicaciones de IA de gama media que requieren una IA de alto rendimiento a un precio asequible (Figura 3).

Figura 3: Diagrama de la arquitectura RZ/V2N. (Fuente: Renesas Electronics Corp.)

Figura 3: Diagrama de la arquitectura RZ/V2N. (Fuente: Renesas Electronics Corp.)

Algunas de sus muchas características incluyen:

- Unidad central de procesamiento (CPU): La arquitectura híbrida cuenta con el Cortex-A55 Quad a 1.8 GHz, una CPU de alto rendimiento, y el Cortex-M33 a 200 MHz, un núcleo de bajo consumo diseñado para el control en tiempo real y tareas relacionadas con la seguridad.

- Memoria interna compartida: 1.5 MB de RAM para memoria integrada en el chip con código de corrección de errores (ECC), lo que ayuda a garantizar la integridad de los datos. Los algoritmos ECC detectan y corrigen errores en los datos, tanto en el almacenamiento como en la transmisión. La memoria integrada de 1.5 MB permite que los algoritmos de IA se ejecuten rápidamente, y el RZ/V2N también cuenta con una interfaz para memoria DDR externa que se puede añadir si se necesita más memoria.

- Acelerador de IA: El motor de IA dedicado DRP-A13 de Renesas permite un procesamiento de inferencia de IA de alta velocidad que alcanza el bajo consumo y la flexibilidad que requieren los terminales.

- Vídeo y gráficos: Unidad de procesamiento gráfico (GPU) opcional e ISP que ayudan a procesar imágenes y renderizar gráficos de forma más eficiente.

- Temporizadores: Los temporizadores admiten operaciones en tiempo real, que son esenciales para el control de motores y otras aplicaciones de automatización.

- Bloque de audio: Ideal para aplicaciones de audio multicanal, como altavoces inteligentes y sistemas de infoentretenimiento.

- Interfaces: Las interfaces de memoria de alta velocidad y los periféricos de gran ancho de banda son algunas de las muchas interfaces que se pueden conectar al módulo microprocesador de visión.

- Bloque analógico: Un convertidor analógico-digital (ADC) de 12 bits elimina la necesidad de ADC independientes en sistemas de control o aplicaciones de monitorización.

Renesas también ofrece el kit de placa de evaluación RTK0EF0186C03000BJ para el RZ/V2N, que permite a los diseñadores crear prototipos y evaluar aplicaciones de IA visual (Figura 4). Los diseñadores también pueden acceder a aplicaciones de IA que cubren más de 50 casos de uso en las aplicaciones de IA de la empresa y en el SDK de IA en GitHub.

Figura 4: El kit de la placa de evaluación para el RZ/V2N incluye una placa CPU, una placa de expansión y dos subplacas, junto con un SDK de IA. (Fuente de la imagen: Renesas Electronics Corp.)

Conclusión

El RZ/V2N de Renesas es ideal para aplicaciones de IA en el borde de gama media que necesitan proporcionar información basada en datos con una latencia reducida a altas velocidades. Su tamaño compacto y su capacidad para satisfacer las demandas de inferencia mientras funciona con bajo consumo lo hacen adecuado para una amplia gama de dispositivos integrados.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.