Fundamentos de seguridad de IoT - Parte 4: Mitigación de las amenazas de la duración de la operación

Colaboración de Editores de DigiKey de América del Norte

2020-06-25

Nota del editor: A pesar de la proliferación de dispositivos de IoT, la seguridad de estos dispositivos sigue siendo una preocupación constante, hasta el punto de que los desafíos de seguridad pueden ser una barrera para la adopción de dispositivos conectados en IoT industrial (IIoT) y aplicaciones de misión crítica donde los datos corporativos y personales pueden verse comprometidos en caso de un ataque exitoso. La seguridad de las aplicaciones de IoT puede ser desalentadora, pero en realidad la seguridad de los dispositivos de IoT se puede construir sobre unos pocos principios relativamente sencillos que se apoyan en los dispositivos de seguridad del hardware. Siguiendo prácticas de seguridad bien establecidas, se pueden abordar estas preocupaciones. Esta serie, que consta de varias partes, ofrece orientación práctica para ayudar a los promotores a asegurarse de que se sigan las mejores prácticas desde el principio. En la Parte 1, se analizan los algoritmos criptográficos que subyacen a los diseños seguros. En la Parte 2, se analiza el papel de las claves privadas, la administración de claves y el almacenamiento seguro en los diseños de IoT segura. En laParte 3, se examinan los mecanismos incorporados en los procesadores seguros para mitigar otros tipos de amenazas a los dispositivos de IoT. Aquí, la Parte 4 identifica y muestra cómo aplicar mecanismos de seguridad en los procesadores avanzados para ayudar a garantizar el aislamiento necesario para mitigar los ataques al entorno en tiempo de ejecución de los dispositivos de IoT. En la Parte 5, se describe cómo la seguridad de la IoT continúa desde los dispositivos de IoT a través de medidas de seguridad de mayor nivel utilizadas para conectar esos dispositivos a los recursos de la nube de IoT.

La criptografía basada en hardware con almacenamiento seguro proporciona la base necesaria para implementar diseños seguros de IoT. El arranque seguro y la actualización del firmware seguro en el aire (FOTA) usan esta base para construir una raíz de confianza para la ejecución del software. No obstante, un dispositivo de la Internet de las cosas (IoT) requiere una protección continua contra el software que puede comprometer accidental o intencionalmente los recursos seguros a los que se accede mediante una aplicación de software y el código de sistema que se ejecuta en el entorno de ejecución.

En este artículo se describe cómo los desarrolladores pueden utilizar mecanismos de seguridad integrados en algunos procesadores de NXP Semiconductors, STMicroelectronics, y otros para proteger más eficazmente los sistemas de las amenazas que se producen durante la ejecución del software.

Cómo se puede subvertir el software en tiempo de ejecución

Como se ha discutido en partes anteriores de esta serie, los cifrados, el almacenamiento seguro de claves, y el arranque seguro y la actualización del firmware proporcionan los bloques de construcción necesarios para la seguridad de la IoT. Aunque estas capacidades contribuyen de manera crítica a la seguridad general de los dispositivos de IoT, pueden presentar una solución incompleta a los ataques diseñados para subvertir el software en tiempo de ejecución en los sistemas conectados. Lo ideal sería que los intentos de penetrar las líneas de defensa proporcionadas por estos mecanismos fracasaran gracias al entorno de confianza construido sobre la base de la confianza creada a través del arranque seguro. En la práctica, los sistemas construidos con estas sólidas capacidades de seguridad pueden ser -y han sido- comprometidos por ataques que inyectan en el sistema un trozo de código corrupto o malware.

Al utilizar una amplia variedad de métodos, los hackers pueden explotar las vulnerabilidades de seguridad en una parte del sistema para atacar otras partes. Los ataques por desbordamiento del búfer, por ejemplo, aprovechan las aplicaciones de software que permiten que grandes flujos de datos de entrada escriban más allá del área de búfer prevista. Si ese desbordamiento de datos contiene código, el procesador podría ejecutarlo más tarde, proporcionando a los hackers un punto de entrada para futuros ataques. Al usar estos y otros métodos, los hackers amplían gradualmente su penetración en partes más amplias de un sistema.

Las vulnerabilidades pueden existir en cualquier componente de software en cualquier capa de la pila de software de un sistema. A medida que los desarrolladores trabajan para crear sistemas más funcionales, la necesidad de más componentes de software aumenta la posibilidad de que sus sistemas sufran más vulnerabilidades. Al mismo tiempo, la variedad de vulnerabilidades encontradas en los programas informáticos sigue creciendo. Por ejemplo, la lista autorizada de Vulnerabilidades y Exposiciones Comunes (CVE®) de vulnerabilidades de seguridad cibernética conocidas públicamente mostró un aumento del 15% interanual en el primer trimestre de 2020.

Los niveles de protección protegen el software crítico.

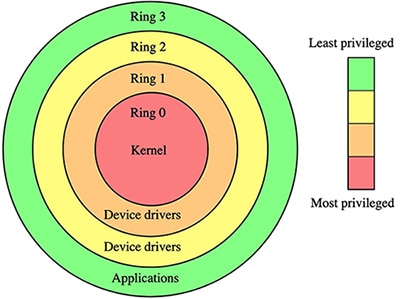

La mitigación de amenazas es una batalla constante entre los hackers de sombrero negro y los especialistas en seguridad de sombrero blanco. Aunque las amenazas seguirán apareciendo, los desarrolladores pueden reforzar considerablemente la seguridad de sus diseños aprovechando los métodos diseñados para aislar los múltiples procesos de software diferentes que se requieren en una aplicación típica. Durante años, los sistemas de seguridad se han construido sobre un enfoque de protección escalonado. En este enfoque clásico, los anillos concéntricos de protección proporcionan niveles crecientes de aislamiento en un sistema. Las aplicaciones que se ejecutan en la capa más externa tienen restringido el acceso a los controladores de los dispositivos y a los servicios del sistema en las capas internas, que a su vez tienen restringido el acceso al núcleo del software en la capa más interna (Figura 1).

Figura 1: Los sistemas de software seguro protegen las aplicaciones, los controladores y los núcleos del sistema operativo en anillos de protección que presentan una protección progresivamente mayor. (Fuente de la imagen: Wikipedia)

Figura 1: Los sistemas de software seguro protegen las aplicaciones, los controladores y los núcleos del sistema operativo en anillos de protección que presentan una protección progresivamente mayor. (Fuente de la imagen: Wikipedia)

Los dispositivos Intel x86 que comienzan con el 80286, ahora disponibles en Rochester Electronics, soportan cuatro niveles, designados mediante un registro de selección que incluye un campo de nivel de privilegio solicitado (RPL) de dos bits. Las modernas arquitecturas de los procesadores como Arm® TrustZone han ampliado significativamente las capacidades de seguridad mediante una variedad de mecanismos diseñados para aislar los procesos del usuario durante el tiempo de ejecución. Los desarrolladores pueden encontrar este tipo de capacidad de protección escalonada en una serie de procesadores de sistemas incorporados, entre ellos:

- Familia de microcontroladores SAM L11 deMicrochip Technology basada en el Arm Cortex®-M23

- Sistemas inalámbricos en chip (SoC) nRF9160 de Nordic Semiconductor basados en Arm Cortex-M33

- Microcontrolador M2351 Nuvoton Technology basado en Arm Cortex-M23

- Microcontroladores LPC55 de NXP Semiconductors basados en Arm Cortex-M33

- Familia de SoC inalámbricos EFR32BG21 de Silicon Labs basados en Arm Cortex-M33

- Familia de microcontroladores STM32L5 de STMicroelectronics basada en Arm Cortex-M33

Arm TrustZone para Cortex-M aporta capacidades de seguridad mejoradas a los procesadores de sistemas integrados de Arm Cortex-M, como el LPC55S69JBD100K de NXP y STM32L552VET6 de STMicroelectronics. TrustZone para Cortex-A proporciona capacidades similares para los procesadores de aplicaciones basados en Cortex-A como el NXP i.MX 8M Mini MIMX8MM6DVTLZAA y STM32MP157AAC3T de STMicroelectronics.

Para cada serie de Arm, TrustZone ofrece mecanismos que soportan el arranque seguro y el código seguro, datos y memoria, entre otras características de seguridad. Diseñado para soportar los requisitos de baja latencia de los sistemas incorporados, TrustZone para los procesadores Cortex-M presenta mejoras en el rendimiento, incluyendo rápidas interrupciones seguras y rápidas transiciones basadas en hardware entre los estados de seguridad. Este artículo describe la TrustZone para los procesadores Cortex-M centrándose en un par de procesadores representativos de esta clase: LPC55S69JBD100K de NXP y STM32L552VET6 de STMicroelectronics.

Los modos de funcionamiento del procesador permiten una protección ampliada.

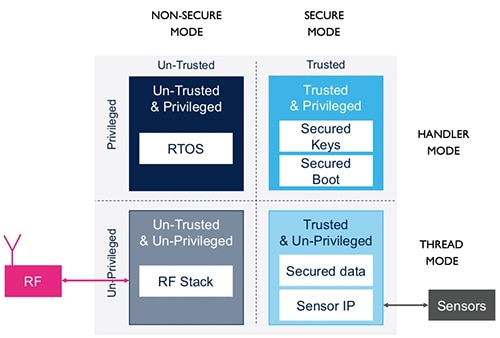

En el corazón de la arquitectura de TrustZone, los procesadores pueden funcionar en múltiples modos de operación que soportan el aislamiento de los procesos de software y los recursos del sistema. Los modos "seguro" y "no seguro" de los procesadores proporcionan una forma de aislar los procesos confiables de los no confiables. Los modos "manipulador" e "hilo" del procesador proporcionan un mecanismo de protección separado que ofrece una mayor granularidad en el aislamiento de los procesos y recursos.

En la arquitectura TrustZone, un procesador que se ejecuta en modo de administrador hace que el software se ejecute siempre en modo privilegiado. Como tal, es el modo recomendado para la ejecución de software como un sistema operativo en tiempo real (RTOS) o el acceso a la imagen de arranque, claves seguras y otros recursos críticos para el funcionamiento del sistema. En el modo de hilo, el software se ejecuta en modo no privilegiado, pero los procesos privilegiados pueden cambiar el nivel de privilegio del software que se ejecuta en este modo. El modo de hilo se usa generalmente para ejecutar el código de la aplicación.

Al usarse en combinación, los modos seguro/no seguro y manipulador/hilo ofrecen el mismo tipo de protección escalonada que se encuentra en los sistemas anteriores que soportan anillos de protección. Al usar el STM32L552VET6 de STMicroelectronics, por ejemplo, los desarrolladores pueden aislar el código de confianza con plenos privilegios del código no fiable con privilegios mínimos (Figura 2).

Figura 2: Los procesadores TrustZone como el STM32L552VET6 de STMicroelectronics proporcionan una combinación de modos de procesador que permiten a los desarrolladores aislar el software del sistema de confianza, como las imágenes de arranque, del código de aplicación no fiable, como las pilas de comunicaciones de radiofrecuencia (RF) de terceros. (Fuente de la imagen: Digi-Key, del material de la fuente de STMicroelectronics)

Figura 2: Los procesadores TrustZone como el STM32L552VET6 de STMicroelectronics proporcionan una combinación de modos de procesador que permiten a los desarrolladores aislar el software del sistema de confianza, como las imágenes de arranque, del código de aplicación no fiable, como las pilas de comunicaciones de radiofrecuencia (RF) de terceros. (Fuente de la imagen: Digi-Key, del material de la fuente de STMicroelectronics)

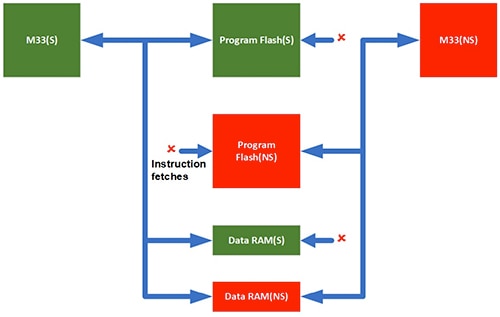

Los mecanismos de aislamiento integrados en estos procesadores restringen la capacidad de cada uno de ellos para acceder a diferentes áreas de la memoria de datos de programas. Por ejemplo, cuando el núcleo LPC55S6x de NXP está en estado seguro, no puede acceder a la memoria de programa no segura, aunque sí a la memoria de datos no segura. Por otro lado, cuando el núcleo LPC55S6x funciona en el estado no seguro, solo puede acceder a la memoria de programa y a la memoria de datos no segura (Figura 3).

Figura 3: Los procesadores como los dispositivos LPC55S6x de NXP pueden asegurar que el núcleo funciona en estado seguro (estado S) para leer la memoria de programa segura (verde) o en estado no seguro (estado NS) para leer la memoria de programa no segura (rojo). (Fuente de la imagen: NXP Semiconductors)

Figura 3: Los procesadores como los dispositivos LPC55S6x de NXP pueden asegurar que el núcleo funciona en estado seguro (estado S) para leer la memoria de programa segura (verde) o en estado no seguro (estado NS) para leer la memoria de programa no segura (rojo). (Fuente de la imagen: NXP Semiconductors)

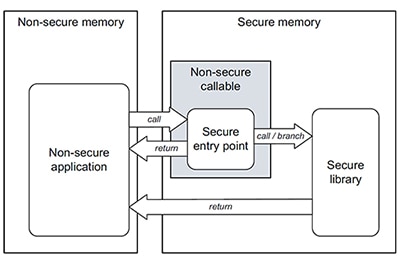

Cuando se ejecutan en el estado seguro para ejecutar software de confianza, estos procesadores no pueden obtener instrucciones de la memoria de programa no segura. Por el contrario, cuando se ejecutan en el estado no seguro para ejecutar software no fiable como el código de aplicación, estos procesadores no pueden acceder al código o a los datos ubicados en áreas seguras. No obstante, el código de la aplicación suele requerir la capacidad de ejecutar código de confianza en bibliotecas seguras. Los procesadores TrustZone permiten a los desarrolladores cumplir con este requisito al definir regiones de memoria no seguras llamables (NSC) que proporcionan puntos de entrada permitidos a bibliotecas seguras (Figura 4).

Figura 4: Las regiones no seguras de llamada proporcionan puntos de entrada seguros desde regiones de memoria no seguras a seguras, permitiendo que las aplicaciones no seguras ejecuten funciones en bibliotecas seguras. (Fuente de la imagen: STMicroelectronics)

Figura 4: Las regiones no seguras de llamada proporcionan puntos de entrada seguros desde regiones de memoria no seguras a seguras, permitiendo que las aplicaciones no seguras ejecuten funciones en bibliotecas seguras. (Fuente de la imagen: STMicroelectronics)

Los alias de memoria mejoran la seguridad

Los procesadores TrustZone como el LPC55S69JBD100K de NXP y el STM32L552VET6 de STMicroelectronics gestionan la ejecución mediante el aliasing de la memoria física del programa en espacios de memoria seguros y no seguros. Por ejemplo, los alias de STM32L552VET6 de STMicroelectronics se codifican en flash y SRAM dos veces en un rango de direcciones no seguras (0x0800_0000 a 0x0BFF_FFFF) y otra vez en un rango de direcciones seguras (0x0C00_0000 a 0x0FFF_FFFF). De manera similar, el LPC55S69JBD100K de NXP solapa la memoria física del programa en un espacio no seguro a partir de 0x0000_0000 y también en un espacio seguro a partir de 0x1000_0000. Cada uno de estos procesadores utiliza un enfoque similar para otros tipos de memoria y periféricos, solapándolos dos veces en regiones seguras y no seguras.

Cuando el procesador necesita acceder a una ubicación de memoria, la capacidad de acceso a esa ubicación está determinada por un atributo de seguridad generado por dos unidades de hardware:

- Unidad de Atribución Definida por Implementación (IDAU), que es una unidad de hardware fija externa al núcleo del procesador que proporciona un estado de seguridad fijo del mapa de la memoria según lo definido por el fabricante.

- Unidad de Atribución Segura (SAU), que es una unidad programable integrada en el núcleo del procesador que se utiliza para definir el estado de seguridad de hasta ocho regiones de memoria.

Durante la inicialización del sistema, las rutinas de configuración que se ejecutan en modo seguro definen el estado de seguridad de cada región estableciendo algunos registros SAU, entre ellos:

- Registro de números de región SAU (SAU_RNR) para seleccionar una región para operaciones posteriores

- Registro de direcciones de base de la región SAU (SAU_RBAR) para definir la dirección inicial de la región

- Registro de direcciones de límite de la región SAU (SAU_RLAR) para definir la extensión de la región

Incluido en su paquete de software STM32Cube MCU para la serie STM32L5, STMicroelectronics proporciona múltiples archivos de plantillas que demuestran el uso de las características del procesador, incluyendo la configuración SAU. Como se muestra en el Listado 1, los desarrolladores pueden definir estas regiones para cada parámetro de configuración utilizando un macro (SAU_INIT_REGION(n)) que establece los valores de registro en una estructura SAU utilizada cuando se escriben los ajustes de configuración en el dispositivo.

Copiar

/*

// <e>Initialize SAU Region 0

// <i> Setup SAU Region 0 memory attributes

*/

#define SAU_INIT_REGION0 1

/*

// <o>Start Address <0-0xFFFFFFE0>

*/

#define SAU_INIT_START0 0x0C03E000 /* start address of SAU region 0 */

/*

// <o>End Address <0x1F-0xFFFFFFFF>

*/

#define SAU_INIT_END0 0x0C03FFFF /* end address of SAU region 0 */

/*

// <o>Region is

// <0=>Non-Secure

// <1=>Secure, Non-Secure Callable

*/

#define SAU_INIT_NSC0 1

/*

// </e>

*/

/*

// <e>Initialize SAU Region 1

// <i> Setup SAU Region 1 memory attributes

*/

#define SAU_INIT_REGION1 1

/*

// <o>Start Address <0-0xFFFFFFE0>

*/

#define SAU_INIT_START1 0x08040000 /* start address of SAU region 1 */

/*

// <o>End Address <0x1F-0xFFFFFFFF>

*/

#define SAU_INIT_END1 0x0807FFFF /* end address of SAU region 1 */

/*

// <o>Region is

// <0=>Non-Secure

// <1=>Secure, Non-Secure Callable

*/

#define SAU_INIT_NSC1 0

/*

// </e>

*/

.

.

.

**

\brief Setup a SAU Region

\details Writes the region information contained in SAU_Region to the

registers SAU_RNR, SAU_RBAR, and SAU_RLAR

*/

__STATIC_INLINE void TZ_SAU_Setup (void)

{

#if defined (__SAUREGION_PRESENT) && (__SAUREGION_PRESENT == 1U)

#if defined (SAU_INIT_REGION0) && (SAU_INIT_REGION0 == 1U)

SAU_INIT_REGION(0);

#endif

.

.

.

#define SAU_INIT_REGION(n) \

SAU->RNR = (n & SAU_RNR_REGION_Msk); \

SAU->RBAR = (SAU_INIT_START##n & SAU_RBAR_BADDR_Msk); \

SAU->RLAR = (SAU_INIT_END##n & SAU_RLAR_LADDR_Msk) | \

((SAU_INIT_NSC##n << SAU_RLAR_NSC_Pos) & SAU_RLAR_NSC_Msk) | 1U

Listing 1: Incluido en las plantillas del paquete de software MCU STM32Cube de STMicroelectronics para la serie STM32L5, este fragmento muestra cómo los desarrolladores definen las regiones de memoria y su estado de seguridad asociado. (Fuente del código: STMicroelectronics)

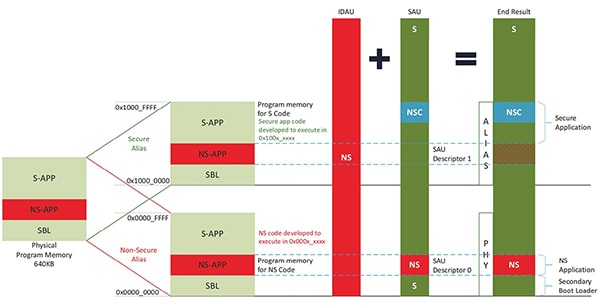

La IDAU y la SAU trabajan en conjunto para determinar si la ubicación de la memoria es accesible, devolviendo el más alto nivel de seguridad de los dos. Dado que un procesador trabaja con el alias de memoria correspondiente a su estado operativo seguro/no seguro, el atributo de seguridad generado por la combinación de la IDAU y la SAU asegura la accesibilidad solo a las regiones con el nivel de seguridad correspondiente (figura 5).

Figura 5: En el LPC55S69JBD100K de NXP, el IDAU y el SAU se combinan para generar un atributo de seguridad para cada alias de memoria, eliminando efectivamente el código que no puede salir de cada región respectiva. (Fuente de la imagen: NXP Semiconductors)

Figura 5: En el LPC55S69JBD100K de NXP, el IDAU y el SAU se combinan para generar un atributo de seguridad para cada alias de memoria, eliminando efectivamente el código que no puede salir de cada región respectiva. (Fuente de la imagen: NXP Semiconductors)

Por ejemplo, cuando el LPC55S69JBD100K de NXP está funcionando en modo seguro, el atributo de seguridad generado por el IDAU y el SAU impedirá el acceso a las aplicaciones no seguras contenidas en el alias seguro de un bloque de memoria física, eliminando efectivamente ese código no seguro del alias seguro. Por el contrario, cuando el procesador funciona en modo no seguro, el atributo de seguridad IDAU y SAU eliminará efectivamente las aplicaciones seguras del alias no seguro resultante.

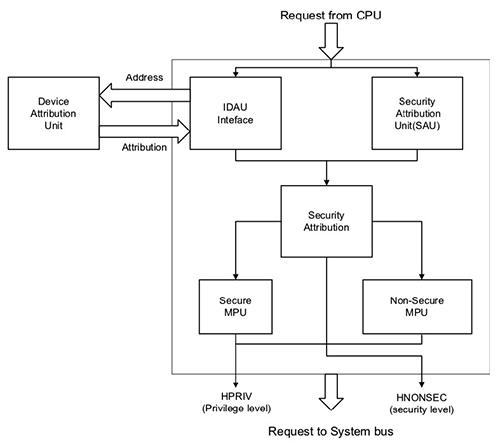

Configuración de privilegios y control de acceso

Si bien la AIDU y la UAE aplican directamente restricciones de acceso seguras y no seguras, trabajan con unidades de protección de memoria (UPM) seguras y no seguras para determinar los derechos de acceso asociados al recurso objetivo (figura 6).

Figura 6: En los procesadores de TrustZone como el LPC55S69JBD100K de NXP ilustrado aquí, el atributo de seguridad generado por el SAU y el IDAU se combina con configuraciones administradas por MPU seguras y no seguras para entregar el nivel de privilegio junto con el nivel de seguridad. (Fuente de la imagen: NXP Semiconductors)

Figura 6: En los procesadores de TrustZone como el LPC55S69JBD100K de NXP ilustrado aquí, el atributo de seguridad generado por el SAU y el IDAU se combina con configuraciones administradas por MPU seguras y no seguras para entregar el nivel de privilegio junto con el nivel de seguridad. (Fuente de la imagen: NXP Semiconductors)

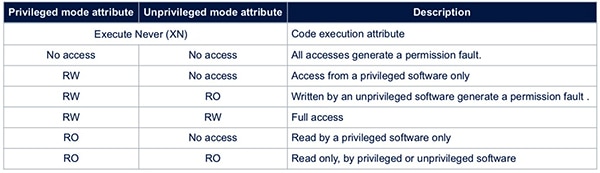

Construido en estos procesadores, el MPU proporciona un control de acceso de grano fino a los recursos de la memoria. En el STM32L552VET6 de STMicroelectronics, por ejemplo, el MPU admite una variedad de derechos de acceso que difieren cuando el procesador se ejecuta en modo de manejador privilegiado o en modo de hilo no privilegiado (Tabla 1).

Tabla 1: El STM32L552VET6 de STMicroelectronics permite a los desarrolladores utilizar su MPU para definir diferentes niveles de acceso que operan de manera diferente en modo privilegiado y no privilegiado. (Fuente de la tabla: STMicroelectronics)

Tabla 1: El STM32L552VET6 de STMicroelectronics permite a los desarrolladores utilizar su MPU para definir diferentes niveles de acceso que operan de manera diferente en modo privilegiado y no privilegiado. (Fuente de la tabla: STMicroelectronics)

Entre esos atributos, el atributo "Execute Never" (Ejecutar nunca) (XN) permite a los desarrolladores asegurarse de que el procesador nunca intente ejecutar código de la región de memoria asociada, proporcionando otro nivel de protección en tiempo de ejecución. Por ejemplo, en los sistemas que ejecutan el código directamente desde el flash, los desarrolladores pueden establecer el atributo XN para las regiones SRAM no utilizadas para eliminar cualquier posibilidad de que el sistema se vea comprometido, incluso si los ataques de inyección de malware tienen éxito con esas áreas.

Extendiendo la protección a más periféricos y a la memoria

Las características IDAU, SAU y MPU de estos procesadores proporcionan una base flexible para proteger la ejecución en tiempo de ejecución tanto del software del sistema como de las aplicaciones, pero estas capacidades se limitan al propio procesador. Los procesadores como el LPC55S69JBD100K de NXP y el STM32L552VET6 de STMicroelectronics llevan las capacidades de seguridad y privilegio a otros sistemas de memoria e interfaces a través de una variedad de enfoques.

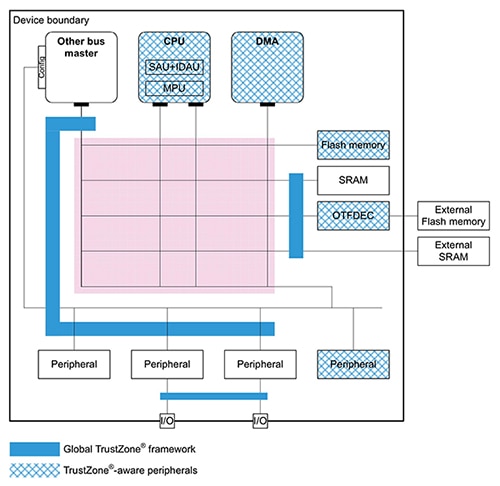

Para su STM32L552VET6, STMicroelectronics complementa el mecanismo nativo de TrustZone con su propio controlador global de TrustZone (GTZC), diseñado para proteger los periféricos, la SRAM incorporada y las memorias externas (Figura 7).

Figura 7: El procesador STMicroelectronics STM32L552VET6 integra un controlador TrustZone global (GTZC) que extiende la protección de seguridad a los periféricos y la memoria no incluidos en el marco TrustZone nativo. (Fuente de la imagen: STMicroelectronics)

Figura 7: El procesador STMicroelectronics STM32L552VET6 integra un controlador TrustZone global (GTZC) que extiende la protección de seguridad a los periféricos y la memoria no incluidos en el marco TrustZone nativo. (Fuente de la imagen: STMicroelectronics)

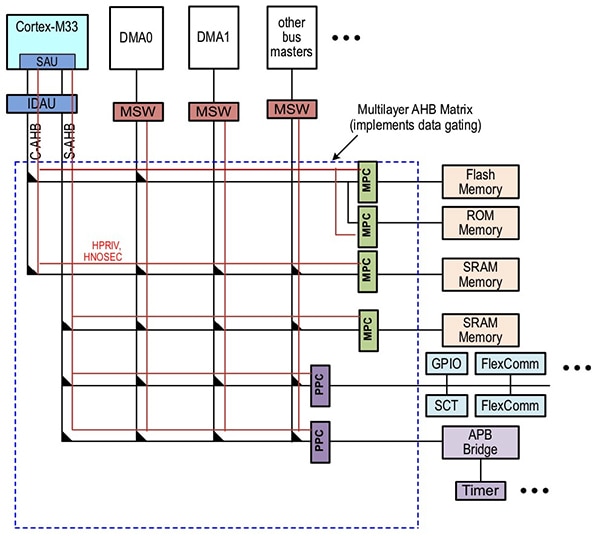

En el LPC55S69JBD100K de NXP, el atributo de privilegio (HPRIV) y el atributo de seguridad (HNONSEC) se llevan a través de la matriz interna del Bus Avanzado de Alto Rendimiento (AHB) para llegar a los Comprobadores de Protección de Memoria (MPC), los Comprobadores de Protección Periférica (PPC) y los Envoltorios de Seguridad Maestros (MSW) para otros maestros de bus (Figura 8).

Figura 8: En el LPC55S69JBD100K de NXP, los niveles de privilegio y seguridad se transmiten a unidades de hardware adicionales que aplican estos atributos a las operaciones relacionadas con la memoria, los periféricos y otros maestros de bus. (Fuente de la imagen: NXP Semiconductors)

Figura 8: En el LPC55S69JBD100K de NXP, los niveles de privilegio y seguridad se transmiten a unidades de hardware adicionales que aplican estos atributos a las operaciones relacionadas con la memoria, los periféricos y otros maestros de bus. (Fuente de la imagen: NXP Semiconductors)

Aunque es importante comprender los mecanismos subyacentes de aislamiento de los programas informáticos y de protección de los sistemas, los desarrolladores pueden aprovechar el apoyo al desarrollo para aplicar rápidamente esas capacidades en sus propios diseños.

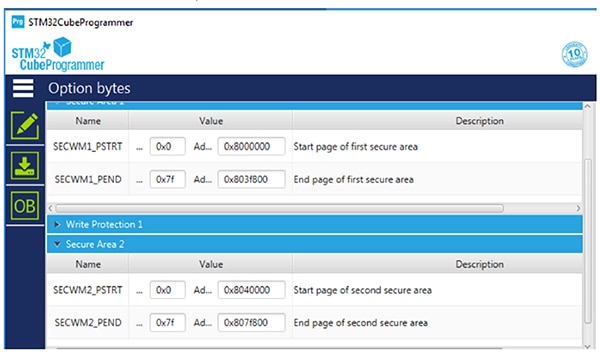

STMicroelectronics proporciona sus placas de evaluación STM32L552E-EV, STM32L562E-DK y NUCLEO-L552ZE-Q, como plataforma de prototipos rápidos para construir aplicaciones basadas en sus procesadores STM32L5. El entorno de desarrollo integrado (IDE) STM32CubeIDE de la empresa proporciona un entorno completo para la programación de software y su STM32CubeProgrammer ofrece versiones tanto de interfaz gráfica de usuario (GUI) como de interfaz de línea de comandos (CLI) para la programación de memorias internas y externas. Mediante esta herramienta, los desarrolladores pueden, por ejemplo, definir regiones seguras en la memoria flash (figura 9).

Figura 9: El programador STM32Cube de STMicroelectronics ofrece un enfoque simple para definir regiones seguras en la memoria flash. (Fuente de la imagen: STMicroelectronics)

Figura 9: El programador STM32Cube de STMicroelectronics ofrece un enfoque simple para definir regiones seguras en la memoria flash. (Fuente de la imagen: STMicroelectronics)

Para el rápido desarrollo de sistemas basados en los procesadores LPC55S69 de NXP, los desarrolladores pueden construir diseños en la placa de evaluación LPC55S69-EVK de NXP. Para la configuración del sistema y la programación del software, el IDEMCUXpresso de NXP proporciona una plataforma completa para crear aplicaciones basadas en los procesadores LPC55S69 de NXP.

Conclusión:

La seguridad de la IoT depende de mecanismos de seguridad fundamentales para la criptografía y el almacenamiento seguro, así como de la capacidad de construir aplicaciones sobre una base de confianza basada en mecanismos de seguridad de hardware. Aunque todos ellos son necesarios para la seguridad, rara vez son suficientes para contrarrestar las amenazas actuales destinadas a explotar las vulnerabilidades en los entornos de ejecución de los sistemas. Mediante el uso de mecanismos de protección por niveles disponibles en una gama cada vez más amplia de procesadores, los desarrolladores pueden crear dispositivos seguros de IoT que puedan mitigar mejor estas amenazas y reducir o eliminar su impacto en las aplicaciones de IoT.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.