Implementar la computación de borde de bajo consumo y alto rendimiento utilizando las FPGA habilitadas por el sistema Quantum de Efinix

Colaboración de Editores de DigiKey de América del Norte

2020-03-17

La computación clásica en la nube tiene problemas de latencia, seguridad de datos, privacidad del usuario final, ancho de banda disponible y conectividad confiable. Para hacer frente a esto, los diseñadores y arquitectos de sistemas se están moviendo hacia la computación de borde. Sin embargo, la computación de borde presenta su propio conjunto de desafíos, que van desde el costo, el tamaño, el rendimiento y el consumo de energía, hasta cuestiones de escalabilidad, flexibilidad y posibilidad de actualización. Esto es particularmente cierto ya que los diseñadores buscan hacer más procesamiento de imágenes e implementar más algoritmos de inteligencia artificial (AI) y aprendizaje automático (ML) más cercanos a la fuente de datos.

Como resultado, los diseñadores están mirando más allá de los microcontroladores tradicionales (MCU) o los procesadores de aplicaciones (AP) y considerando los conjuntos de puertas programables en campo (FPGA) con sus capacidades de procesamiento en paralelo. Las mejoras constantes en el diseño y la aplicación de las FPGA significan que ahora pueden satisfacer muchos o todos estos requisitos, ya sea como dispositivos autónomos o en conjunción con MCU y AP. Dicho esto, muchos diseñadores no están familiarizados con las FPGA y están preocupados por la curva de aprendizaje.

Este artículo analiza brevemente la migración de la nube a la computación de borde y por qué las arquitecturas de procesamiento tradicionales se quedan cortas en lo que se refiere al procesamiento de imágenes, así como a la IA y el ML. A continuación, proporciona una rápida mirada a las FPGA y por qué tienen una ventaja arquitectónica para estas aplicaciones de borde intensivas en datos. Por último, introduce un nuevo enfoque de las FPGA -la tecnología Quantum de Efinix y cómo aplicarla.

¿Por qué la computación de borde?

En la computación tradicional en la nube, los datos se recogen de innumerables lugares remotos y se introducen en un sistema basado en la nube para su almacenamiento y análisis. Sin embargo, este enfoque tiene muchas desventajas. Entre ellos figuran los costos de la transmisión de grandes cantidades de datos en bruto, el mantenimiento de la integridad y la seguridad de esos datos mientras están en tránsito, las latencias de respuesta, las preocupaciones por la privacidad de los usuarios finales y las conexiones a menudo poco fiables a la Internet y el uso no óptimo del ancho de banda disponible.

Como su nombre lo sugiere, la computación de borde significa mover el procesamiento, computación y análisis, más cerca del borde de la Internet, justo donde los datos están siendo generados, analizados, reunidos y aplicados. El término "computación de borde o edge computing" no es específico de la aplicación o del dispositivo, y los diseñadores pueden elegir el procesamiento sólo en el borde o un equilibrio entre la nube y el borde, según sea apropiado.

Las aplicaciones de borde incluyen fábricas inteligentes, ciudades inteligentes, casas inteligentes y transporte inteligente, sólo para mencionar algunas. Además, los dispositivos de borde pueden ir desde grandes servidores de borde de alta gama hasta sistemas de sensores y actuadores relativamente pequeños situados en el extremo de la Internet, en el punto de generación de datos.

La ventaja de las FPGA

En lo que respecta a la computación, los procesadores tradicionales son extremadamente eficientes en lo que se refiere a la toma de decisiones y a las tareas secuenciales, pero terriblemente ineficientes en lo que respecta a muchos algoritmos de procesamiento de datos, como los utilizados para el procesamiento de imágenes, la IA y el ML. Estas tareas a menudo pueden dividirse en conductos de procesamiento masivamente paralelos (frente a los secuenciales). En realidad, son precisamente estas aplicaciones las que están migrando hacia el borde y el extremo.

El hecho de que las FPGA puedan ser programadas (configuradas) para implementar cualquier combinación de funciones les permite ejecutar algoritmos de procesamiento de imágenes, IA y ML de forma masivamente paralela, minimizando así la latencia y reduciendo el consumo de energía. Además de su principal tejido programable, las FPGA vienen equipadas con bloques de procesamiento de señales digitales (DSP) en el chip que contienen multiplicadores especiales que aceleran dramáticamente las aplicaciones intensivas de DSP. Las FPGA también tienen bloques de memoria en el chip que facilitan el procesamiento en el chip, que es mucho más rápido que el de fuera del chip.

Hay un número de vendedores de FPGA, cada uno con sus propias ofertas. Uno de estos vendedores, Efinix, ha desarrollado una arquitectura especial de FPGA llamada Quantum que se adapta de manera única a la computación de borde en general, y al procesamiento de imágenes en particular. Alrededor de esa tecnología ha desarrollado su serie de FPGA de Trion (y Quantum ASIC) para ofrecer una ventaja de 4 áreas de rendimiento de potencia sobre las tecnologías tradicionales de FPGA (Figura 1). La unión de los dominios FPGA y ASIC es el entorno de desarrollo integrado (IDE) Efinity.

Figura 1: Con su ventaja en el área de rendimiento de potencia, las FPGA de Trion se dirigen a aplicaciones como la lógica personalizada, la aceleración de cómputo, el ML, el aprendizaje profundo y el procesamiento de imágenes. Con el Efinity IDE, los usuarios pueden migrar sin problemas de una FPGA de Trion a un Quantum ASIC para la producción de volumen ultra alto. (Fuente de la imagen: Efinix)

Figura 1: Con su ventaja en el área de rendimiento de potencia, las FPGA de Trion se dirigen a aplicaciones como la lógica personalizada, la aceleración de cómputo, el ML, el aprendizaje profundo y el procesamiento de imágenes. Con el Efinity IDE, los usuarios pueden migrar sin problemas de una FPGA de Trion a un Quantum ASIC para la producción de volumen ultra alto. (Fuente de la imagen: Efinix)

¿Qué es la tecnología Quantum?

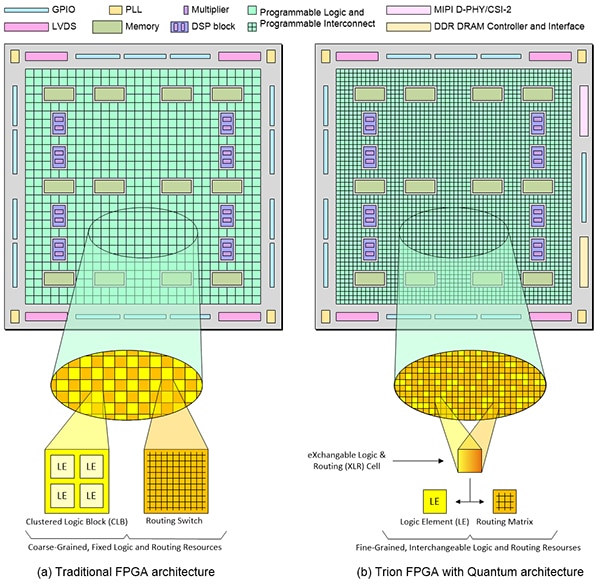

Al igual que las FPGA tradicionales, las FPGA de Trion incluyen bloques de memoria y DSP. La diferencia radica en el tejido programable (Figura 2). En el centro de la lógica programable, está el elemento lógico (LE). Cada LE incluye una tabla de búsqueda (LUT), un multiplexor y un registro, todos los cuales pueden ser configurados según sea necesario. En el caso de las FPGA tradicionales, su tejido programable puede describirse como "de grano grueso".

Figura 2: Una arquitectura tradicional de FPGA (a) es de grano grueso, y aunque la lógica y la interconexión son programables, siguen siendo recursos fijos. En comparación, las FPGA de Trion (b) basadas en la arquitectura Quantum son de grano fino, y sus recursos lógicos y de enrutamiento son intercambiables (Fuente de la imagen: Max Maxfield)

Figura 2: Una arquitectura tradicional de FPGA (a) es de grano grueso, y aunque la lógica y la interconexión son programables, siguen siendo recursos fijos. En comparación, las FPGA de Trion (b) basadas en la arquitectura Quantum son de grano fino, y sus recursos lógicos y de enrutamiento son intercambiables (Fuente de la imagen: Max Maxfield)

En los tejidos de grano grueso, múltiples LE se reúnen en un bloque lógico agrupado más grande (CLB). Obsérvese que algunos vendedores usan el término bloque lógico configurable (CLB), mientras que otros usan bloque de matriz lógica (LAB), pero todos significan lo mismo.

Es importante señalar que esta ilustración es una abstracción. Los CLB y los interruptores de enrutamiento (interconexión programable) en los FPGA tradicionales no se presentan realmente en un patrón de tablero de ajedrez como se muestra aquí. Sin embargo, son fijos e inmutables en que la lógica programable siempre será la lógica programable, y la interconexión programable siempre será la interconexión programable.

En comparación con las arquitecturas tradicionales, las FPGA de Trion tienen un grano mucho más fino, hasta la resolución de un solo elemento lógico. Además, cada célula lógica intercambiable y de enrutamiento (XLR) puede ser configurada para actuar como una LE o como parte de la matriz de enrutamiento.

Las células de configuración utilizadas en la arquitectura Quantum están basadas en SRAM, lo que significa que esta tecnología es "agnóstica al silicio". Pueden fabricarse utilizando cualquier proceso estándar de CMOS sin necesidad de los pasos de procesamiento especiales que exigen las tecnologías de configuración alternativas, como el flash y el antifuse, que se utilizan en algunas FPGA de gama media.

Es esta lógica y encaminamiento configurables por software y la interconexión adaptativa de alto rendimiento lo que da al enfoque basado en el Quantum una mejora de 4 veces en términos de área de rendimiento de potencia (PPA) en comparación con las tradicionales FPGA basadas en SRAM creadas en el mismo nodo de tecnología de procesos.

Además, las FPGA creadas con la arquitectura Quantum requieren sólo siete capas de metalización, a diferencia de las más de 12 que exigen las FPGA tradicionales. Dado que cada capa adicional de metal requiere múltiples pasos de máscara y proceso, el uso de sólo siete capas reduce los costos de diseño y fabricación y aumenta el rendimiento.

Todas estas características y prestaciones son muy útiles para los diseñadores que buscan ventajas de coste, tamaño, rendimiento y flexibilidad para la computación de borde y el procesamiento de imágenes. Como tal, las FPGA de Trion son ideales tanto para las aplicaciones tradicionales de FPGA como para las aplicaciones emergentes de computación de borde y de procesamiento de imágenes. Entre estos últimos se encuentran los móviles, el Internet de las cosas (IoT), la automatización, la robótica, la fusión de sensores, la visión por ordenador, la IA y el ML.

La estructura de las FPGA de Trion

Las FPGA de Trion se fabrican en un proceso de silicio de baja potencia de 40 nanómetros (nm) con entre cuatro mil (K) y 200K LEs, aunque el proceso es escalable a dispositivos mucho más grandes. Todas las FPGA de Trion incluyen bloques de memoria y DSP, pero su capacidad y número varían dependiendo del tamaño del dispositivo. Los dispositivos más pequeños como el T4F81C2 son más minimalistas en sus características (es decir, 3.888 LEs, 78.848 bits de memoria, 59 GPIO) y están dirigidos a las funciones de los aviones de control de mano.

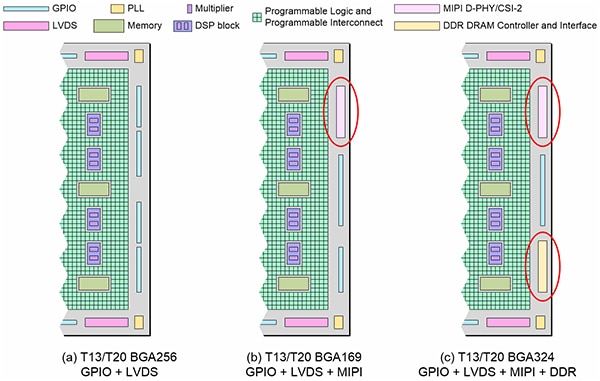

Los dispositivos de gama alta como el T20F256C3 contienen correspondientemente más recursos (es decir, 19.728 LE, 1.069.548 bits de memoria, 195 GPIO). El T13F256C3 es similar al T20F256C3, pero tiene 12.828 LE. Además, los dispositivos como el T13/T20 vienen en diferentes versiones (Figura 3).

Figura 3: Los Efinix T13/T20 BGA256s (a) son una FPGA genérica que son una buena opción para diseños con necesidades intensivas de E/S; los T13/T20 BGA169s (b) incluyen dos bloques de núcleo duro MIPI D-PHY/CSI-2 para diseños que necesitan soportar la interfaz de cámara MIPI; y los T13/T20 BGA324s (c) aumentan las interfaces MIPI con una interfaz y controlador DRAM de núcleo duro x16-bit de doble velocidad de datos (DDR) para diseños con necesidades intensivas de ancho de banda de memoria. (Fuente de la imagen: Max Maxfield)

Figura 3: Los Efinix T13/T20 BGA256s (a) son una FPGA genérica que son una buena opción para diseños con necesidades intensivas de E/S; los T13/T20 BGA169s (b) incluyen dos bloques de núcleo duro MIPI D-PHY/CSI-2 para diseños que necesitan soportar la interfaz de cámara MIPI; y los T13/T20 BGA324s (c) aumentan las interfaces MIPI con una interfaz y controlador DRAM de núcleo duro x16-bit de doble velocidad de datos (DDR) para diseños con necesidades intensivas de ancho de banda de memoria. (Fuente de la imagen: Max Maxfield)

El MIPI CSI-2 es la interfaz de cámara más utilizada en los mercados de telefonía móvil y otros mercados debido a su baja potencia, baja latencia y bajo costo de conectividad chip a chip. También es compatible con una amplia gama de formatos de alto rendimiento, incluidos los de vídeo de 1080p, 4K, 8K (y más), así como con imágenes de alta resolución. De particular interés aquí es el hecho de que el MIPI CSI-2 es la interfaz predominante usada para los sensores de visión en las aplicaciones de borde. Para apoyar los diseños de estas aplicaciones, las FPGA T13/T20 BGA169s incluyen dos bloques de núcleo duro MIPI D-PHY/CSI-2 (Figura 3, de nuevo).

La memoria DDR soporta transferencias de datos de gran ancho de banda, pero también requiere el cumplimiento de un estricto protocolo de cronometraje. Además de las interfaces MIPI D-PHY/CSI-2 endurecidas, los Trion T13/T20 BGA324s (Figura 3, de nuevo) también incluyen una interfaz y un controlador DRAM DDR endurecido de x16 bits para diseños con necesidades intensivas de ancho de banda de memoria.

Quantum ASIC

Como se ha señalado anteriormente, las células de configuración utilizadas en las FPGA de Trion están basadas en SRAM. Como resultado, cuando el sistema se enciende por primera vez, las FPGA de Trion necesitan tener sus datos de configuración cargados, ya sea desde un dispositivo de memoria externa o mediante "bit-banging" a través del procesador anfitrión. Para hacer esto en la producción de volumen ultra alto, Efinix también ofrece soluciones FPGA integrado (eFPGA) de Quantum Accelerated en forma de Quantum ASIC. En este caso, Efinix puede tomar diseños T4, T8, T13 o T20 y crear versiones de Quantum ASIC programadas con máscara que arrancan internamente sin necesidad de un dispositivo de configuración externo.

Diseño y desarrollo con FPGA de Trion

Efinix ofrece una variedad de tablas de evaluación y kits de desarrollo para permitir a los usuarios familiarizarse con las FPGA de Trion. Estos incluyen el kit de desarrollo de la FPGA de Trion T8F81C-DK T8 Trion, la tarjeta de evaluación de la FPGA de Trion T20F256C-DK T20 Trion, y el kit de desarrollo del MIPI D-PHY/CSI-2 de Trion T20MIPI-DK T20.

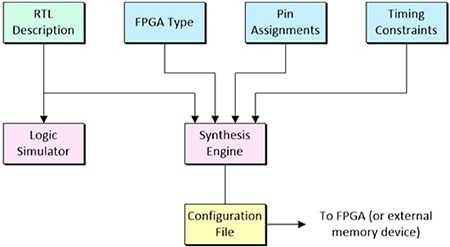

Una de las técnicas más comunes utilizadas para desarrollar con FPGA se llama diseño dirigido por el lenguaje (LDD). Esto implica capturar la intención del diseño a un nivel de abstracción conocido como nivel de transferencia de registro (RTL) utilizando un lenguaje de descripción de hardware (HDL) como Verilog o VHDL. Tras la verificación mediante simulación lógica, esta representación se introduce en un motor de síntesis, junto con información adicional como el tipo de FPGA del objetivo, las asignaciones de los pines y las limitaciones de tiempo, como los retrasos máximos de entrada y salida. La salida del motor de síntesis es un archivo de configuración que se carga directamente en la FPGA o en un dispositivo de memoria externa (Figura 4).

Figura 4: Tras la verificación mediante simulación lógica, la descripción del diseño RTL se introduce en un motor de síntesis junto con detalles de diseño adicionales como el tipo de FPGA, las asignaciones de pines y las restricciones de tiempo. La salida del motor de síntesis es un archivo de configuración que se carga en la FPGA. (Fuente de la imagen: Max Maxfield)

Figura 4: Tras la verificación mediante simulación lógica, la descripción del diseño RTL se introduce en un motor de síntesis junto con detalles de diseño adicionales como el tipo de FPGA, las asignaciones de pines y las restricciones de tiempo. La salida del motor de síntesis es un archivo de configuración que se carga en la FPGA. (Fuente de la imagen: Max Maxfield)

El IDE Efinity de Efinix entra dentro de esta clase de herramientas. Este software proporciona un flujo completo de RTL a flujo de bits con una interfaz gráfica de usuario (GUI) sencilla y fácil de usar y soporte de escritura de línea de comandos. Un tablero intuitivo guía al desarrollador a través del flujo (es decir, síntesis, colocación, enrutamiento, generación de flujo de bits), donde cada etapa puede ser controlada automática o manualmente. Los desarrolladores pueden utilizar el motor de síntesis de Efinity para aprovechar al máximo la arquitectura Quantum que aparece en las FPGA de Trion para generar dispositivos con las prometidas mejoras de 4x PPA.

Además de admitir flujos de simulación utilizando los simuladores ModelSim, NCSim o IVerilog libre, el IDE de Efinity también cuenta con un Diseñador de interfaz para restringir la lógica y asignar pines a los bloques en la periferia del dispositivo, un editor de planos para examinar la lógica y la colocación de las rutas de un diseño, un navegador de tiempo y análisis estático de tiempo para medir el rendimiento de un diseño, y un depurador de hardware integrado con analizador lógico y núcleos de depuración de E/S virtuales.

Conclusión

A medida que los diseñadores realizan más procesamiento de imágenes, IA y ML en el borde, en lugar de, o para complementar un enfoque basado en la nube, necesitan considerar las FPGA como parte de su arquitectura de procesamiento para abordar mejor cuestiones como el costo, el rendimiento, el consumo de energía, el tamaño, la escalabilidad, la flexibilidad y la posibilidad de actualización.

Para algunos diseñadores, esto puede implicar una curva de aprendizaje; pero como se ha demostrado, los avances en FPGA como la tecnología Quantum de Efinix pueden hacer que la inversión valga la pena rápidamente gracias a su menor costo, factores de forma más pequeños, mayor rendimiento y mayor flexibilidad.

Como resultado, las FPGA son ahora ideales tanto para las aplicaciones tradicionales de FPGA como para la computación emergente de borde para aplicaciones móviles, IO, automatización, robótica, fusión de sensores, visión por ordenador, IA y ML.

Recursos adicionales

- Fundamentos: La IO, la IOT, la IOA y por qué son el futuro de la automatización industrial

- Fundamentos de las FPGA: ¿Qué son las FPGA y por qué son necesarias?

- Fundamentos de las FPGA - Parte 2: Introducción a las FPGA de Lattice Semiconductor

- Fundamentos de las FPGA - Parte 3: Introducción a las FPGA de la tecnología del microchip

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.