Cómo usar una MRAM para mejorar la fiabilidad, reducir las latencias y disminuir la potencia de la informática de punta

Colaboración de Editores de DigiKey de América del Norte

2020-11-05

El uso de la computación de punta está creciendo a través de aplicaciones como la Internet Industrial de las Cosas (IIoT), la robótica, los dispositivos médicos, los artículos de vestir, la inteligencia artificial, la automoción y los diseños portátiles. Junto con este crecimiento está la necesidad de una memoria de alta velocidad, baja latencia, no volátil, de baja potencia y bajo costo para usos como el almacenamiento de programas y el respaldo de datos. Aunque hay muchas opciones disponibles, incluyendo la memoria estática de acceso aleatorio (SRAM), la memoria RAM dinámica (DRAM), el flash y la memoria programable de solo lectura (EEPROM) con borrado eléctrico, cada una de estas tecnologías ampliamente utilizadas requieren compensaciones en una o más áreas que las hacen menos que ideales para la computación de punta.

En su lugar, los diseñadores pueden recurrir a las memorias de acceso aleatorio magnetorresistivas (MRAM). Los dispositivos MRAM, como su nombre indica, almacenan datos en elementos de almacenamiento magnético y ofrecen un verdadero acceso aleatorio, permitiendo que tanto la lectura como la escritura ocurran de forma aleatoria en la memoria. Su estructura y funcionamiento son tales que se caracterizan por una baja latencia, bajas fugas, un alto número de ciclos de escritura y una alta retención, todo lo cual es muy deseable para la informática de vanguardia.

Este artículo compara brevemente las capacidades de rendimiento de las tecnologías de memoria comunes, incluyendo EEPROM, SRAM y flash con MRAM. A continuación, revisará los beneficios del uso de MRAM en varias aplicaciones informáticas de punta y luego introducirá dispositivos MRAM específicos de Renesas Electronics, algunos consejos de uso de MRAM y una plataforma de evaluación para ayudar a los diseñadores a comenzar su diseño.

Comparación de tecnologías de memoria

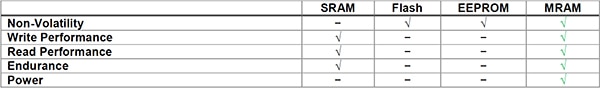

Los diseñadores de aplicaciones informáticas de vanguardia tienen varias tecnologías de memoria para elegir, cada una de las cuales ofrece diversas capacidades de rendimiento y compensaciones (Figura 1). La DRAM suele proporcionar la memoria de trabajo para varios tipos de procesadores durante la ejecución del software. Es barato, relativamente lento (comparado con el SRAM), consume cantidades significativas de energía, y retiene los datos solo mientras haya energía suministrada. Además, las celdas de memoria DRAM están sujetas a la corrupción por la radiación.

El SRAM es más rápido y más caro que el DRAM. A menudo se utiliza como memoria caché de los procesadores, mientras que la DRAM proporciona la memoria principal. Es el más hambriento de poder de los recuerdos que se describen aquí, y como el DRAM, es un recuerdo volátil. Las celdas SRAM están sujetas a la corrupción por la radiación, y tanto la DRAM como la SRAM proporcionan una gran resistencia.

La EEPROM es una memoria no volátil que utiliza un voltaje aplicado externamente para borrar los datos. Las EEPROM son lentas, tienen una resistencia limitada, generalmente hasta un millón de ciclos, y están relativamente hambrientas de energía. La EEPROM es actualmente la menos utilizada de las tecnologías de memoria que se describen aquí.

La memoria flash es una variación de la EEPROM, con una capacidad de almacenamiento sustancialmente mayor y con velocidades de lectura/escritura más rápidas, pero sigue siendo relativamente lenta. La memoria flash es barata y los datos sobreviven en condiciones de apagado hasta 10 años. Sin embargo, la flash es más compleja de usar en relación con otros tipos de memoria. Los datos deben ser leídos en bloques y no pueden ser leídos byte por byte. Además, antes de ser reescrito, las células deben ser borradas. El borrado debe realizarse bloque por bloque, no por bytes individuales.

La MRAM, por su parte, es una verdadera memoria de acceso aleatorio; permitiendo que tanto las lecturas como las escrituras ocurran al azar en la memoria. La MRAM también tiene cero fugas cuando está en espera, y combina la capacidad de soportar1016 ciclos de escritura con una capacidad de retención de datos de más de 20 años a 85 °C. Actualmente se ofrece en una densidad que va de 4 megabits (Mbits) a 16 Mbits.

La tecnología MRAM es análoga a la tecnología flash con tiempos de lectura/escritura compatibles con SRAM (MRAM a veces se denomina SRAM persistente (P-SRAM)). Debido a sus características, la MRAM es particularmente adecuada para aplicaciones que deben almacenar y recuperar datos con una latencia mínima. Combina esta baja latencia con baja potencia, resistencia infinita, escalabilidad y no volatilidad. La inmunidad inherente de la MRAM a las partículas alfa también lo hace adecuado para los dispositivos que se exponen regularmente a la radiación.

Figura 1: El MRAM no es volátil como el flash y el EEPROM y tiene tiempos de lectura/escritura compatibles con la SRAM. (Fuente de la imagen: Renesas Electronics)

Figura 1: El MRAM no es volátil como el flash y el EEPROM y tiene tiempos de lectura/escritura compatibles con la SRAM. (Fuente de la imagen: Renesas Electronics)

Cómo funciona la MRAM

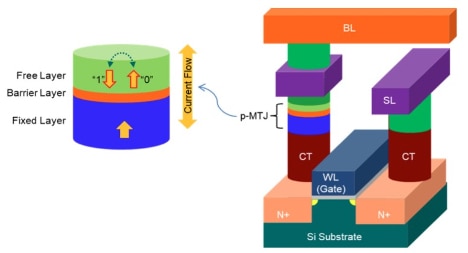

Como su nombre indica, los datos de la MRAM son almacenados por elementos de almacenamiento magnético. Los elementos están formados por dos placas ferromagnéticas, cada una de las cuales puede contener una magnetización, separadas por una fina capa aislante. Esta estructura se llama unión de túnel magnético (MTJ). Una de las dos placas es un imán permanente ajustado a una polaridad específica durante la fabricación; la magnetización de la otra placa puede cambiarse para almacenar datos. Renesas Electronics añadió recientemente dispositivos MRAM que utilizan un par de transferencia de giro MRAM (STT-MRAM) patentado que se basa en una unión de túnel magnético perpendicular (p-MTJ). La p-MTJ incluye una capa magnética fija e inalterable, una capa de barrera dieléctrica y una capa de almacenamiento ferromagnética cambiante (Figura 2).

Figura 2: La celda básica del STT-MRAM consiste en un MTJ y un transistor de acceso. (Fuente de la imagen: Avalanche Technology)

Figura 2: La celda básica del STT-MRAM consiste en un MTJ y un transistor de acceso. (Fuente de la imagen: Avalanche Technology)

Durante una operación de programación, la orientación magnética de la capa de almacenamiento pasa eléctricamente de un estado paralelo (estado de baja resistencia "0") a un estado antiparalelo (estado de alta resistencia "1"), o viceversa, dependiendo de la dirección de la corriente a través del elemento p-MTJ. Estos dos estados de resistencia distintos se utilizan para el almacenamiento de datos y la detección.

Casos de uso de MRAM

El registro de datos, las memorias en los nodos de IoT, el aprendizaje de máquinas/inteligencia artificial en dispositivos de computación de punta y las etiquetas RFID en los hospitales son ejemplos de casos de uso de MRAM.

Los registradores de datos requieren múltiples megabits de memoria no volátil para acomodar la acumulación de datos a largo plazo. Normalmente funcionan con pilas, pero también pueden depender de la recolección de energía para su alimentación, y por lo tanto requieren una memoria de bajo consumo. En caso de pérdida de energía, los datos registrados deben conservarse indefinidamente. La MRAM cumple con las exigencias de rendimiento de los registradores de datos.

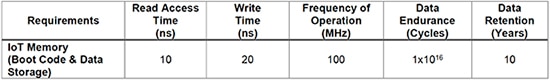

La persistencia de la MRAM, combinada con un modo de energía extremadamente bajo, está permitiendo una solución de memoria unificada para el código y los datos en los nodos de IoT que funcionan con cosechadores de energía o fuentes de baterías en factores de forma extremadamente pequeños (Figura 3). El tiempo de inicio es a menudo una consideración importante en los nodos IoT. La implementación de una estructura de código en el lugar utilizando MRAM puede reducir el tiempo requerido para el arranque, así como el costo total de la lista de materiales ya que hay menos necesidad de DRAM o SRAM.

Figura 3: La velocidad, resistencia y capacidad de retención de datos de la MRAM le ayudan a cumplir con los requisitos de memoria de los nodos de IoT. (Fuente de la imagen: Avalanche Technology)

Figura 3: La velocidad, resistencia y capacidad de retención de datos de la MRAM le ayudan a cumplir con los requisitos de memoria de los nodos de IoT. (Fuente de la imagen: Avalanche Technology)

La persistencia que ofrece la MRAM también está permitiendo una nueva generación de nodos de IoT capaces de realizar aprendizaje automático donde los algoritmos de inferencia no tienen que ser recargados cada vez después de que el dispositivo se activa. El procesamiento local incluye el análisis de los datos de los sensores, la toma de decisiones y, en algunos casos, incluso la reconfiguración del nodo. Esta inteligencia localizada exige una memoria persistente y de baja potencia. Estos dispositivos pueden implementar una inferencia local gruesa en tiempo real y pueden utilizar la nube para un análisis mejorado.

La velocidad de la MRAM es beneficiosa para implementar el aprendizaje de la máquina en dispositivos de vanguardia como los sistemas de planificación de recursos empresariales (ERP), los sistemas de ejecución de la fabricación (MES) y los sistemas de control de supervisión y adquisición de datos (SCADA). En estos sistemas se analizan los datos y se identifican los patrones intermedios y se comparten con los dominios adyacentes. La arquitectura del borde requiere velocidad de procesamiento y memoria persistente.

Los diseñadores también pueden aplicar la MRAM en dispositivos de salud donde la identificación por radiofrecuencia (RFID) puede ser beneficiosa. Su bajo consumo de energía, combinado con su inmunidad a la radiación, lo hace adecuado para entornos hospitalarios. Las etiquetas RFID en los hospitales se utilizan por una variedad de razones que incluyen la administración de inventarios, el cuidado y la seguridad de los pacientes, la identificación del equipo médico y la identificación y el control de los consumibles.

Memoria MRAM serial de alto rendimiento

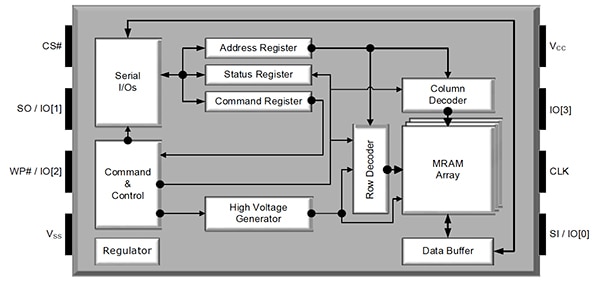

Los diseñadores de sistemas de computación de punta, incluyendo controles industriales y automatización, dispositivos médicos, prendas de vestir, sistemas de red, almacenamiento/RAID, automotriz y robótica pueden usar el M30082040054X0IWAY de Renesas (Figura 4). Está disponible en densidades que van de 4 Mbits a 16 Mbits. La tecnología MRAM de Renesas es análoga a la tecnología flash con tiempos de lectura/escritura compatibles con SRAM. Los datos son siempre no volátiles con una resistencia de1016 ciclos de escritura y una retención mayor de 20 años a 85°C.

El M30082040054X0IWAY tiene una Interfaz Periférica Serial (SPI), eliminando la necesidad de controladores de dispositivos de software. El SPI es una interfaz serial sincrónica que utiliza líneas separadas para los datos y el reloj para ayudar a mantener al anfitrión y al secundario en perfecta sincronización. El reloj le dice al receptor exactamente cuándo realizar una muestra de los bits en la línea de datos. Esto puede ser el aumento (de bajo a alto) o la disminución (de alto a bajo) o ambos bordes de la señal del reloj.

Figura 4: El M30082040054X0IWAY ofrece esquemas de protección de datos basados en hardware y software. La protección del hardware es a través del pin WP#. La protección del software está controlada por los bits de configuración en el registro de estado. Ambos esquemas inhiben la escritura en los registros y en la matriz de memoria. (Fuente de la imagen: Renesas)

Figura 4: El M30082040054X0IWAY ofrece esquemas de protección de datos basados en hardware y software. La protección del hardware es a través del pin WP#. La protección del software está controlada por los bits de configuración en el registro de estado. Ambos esquemas inhiben la escritura en los registros y en la matriz de memoria. (Fuente de la imagen: Renesas)

El M30082040054X0IWAY soporta eXecute-In-Place (XIP) que permite completar una serie de instrucciones de lectura y escritura sin tener que cargar individualmente el comando de lectura o escritura para cada instrucción. Así, el modo XIP ahorra la sobrecarga de los comandos y reduce el tiempo de acceso de lectura y escritura aleatoria.

El M30082040054X0IWAY ofrece esquemas de protección de datos basados en hardware y software. La protección del hardware es a través del pin WP#. La protección del software está controlada por los bits de configuración en el registro de estado. Ambos esquemas inhiben la escritura en los registros y en la matriz de memoria. Tiene una matriz de almacenamiento aumentado de 256 bytes que es independiente de la matriz de memoria principal. Es programable por el usuario y puede ser protegido contra escritura accidental.

Para satisfacer aún más las aplicaciones de baja potencia, el M30082040054X0IWAY tiene dos estados de potencia más bajos: Deep Power Down e Hibernación. Los datos no se pierden mientras el dispositivo está en cualquiera de estos dos estados de baja potencia. Además, el dispositivo mantiene todas sus configuraciones.

El dispositivo está disponible en paquetes DFN de 8 pines (WSON) y SOIC de 8 pines. Estos paquetes son compatibles con productos volátiles y no volátiles de baja potencia similares. Se ofrece con rangos de temperatura de funcionamiento industrial (-40 °C a 85 °C) e industrial plus (-40 °C a 105 °C).

Uso de la MRAM

La MRAM puede reducir significativamente el consumo de energía en general en comparación con otras tecnologías de memoria. Sin embargo, la cantidad de ahorro de energía puede variar dependiendo de los patrones de uso del diseño de la aplicación específica. Como otras memorias no volátiles, la corriente de escritura es mucho más alta que la corriente de lectura o de espera. Por consiguiente, es necesario reducir al mínimo el tiempo de escritura en las aplicaciones de potencia crítica, especialmente en los diseños que requieren escritura frecuente en la memoria. Los tiempos de escritura más cortos de MRAM pueden mitigar esta consideración y reducir el consumo de energía en comparación con otras opciones de memoria no volátil, como EEPROM o flash.

Un ahorro adicional de energía es posible con la MRAM usando una arquitectura de sistema de compuerta de energía y poniendo la memoria en espera lo más a menudo posible. La potencia más rápida de la MRAM para escribir el tiempo hace posible ponerla en espera más frecuentemente que otras memorias no volátiles. El cero de fugas de la MRAM cuando está en espera también es una ayuda aquí. Obsérvese que a menudo se necesita un capacitor de desacoplamiento más grande para apoyar las necesidades de energía cuando se emplea la compuerta de potencia.

Placa de evaluación de la MRAM

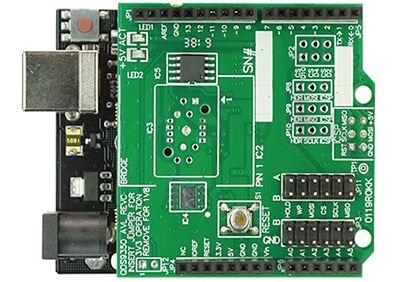

Para ayudar a los diseñadores a iniciarse en el M30082040054X0IWAY, Renesas proporciona el kit de evaluación M3016-EVK. Este contiene la MRAM de 16 Mbit y permite a los usuarios desarrollar soluciones interactivas de hardware usando la popular placa Arduino (Figura 5). El kit "plug-n-play" incluye una placa base Arduino y un software emulador de terminal que se comunica con la interfaz USB de la computadora. La palca de evaluación se monta en la parte superior de la placa anfitriona Arduino UNO a través de los cabezales de la UNO R3. Los programas de prueba proporcionados permiten a los usuarios evaluar rápidamente la funcionalidad del dispositivo MRAM.

Figura 5: El kit de evaluación M3016-EVK se monta encima de una placa anfitriona Arduino UNO para apoyar la rápida evaluación del rendimiento de la MRAM. (Fuente de la imagen: Renesas)

Figura 5: El kit de evaluación M3016-EVK se monta encima de una placa anfitriona Arduino UNO para apoyar la rápida evaluación del rendimiento de la MRAM. (Fuente de la imagen: Renesas)

Conclusión:

El diseño de dispositivos de computación de vanguardia que utilizan tecnologías de memoria convencionales, como DRAM, SRAM, flash y EEPROM, requiere una variedad de compensaciones que pueden limitar el rendimiento. Para la computación de punta, los diseñadores pueden recurrir a las recientemente introducidas MRAM que ofrecen un verdadero acceso aleatorio, permitiendo que tanto la lectura como la escritura ocurran de forma aleatoria en la memoria.

Como se muestra, la MRAM soporta las necesidades de memoria de los diseñadores de computadoras de punta, incluyendo: un dispositivo que debe almacenar y recuperar datos sin incurrir en grandes latencias; bajo consumo de energía debido a la ausencia de fugas cuando está en espera; y la capacidad de soportar1016 ciclos de escritura con una capacidad de retención de datos de más de 20 años a 85 °C.

Lecturas recomendadas

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.