Cómo utilizar los SoCs FPGA para sistemas en tiempo real seguros y conectados (Hard Real-Time Systems)

Colaboración de Editores de DigiKey de América del Norte

2023-02-16

Los arreglos programables de puertas en campo (FPGA), los subsistemas de unidades de microcontroladores (MCU) RISC-V compatibles con Linux, las arquitecturas de memoria avanzadas y las interfaces de comunicaciones de alto rendimiento son herramientas importantes para los diseñadores. Esto es especialmente cierto para los diseñadores de sistemas conectados seguros, sistemas críticos para la seguridad y un amplio rango de sistemas deterministas en tiempo real como la inteligencia artificial (IA) y el aprendizaje automático (AM).

Sin embargo, la integración de esos diversos elementos en un sistema seguro, conectado y determinista puede ser una actividad ardua y lenta, como lo es el trazado de las interconexiones de alta velocidad para los distintos elementos del sistema. Los diseñadores deben incluir una unidad de gestión de memoria, una unidad de protección de memoria, capacidad de arranque seguro y transceptores de clase gigabit para conectividad de alta velocidad. El diseño necesitará una gestión activa y estática de la potencia y un control de las corrientes de irrupción. Algunos diseños requerirán un funcionamiento en el rango de temperatura comercial ampliado de 0 °C a +100 °C de temperatura de unión (TJ), mientras que los sistemas en entornos industriales necesitarán funcionar con TJ de -40 °C a +100 °C.

Para hacer frente a estos y otros retos, los diseñadores pueden recurrir a dispositivos FPGA de sistema en chip (SoC) que combinan bajo consumo, eficiencia térmica y seguridad de grado de defensa para sistemas inteligentes, conectados y deterministas.

Este artículo repasa la arquitectura de un SoC FPGA de este tipo y cómo favorece el diseño eficiente de sistemas conectados y deterministas. A continuación, presenta brevemente la referencia EEMBC CoreMark-Pro de potencia de procesamiento frente a consumo de energía, junto con una visión del rendimiento de referencia de un SoC FPGA representativo. Analiza cómo se incorpora la seguridad a estos SoC FPGA y detalla SoC FPGA ejemplares de Microchip Technology, junto con una plataforma de desarrollo para acelerar el proceso de diseño. Concluye con una breve lista de placas de expansión de MikroElektronika que pueden utilizarse para implementar una serie de interfaces de comunicaciones, así como la capacidad de localización del sistema mundial de navegación por satélite (GNSS).

Arreglos de compuertas programables en campo (FPGA) o sistemas en chip (SoC) construidos con una estructura FPGA

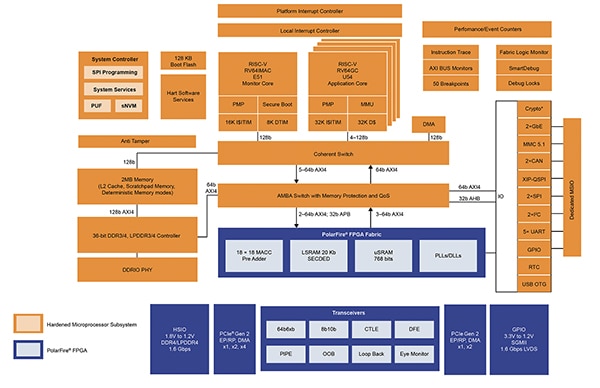

El "chip" de este SoC es una estructura FPGA que contiene los elementos del sistema, desde la FPGA hasta el subsistema MCU RISC-V construido con lógica FPGA reforzada. El subsistema MCU incluye un clúster MCU RISC-V de cuatro núcleos, un núcleo de monitor RISC-V, un controlador de sistema y un subsistema de memoria determinista de nivel 2 (L2). La FPGA de estos SoC incluye hasta 460 K de elementos lógicos, transceptores de hasta 12.7 gigabits por segundo (Gbps) y otros bloques de entrada/salida (I/O), como I/O de uso general (GPIO) y Peripheral Component Interconnect Express (PCIe) 2. La arquitectura general está diseñada para ser fiable. Incluye corrección de errores individuales y detección de errores dobles (Corrector de errores individuales-Detector de errores dobles) en todas las memorias, Análisis de potencia diferencial (DPA), protección de la memoria física y 128 kilobits (Kbits) de memoria Flash de arranque (Figura 1).

Figura 1: Todos los elementos de este SoC FPGA, incluidos los subsistemas RISC-V, se implementan en la estructura FPGA. (Fuente de la imagen: Microchip Technology)

Figura 1: Todos los elementos de este SoC FPGA, incluidos los subsistemas RISC-V, se implementan en la estructura FPGA. (Fuente de la imagen: Microchip Technology)

Microchip ofrece su ecosistema Mi-V (pronunciado "my five") de herramientas de terceros y recursos de diseño para apoyar la implantación de sistemas RISC-V. Está diseñado para acelerar la adopción de la arquitectura de conjuntos de instrucciones (ISA) RISC-V para núcleos RISC-V reforzados y para núcleos RISC-V blandos. Los elementos del ecosistema Mi-V incluyen acceso a:

- Licencias de propiedad intelectual (PI)

- Hardware

- Sistemas operativos y middleware

- Depuradores, compiladores y servicios de diseño

Las MCU RISC-V reforzadas del SoC FPGA incluyen varias funciones de depuración, como Interfaz eXtensible avanzada (AXI) configurable en tiempo de ejecución pasivo y rastreo de instrucciones. AXI permite a los diseñadores supervisar los datos que se escriben o leen en varias memorias y saber cuándo se escriben o leen.

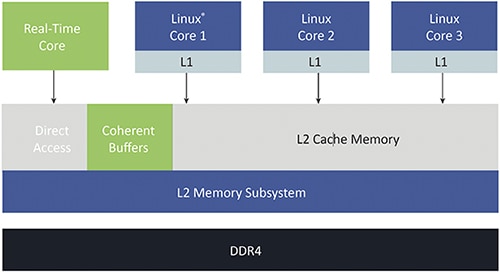

El subsistema MCU RISC-V utiliza un canal de un solo paso de cinco etapas, en orden. No es vulnerable a los exploits Spectre o Meltdown que pueden afectar a las arquitecturas fuera de orden. Las cinco MCU son coherentes con el subsistema de memoria y admiten una combinación de sistemas en tiempo real en modo de multiprocesamiento asimétrico determinista (AMP) y Linux. Las capacidades del subsistema RISC-V incluyen (Figura 2):

- Ejecutar operaciones Linux y hard en tiempo real

- Configurar L1 y L2 como memoria determinista

- Subsistema de memoria DDR4

- Desactivar/activar los predictores de bifurcación

- Operación de tuberías bajo pedido

Figura 2: El subsistema RISC-V incluye varios elementos de procesador y memoria. (Fuente de la imagen: Microchip Technology)

Figura 2: El subsistema RISC-V incluye varios elementos de procesador y memoria. (Fuente de la imagen: Microchip Technology)

Más procesamiento con menos energía

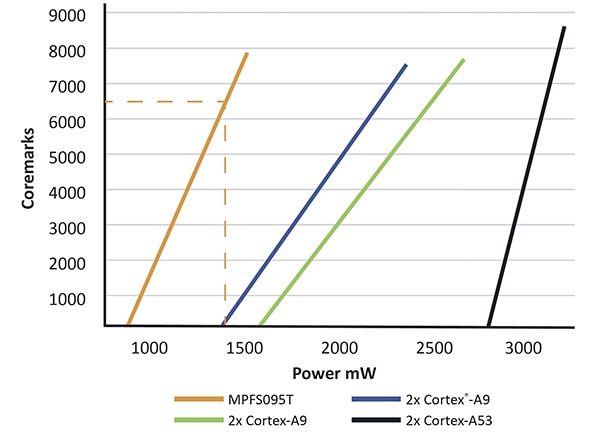

Además de sus ventajas de funcionamiento del sistema, incluido el soporte de procesamiento en tiempo real, estos SoCs FPGA son muy eficientes desde el punto de vista energético. La referencia CoreMark-PRO de EEMBC es un estándar del sector para comparar la eficiencia y el rendimiento de las MCU en sistemas embebidos. Se diseñó específicamente para evaluar el rendimiento del hardware y sustituir a la referencia Dhrystone.

Las cargas de trabajo de CoreMark-PRO incluyen una diversidad de características de rendimiento, paralelismo a nivel de instrucción y utilización de memoria basadas en cuatro cargas de trabajo de coma flotante y cinco cargas de trabajo de enteros comunes. Las cargas de trabajo en coma flotante incluyen una rutina de álgebra lineal derivada de LINPACK, una transformada rápida de Fourier, un algoritmo de red neuronal para la evaluación de patrones y una versión mejorada de la referencia Livermore loops. La compresión JPEG, un analizador XML, la compresión ZIP y un algoritmo hash seguro de 256 bits (SHA-256) constituyen la base de las cargas de trabajo enteras.

Los modelos MPFSO95T de estas FPGA SoC, como la MPFS095TL-FCSG536E, pueden proporcionar hasta 6.500 Coremarks a 1.3 Vatios (Figura 3).

Figura 3: El arreglo programable de puertas en campo (FPGA) o arreglos de compuertas programables en campo (SoC) MPFS095T (línea naranja) proporciona 6500 Coremarks a 1.3 vatios. (Fuente de la imagen: Microchip Technology)

Figura 3: El arreglo programable de puertas en campo (FPGA) o arreglos de compuertas programables en campo (SoC) MPFS095T (línea naranja) proporciona 6500 Coremarks a 1.3 vatios. (Fuente de la imagen: Microchip Technology)

Consideraciones de seguridad

Las aplicaciones críticas para la seguridad y en tiempo real para estos SoCs FPGA requieren una fuerte seguridad, además de una alta eficiencia energética y potentes capacidades de procesamiento. Las funciones de seguridad básicas de estos SoCs FPGA incluyen análisis de potencia diferencial (DPA), programación de secuencias de bits resistentes, un generador de números aleatorios reales (TRNG) y una función físicamente no clonable (PUF). También incluyen arranque seguro estándar y definido por el usuario, protección de la memoria física que proporciona restricciones de acceso a la memoria relacionadas con el estado de privilegios de la máquina, incluidos los modos máquina, supervisor o usuario, e inmunidad frente a los ataques Meltdown y Spectre.

La seguridad comienza con la gestión segura de la cadena de suministro, incluido el uso de módulos de seguridad de hardware (HSM) durante las pruebas y el empaquetado de las obleas. El uso de un certificado FPGA de 768 bytes firmado digitalmente x.509 integrado en cada sistema en chip (SoC) FPGA contribuye a garantizar la cadena de suministro.

En estos SoCs FPGA se incluyen numerosos detectores de manipulación en chip para garantizar un funcionamiento seguro y fiable. Si se detecta una manipulación, se emite un indicador de manipulación que permite al sistema responder según sea necesario. Algunos de los detectores de manipulación disponibles son:

- Monitores de voltaje

- Sensores de temperatura

- Detectores de fallos y frecuencias de reloj

- Detector activo JTAG

- Detector activo de malla

La seguridad se garantiza además con contramedidas de ataque de correlación de potencia (Garantía de posición del conector) de cifrado por bloques simétrico con Estándar de encriptación avanzada (AES-256) de 256 bits, funciones integradas de compendio criptográfico para garantizar la integridad de los datos, PUF integrado para el almacenamiento de claves y funciones de puesta a cero para la estructura FPGA y todas las memorias en chip.

Ejemplos de SoC FPGA

Microchip Technology combina estas capacidades y tecnologías en sus SoCs FPGA PolarFire con múltiples grados de velocidad, índices de temperatura y varios tamaños de encapsulado para satisfacer las necesidades de los diseñadores de una amplia gama de soluciones con elementos lógicos de entre 25 K y 460 K. Hay cuatro grados de temperatura disponibles (todos con clasificación TJ), de 0 °C a +100 °C en el rango comercial ampliado, de -40 °C a +100 °C en el rango industrial, de -40 °C a +125 °C en el rango de automoción y de -55 °C a +125 °C en el rango militar.

Los diseñadores pueden elegir entre dispositivos de velocidad estándar o dispositivos de velocidad -1, un 15% más rápidos. Estos SoCs FPGA pueden funcionar a 1.0 voltios para un menor consumo, o a 1.05 voltios para un mayor rendimiento. Están disponibles en distintos tamaños de envase, como 11 x 11 milímetros (mm), 16 x 16 mm y 19 x 19 mm.

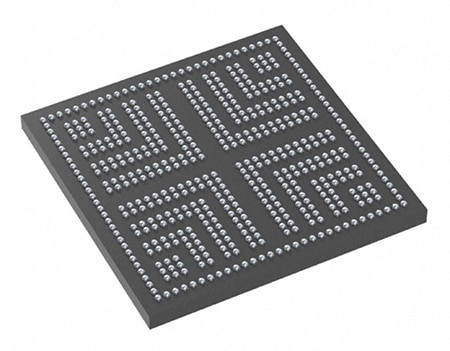

Para aplicaciones que necesitan un funcionamiento a temperatura comercial ampliada, funcionamiento a velocidad estándar y elementos lógicos de 254 K en un encapsulado de 19 x 19 mm, los diseñadores pueden utilizar el MPFS250T-FCVG484EES. Para soluciones más sencillas que necesiten elementos lógicos de 23 K, los diseñadores pueden recurrir al MPFS025T-FCVG484E, también con funcionamiento a temperatura comercial ampliada y grado de velocidad estándar en un encapsulado de 19 x 19 mm. El MPFS250T-1FCSG536T2 con 254 K elementos lógicos está diseñado para sistemas de automoción de alto rendimiento y tiene un rango de temperatura de funcionamiento de -40 a 125 °C y un grado de velocidad -1 para un reloj un 15% más rápido, en un encapsulado compacto de 16 x 16 mm con 536 bolas en un paso de 0.5 mm (Figura 4).

Figura 4: El MPFS250T-1FCSG536T2 de temperatura de automoción se presenta en un encapsulado de 16 x 16 mm con un recuento de 536 bolas y un paso de 0.5 mm. (Fuente de la imagen: Microchip Technology)

Figura 4: El MPFS250T-1FCSG536T2 de temperatura de automoción se presenta en un encapsulado de 16 x 16 mm con un recuento de 536 bolas y un paso de 0.5 mm. (Fuente de la imagen: Microchip Technology)

Plataforma de desarrollo del SoC FPGA

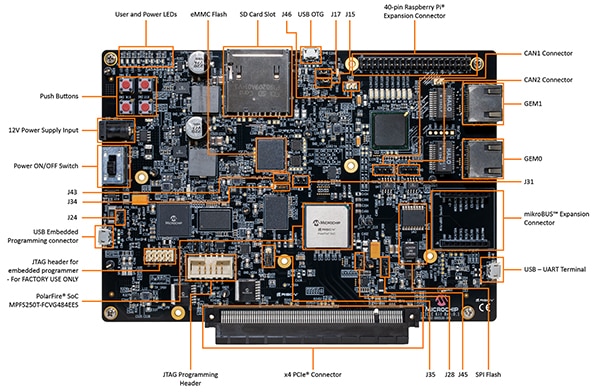

Para acelerar el diseño de sistemas con el SoC PolarFire FPGA, Microchip ofrece el kit PolarFire SoC Icicle MPFS-ICICLE-KIT-ES, que permite explorar el subsistema de microprocesador RISC-V de cinco núcleos compatible con Linux y con ejecución en tiempo real de bajo consumo. El kit incluye una licencia gratuita de Libero Silver, necesaria para evaluar los diseños. Características de programación y depuración en un solo lenguaje.

Estos SoC FPGA son compatibles con el kit de desarrollo de software (SDK) del acelerador VectorBlox, que permite aplicaciones AI/ML de bajo consumo y factor de forma pequeño. Se hace hincapié en simplificar el proceso de diseño hasta el punto de que los diseñadores no necesitan tener experiencia previa en el diseño de FPGA. El SDK del acelerador VectorBlox permite a los desarrolladores programar redes neuronales de bajo consumo mediante C/C++. El kit Icicle cuenta con numerosas características para proporcionar un entorno de desarrollo completo, incluido un sistema de sensores de potencia multirraíl para supervisar los distintos dominios de potencia, un puerto raíz PCIe y memorias integradas -incluidas LPDDR4, QSPI y eMMC Flash- para ejecutar Linux y Raspberry Pi, y puertos de expansión mikroBUS para una gran cantidad de opciones de conectividad por cable e inalámbrica, además de extensiones funcionales como la capacidad de localización GNSS (Figura 5).

Figura 5: Este completo entorno de desarrollo SoC FPGA incluye conectores para placas de expansión Raspberry Pi (arriba a la derecha) y mikroBUS (abajo a la derecha). (Fuente de la imagen: Microchip Technology)

Figura 5: Este completo entorno de desarrollo SoC FPGA incluye conectores para placas de expansión Raspberry Pi (arriba a la derecha) y mikroBUS (abajo a la derecha). (Fuente de la imagen: Microchip Technology)

Placas de expansión

Algunos ejemplos de placas de expansión mikroBUS son:

MIKROE-986, para añadir conectividad de bus CAN mediante una Interfaz periférica serial (SPI).

MIKROE-1582, para la interconexión entre la unidad de microcontrolador y un bus RS-232.

MIKROE-989, para conectar con un bus de comunicación RS422/485.

MIKROE-3144, compatible con las tecnologías LTE Cat M1 y NB1, permite una conectividad fiable y sencilla con dispositivos IoT 3GPP.

MIKROE-2670, permite la funcionalidad GNSS con recepción simultánea de las constelaciones GPS y Galileo más BeiDou o GLONASS, lo que da como resultado una alta precisión de posición en situaciones con señales débiles o interferencias en cañones urbanos.

Conclusión:

Los diseñadores pueden recurrir a los SoC FPGA cuando desarrollen sistemas conectados, críticos para la seguridad y deterministas en tiempo real. Los SoC FPGA ofrecen un amplio rango de elementos de sistema, entre los que se incluyen una estructura FPGA, un subsistema MCU RISC-V con memorias de alto rendimiento, interfaces de comunicación de alta velocidad y numerosas funciones de seguridad. Para ayudar a los diseñadores a empezar, existen placas de desarrollo y entornos que incluyen todos los elementos necesarios, incluidas placas de expansión que pueden utilizarse para implementar un amplio rango de funciones de comunicaciones y localización.

Lecturas recomendadas

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.