Cómo equilibrar eficazmente la latencia, el ancho de banda y el rendimiento de las soluciones de prueba y medición

Colaboración de Editores de DigiKey de América del Norte

2022-11-16

Los diseñadores de soluciones de prueba y medición, como los bancos de pruebas de automoción y los subsistemas de hardware-in-the-loop (HIL), se enfrentan cada vez más al reto de encontrar el equilibrio óptimo entre un alto rendimiento con una menor latencia y un mayor ancho de banda. Al mismo tiempo, necesitan flexibilidad y capacidad de reconfiguración para soportar los rápidos cambios en los requisitos del sistema y dar servicio a una amplia gama de casos de uso.

Tradicionalmente, el cumplimiento de estos requisitos -manteniendo la precisión del rendimiento de CA y CC a medida que aumentan las frecuencias de muestreo- requiere un tiempo y un esfuerzo de diseño/depuración considerables. Este esfuerzo aumenta con cualquier rediseño cuando se cambian los componentes para adaptarse a los cambios en los objetivos del banco de pruebas y de la instrumentación.

Una alternativa mejor es un enfoque de plataforma basado en dispositivos programables, reconfigurables y reutilizables. Estas piezas "ancla" establecen una línea de base de rendimiento que puede utilizarse -y reutilizarse- en variaciones de un mismo tipo de aplicación o incluso en múltiples aplicaciones dispares.

Este artículo presenta el convertidor de digital a analógico (DAC) AD3552R de Analog Devices como ejemplo de cómo los componentes programables pueden cumplir los objetivos de los diseñadores para crear una plataforma de cadena de señales escalable, fácilmente optimizada y reconfigurable. Se comentan las placas de evaluación y el soporte de LTspice para ayudar a los diseñadores a empezar. También se presenta el convertidores de analógico a digital (ADC) ADAQ23878 altamente integrado que, junto con el AD3552R, puede formar dos piezas de anclaje críticas y complementarias para un enfoque basado en la plataforma.

La integración y la programabilidad simplifican los diseños.

A medida que cambian los requisitos de los sistemas de pruebas, las técnicas tradicionales y a menudo exitosas que se han utilizado para maximizar la precisión y minimizar el error, aunque con un costo añadido de diseño y componentes, son:

- Elegir componentes "mejores", como resistencias con una tolerancia más ajustada o un coeficiente de temperatura más bajo, para minimizar las insuficiencias tanto en el rendimiento inicial como en el tiempo y la temperatura.

- Utilizar topologías que admitan en gran medida la autocancelación de errores inevitables, como las resistencias/resistores emparejados y los circuitos diferenciales o el clásico puente de Wheatstone.

- Proporcionar una calibración inicial y continua mediante el uso de un componente "de oro", como una referencia de voltaje de precisión con la que se pueden comparar todos los demás voltajes clave.

El éxito de estas técnicas se convierte en un reto para los diseñadores de sistemas de prueba cuando la aplicación requiere altas tasas de actualización para el ADC y el DAC.

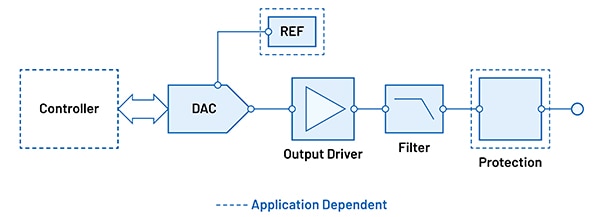

Para eliminar muchos de estos retos, un enfoque programable y basado en plataformas ofrece una mejor opción al minimizar -o incluso eliminar- la necesidad de diseñar "desde cero" para el proyecto inicial y a medida que cambian los requisitos. El enfoque también garantiza un medio coherente para evaluar y simular un diseño. Un elemento fundamental de este enfoque programable es el DAC (Figura 1).

Figura 1: El DAC es una función clave en las aplicaciones de prueba e instrumentación; sus capacidades se someten a un estrecho escrutinio a medida que los requisitos de los sistemas de prueba se vuelven más exigentes. (Fuente de la imagen: Analog Devices).

Figura 1: El DAC es una función clave en las aplicaciones de prueba e instrumentación; sus capacidades se someten a un estrecho escrutinio a medida que los requisitos de los sistemas de prueba se vuelven más exigentes. (Fuente de la imagen: Analog Devices).

El rendimiento y las capacidades de los DAC están siendo cada vez más "estresados" por las aplicaciones de prueba y control que exigen tanto precisión como alta velocidad en una amplia gama. También exigen flexibilidad y necesitan ser fácilmente reconfigurados sin tener que pasar por un completo y complicado ciclo de rediseño y recalificación.

El AD3552R de ADI puede abordar los objetivos de rendimiento, ya que es un DAC SPI de 16 bits, 33 millones de actualizaciones por segundo (MUPS), de varios tramos y doble salida (Figura 2). Además de los atributos básicos de rendimiento, otra ventaja del AD3552R es la facilidad con la que se puede reconfigurar para cumplir con los objetivos nuevos o cambiantes del proyecto. Esta reconfigurabilidad incluye la garantía de que cumplirá esos objetivos con un alto nivel de confianza, en lugar de aportar nuevas e indeseadas "sorpresas".

Figura 2: El AD3552R es un DAC SPI de 16 bits, 33 MUPS, con múltiples salidas y que puede reconfigurarse fácilmente para obtener diferentes atributos de rendimiento. (Fuente de la imagen: Analog Devices)

Figura 2: El AD3552R es un DAC SPI de 16 bits, 33 MUPS, con múltiples salidas y que puede reconfigurarse fácilmente para obtener diferentes atributos de rendimiento. (Fuente de la imagen: Analog Devices)

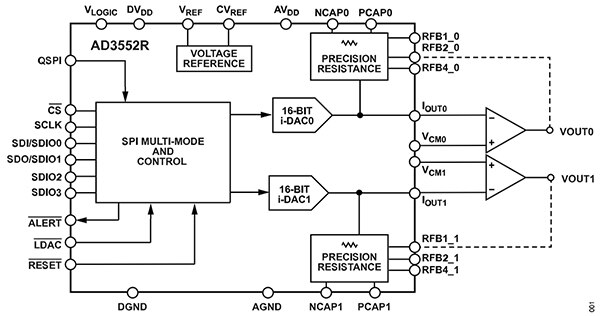

El AD3552R está disponible en un encapsulado LFCSP de 5 milímetros (mm) × 5 mm y funciona con una referencia fija de 2.5 voltios, pero puede configurarse mediante software para múltiples rangos de salida de voltaje. También permite un equilibrio óptimo de rendimiento, precisión, velocidad y flexibilidad.

El dispositivo incorpora tres resistencias de retroalimentación con compensación de deriva para apoyar el amplificador de transimpedancia externo (TIA) que escala la tensión de salida. Los registros de escala de offset y ganancia permiten generar múltiples rangos de salida, como 0 a 2.5 voltios, 0 a 5 voltios, 0 a 10 voltios, -5 a +5 voltios y -10 a +10 voltios, así como rangos intermedios personalizados con una resolución completa de 16 bits.

Además, para resolver el conocido dilema "velocidad frente a precisión", el DAC AD3552R puede funcionar en modo rápido para obtener la máxima velocidad y el tiempo de establecimiento más rápido, o en modo de precisión para obtener la mayor precisión y la máxima exactitud. En el modo rápido, los datos del DAC se cargan como una palabra de 16 bits, lo que resulta en una velocidad de actualización de un solo canal de 33 MUPS. En cambio, en el modo de precisión, los datos se escriben en 24 bits, lo que da lugar a una velocidad de actualización de un solo canal de 22 MUPS.

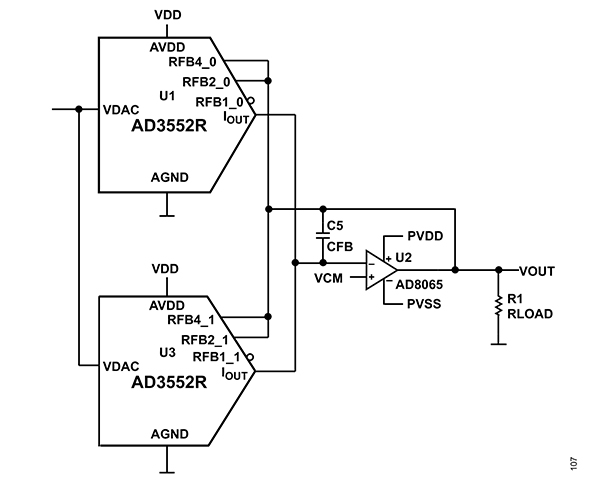

Para aquellas aplicaciones que requieren una menor densidad de ruido junto con un tiempo de asentamiento más rápido, y que pueden aceptar un mayor consumo de energía, el AD3552R admite la combinación de los dos canales DAC para producir una única salida (Figura 3). Ambos DAC deben ser actualizados simultáneamente con el mismo código para obtener la misma salida de voltaje obtenida usando un solo DAC; el AD3552R proporciona varias formas eficientes de hacerlo.

Figura 3: Las dos salidas del AD3552R pueden combinarse para obtener una menor densidad de ruido junto con un tiempo de estabilización más rápido. (Fuente de la imagen: Analog Devices).

Figura 3: Las dos salidas del AD3552R pueden combinarse para obtener una menor densidad de ruido junto con un tiempo de estabilización más rápido. (Fuente de la imagen: Analog Devices).

También hay flexibilidad en la interfaz SPI del dispositivo, ya que puede configurarse en los modos SPI simple (SPI clásico), SPI doble, SPI doble síncrono y SPI cuádruple, con funcionamiento a velocidad de datos simple (SDR) o doble (DDR), y con niveles lógicos de 1.2 a 1.8 voltios. Además, como la integridad de los datos es también una preocupación constante y creciente, el dispositivo puede estar habilitado para incorporar una comprobación de redundancia cíclica (CRC). También se han integrado múltiples verificadores de errores para detectar fallos de VREF o corrupción del mapa de memoria.

Los modelos de simulación agilizan la configuración e infunden confianza

Aunque el AD3552R es un dispositivo de precisión de banda ancha, siempre habrá compensaciones entre sus numerosos parámetros programables por el usuario. Para acelerar la comprensión del impacto de estas opciones de diseño y ayudar a los diseñadores a empezar, cuenta con el apoyo de placas de evaluación, así como de LTspice para evaluar el ruido, el análisis transitorio, la simulación de CA y otros parámetros. Esto simplifica la optimización de la latencia y el rendimiento, por lo que los diseñadores no tienen que establecer los valores de los parámetros o hacer concesiones sin datos creíbles.

La posibilidad de utilizar LTspice en la cadena de señales reúne todos sus elementos para que los usuarios puedan comprender claramente el rendimiento completo de la cadena de señales. Esto es especialmente importante ya que el AD3552R ofrece:

- Diez rangos de corriente; resultantes de la combinación de valores de escala de ganancia configurados digitalmente.

- Tres valores de ganancia de transimpedancia; resultantes de la conexión de una de las resistencias de retroalimentación.

- Un total de 511 valores de compensación de CC configurados digitalmente.

Esto supone un total de 15.330 combinaciones, claramente más allá del alcance de cualquier enfoque "práctico" de breadboarding o incluso de una evaluación manual selectiva.

El modelo LTspice para el AD3552R actualiza los modelos tradicionales de DAC centrados en la salida analógica con una simulación más centrada en lo digital. La funcionalidad de algunos registros del modelo -en particular los relacionados con el escalado de la ganancia digital y el desplazamiento de CC- puede simularse, y el modelo también es capaz de reproducir el rendimiento dinámico y de ruido con gran fidelidad. Entre las características de rendimiento del AD3552R que simula el software LTspice se encuentran:

- Simulación del rango de salida: La simulación de barrido de CC es útil para confirmar el rango de la tensión de salida para una determinada configuración de parámetros. También tiene en cuenta las limitaciones impuestas por el margen de sobrecarga del amplificador operacional (parte superior del rango) y el margen de pie (parte inferior), lo que facilita la anticipación de cualquier saturación de la señal de salida.

- Ajuste de la respuesta escalonada: La simulación de transitorios con una forma de onda escalonada es útil para ajustar el valor del condensador de realimentación y el filtro de salida de la TIA para conseguir el tiempo de subida, el tiempo de asentamiento y la sobrecresta deseados, y puede combinarse con un barrido paramétrico para encontrar los valores óptimos de las piezas. La simulación también tiene en cuenta la capacidad de accionamiento del amplificador y el DAC para estimar la velocidad de respuesta y el tiempo de subida de la señal. (Tenga en cuenta que este valor es un punto de partida porque el circuito de simulación no incluye los efectos parásitos de la placa y los paquetes de las piezas).

- Simulación del ancho de banda de CA: La simulación de barrido de CA es útil para ajustar los valores del condensador de realimentación y del filtro de salida de la TIA en aplicaciones en las que la señal de salida es armónica.

- Simulación de la Densidad de ruido: Permite predecir la densidad de ruido a la salida del DAC y del TIA, tanto en la región de 1/f como en la de ruido térmico. El modelo LTspice del AD3552R captura la variación de la densidad de ruido con el código, y también tiene en cuenta la ganancia de la TIA, que escala el ruido a la salida del DAC actual.

Para más información sobre LTspice, véase "Cómo utilizar LTspice para determinar el rendimiento del ruido de la fotodetección durante el diseño de instrumentos sensibles".

Practica, prueba, con hardware real

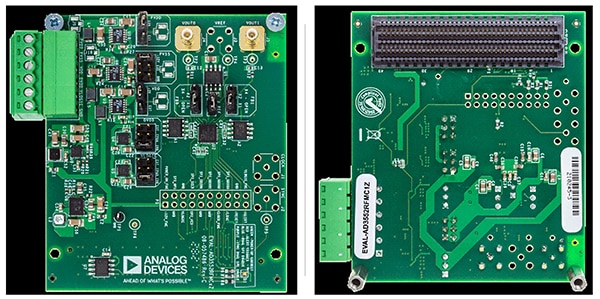

Las simulaciones son muy útiles y necesarias, pero, como sabe cualquier ingeniero experimentado, no pueden sustituir totalmente a una evaluación en el mundo real, especialmente cuando factores como las parásitas externas al dispositivo pueden afectar al rendimiento. En el caso del AD3552R, esta necesidad se satisface con el EVAL-AD3552RFMCxZ, que está disponible en dos variantes: el EVAL-AD3552RFMC1Z para mayor velocidad, y el EVAL-AD3552RFMC2Z para mayor precisión (Figura 4).

Figura 4: El EVAL-AD3552RFMCxZ (izquierda: capa superior; derecha: capa inferior) se presenta en dos versiones similares, una optimizada para la velocidad y otra para la precisión. (Fuente de la imagen: Analog Devices).

Figura 4: El EVAL-AD3552RFMCxZ (izquierda: capa superior; derecha: capa inferior) se presenta en dos versiones similares, una optimizada para la velocidad y otra para la precisión. (Fuente de la imagen: Analog Devices).

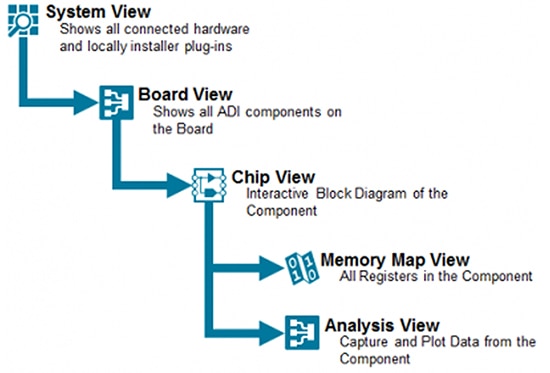

El software de la placa utiliza el paquete "Analysis, Control, Evaluation" (ACE) de ADI, una aplicación de escritorio que permite evaluar y controlar múltiples sistemas de evaluación de toda la cartera de productos de ADI. La aplicación consta de un marco común y de complementos individuales específicos para cada componente.

Para el AD3552R, ACE tiene varias vistas para controlar diferentes aspectos del DAC. Cuando se abre una vista por primera vez, se crea una nueva lengüeta en la parte superior de la ventana principal. La clavija de conexión del AD3552R produce una jerarquía de vistas: Vista de placa, una vista de chip, una vista de mapa de memoria y una vista de análisis que combina una vista de generador de formas de onda y una vista de generador de vectores (Figura 5).

Figura 5: La clavija de conexión ACE para el AD3552R produce una jerarquía de vistas desde una vista de sistema de alto nivel hasta una vista de análisis de nivel básico. (Fuente de la imagen: Analog Devices).

Figura 5: La clavija de conexión ACE para el AD3552R produce una jerarquía de vistas desde una vista de sistema de alto nivel hasta una vista de análisis de nivel básico. (Fuente de la imagen: Analog Devices).

- La vista de placa muestra un diagrama simplificado de la placa de evaluación, incluyendo algunos conectores relevantes y la interconexión entre los chips.

- La vista de chip muestra un diagrama interno simplificado del chip que muestra la lógica de la interfaz, los núcleos DAC, las resistencias de retroalimentación de precisión y los pines relevantes para esos bloques.

- La vista del mapa de memoria muestra todo el espacio de configuración del AD3552R; este espacio puede mostrarse como una lista de registros o como una lista de campos de bits.

- La vista del generador de formas de onda permite asignar vectores a los canales e iniciar o detener la generación de formas de onda.

- La vista del generador de vectores permite definir o cargar formas de onda que posteriormente pueden asignarse a los canales DAC.

Utilizando la placa de evaluación y el software ACE, los usuarios del AD3552R pueden confirmar las decisiones que tomaron a través del simulador LTspice y ajustarlas según sea necesario. Los usuarios también pueden ejercitar el dispositivo con sus numerosos registros y funciones y características programables.

Explore otras opciones de adquisición de datos

Las opciones de componentes altamente programables que pueden utilizarse para crear plataformas de cadena de señales escalables, fácilmente optimizadas y reconfigurables no se limitan a dispositivos como el AD3552R.

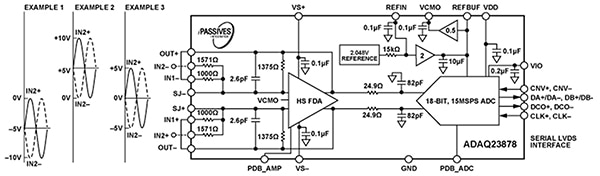

Por ejemplo, el ADAQ23878 de Analog Devices es un ADC µModule de 18 bits y 15 MSPS con pin/clavija. Esta solución de adquisición de datos de alta velocidad simplifica y acelera el ciclo de desarrollo de los sistemas de medición de precisión al eliminar gran parte de la carga de diseño de la selección, optimización y disposición de los componentes mediante el uso de un dispositivo disponible en el mercado.

Gracias a la tecnología de sistema en paquete (SIP), el ADAQ23878 reduce el número de componentes del sistema final combinando múltiples bloques de procesamiento y acondicionamiento de señales comunes en un único dispositivo. Incluye un amplificador controlador de búfer de bajo ruido y totalmente diferencial, un búfer de referencia estable y un ADC de alta velocidad de 18 bits y 15 MSPS de registro de aproximaciones sucesivas (SAR) (Figura 6).

Figura 6: El ADAQ23878 combina bloques de procesamiento y acondicionamiento de señales en un solo dispositivo, lo que minimiza la necesidad de componentes externos. (Fuente de la imagen: Analog Devices)

Figura 6: El ADAQ23878 combina bloques de procesamiento y acondicionamiento de señales en un solo dispositivo, lo que minimiza la necesidad de componentes externos. (Fuente de la imagen: Analog Devices)

El ADAQ23878 también incorpora los componentes pasivos críticos con características superiores de adaptación y deriva que provienen del uso de la tecnología iPassive de ADI, que minimiza las fuentes de error dependientes de la temperatura para un rendimiento óptimo. El pequeño espacio de tan sólo 9 mm × 9 mm, con un paso de 0.8 mm y un encapsulado CSP BGA de 100 bolas, permite utilizar instrumentos de factor de forma más pequeño sin sacrificar el rendimiento (Figura 7).

Figura 7: La tecnología SIP del ADAQ23878 incorpora componentes activos y pasivos en un único dispositivo de fácil aplicación y permite minimizar las fuentes de error relacionadas con la deriva. (Fuente de la imagen: Analog Devices).

Figura 7: La tecnología SIP del ADAQ23878 incorpora componentes activos y pasivos en un único dispositivo de fácil aplicación y permite minimizar las fuentes de error relacionadas con la deriva. (Fuente de la imagen: Analog Devices).

La integración del sistema resuelve muchos problemas de diseño, mientras que el dispositivo sigue ofreciendo la flexibilidad de un bucle de retroalimentación ADC-controlador configurable para permitir ajustes de ganancia o atenuación, así como una entrada totalmente diferencial o de un solo extremo a otro.

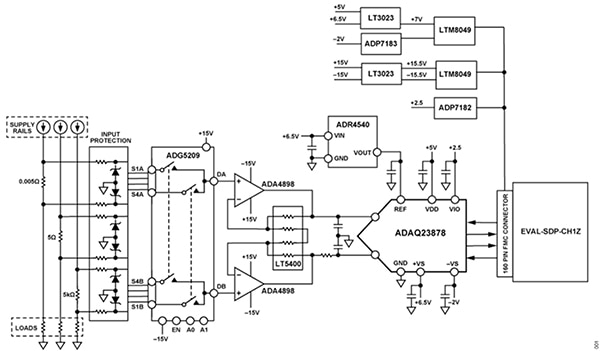

Por ejemplo, puede ser el núcleo de un citómetro de flujo completo (véase "Implementación rápida de diseños de citómetros de flujo utilizando módulos de adquisición de datos de alta precisión"), o un sistema de medición de corriente de amplio rango con precisión, ancho de banda y rendimiento de deriva comparables a los equipos de prueba de banco y de montaje en bastidor para un entorno de prueba de producción (Figura 8). Al mismo tiempo, la solución es lo suficientemente pequeña como para incorporarse a aplicaciones que necesitan ser supervisadas continuamente.

Figura 8: Con los componentes de apoyo activos y pasivos apropiados para la aplicación, el ADAQ23878 funciona como el núcleo de un sistema de adquisición de datos que proporciona una medición precisa de la corriente en un amplio rango dinámico. (Fuente de la imagen: Analog Devices)

Figura 8: Con los componentes de apoyo activos y pasivos apropiados para la aplicación, el ADAQ23878 funciona como el núcleo de un sistema de adquisición de datos que proporciona una medición precisa de la corriente en un amplio rango dinámico. (Fuente de la imagen: Analog Devices)

El diseño presenta una medición de alta precisión de tres rangos de corriente utilizando una combinación de resistencias/resistencias en derivación, amplificadores incorporados y el módulo ADAQ23878 μModule. Esta solución aumenta el número de canales por placa a pesar de las limitaciones de tamaño, al tiempo que mitiga los problemas térmicos, alivia la carga de calibración del sistema debido al autocalentamiento y optimiza el rendimiento general de la precisión. El diseño de la placa utiliza resistencias de derivación de cuatro terminales con una conexión Kelvin incorporada que reduce los efectos del coeficiente de temperatura de resistencia (TCR), ofreciendo una estabilidad de temperatura mejorada en comparación con las resistencias de derivación de dos terminales (Figura 9).

Figura 9: El sistema completo de medición de corriente basado en el ADAQ23878 μModule es más pequeño que los conectores necesarios. (Fuente de la imagen: Analog Devices).

Figura 9: El sistema completo de medición de corriente basado en el ADAQ23878 μModule es más pequeño que los conectores necesarios. (Fuente de la imagen: Analog Devices).

Conclusión:

Los diseñadores de equipos de prueba y medición requieren precisión, rendimiento y flexibilidad, además de poder reconfigurar fácilmente el diseño básico para dar servicio a una amplia gama de casos de uso. Como se ha mostrado, componentes como el DAC AD3552R presentan muchos parámetros programables, lo que permite adaptarlos rápida y fácilmente según las necesidades. Junto con el ADC ADAQ23878 y con el apoyo de herramientas como LTspice y las placas de evaluación y el software, el AD35525 desempeña un papel clave en un enfoque basado en la plataforma para el diseño de sistemas de prueba que proporciona la flexibilidad y el rendimiento necesarios, al tiempo que minimiza el tiempo requerido para la reconfiguración.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.