Cómo evaluar y usar los búferes de reloj con retardo cero para proteger la temporización en sistemas digitales síncronos

Colaboración de Editores de DigiKey de América del Norte

2019-07-18

A medida que los sistemas digitales aumentan su rendimiento, los diseñadores deben prestar una atención cada vez más minuciosa al diseño de los circuitos de generación y distribución de reloj para evitar diferencias o incertidumbres en el tiempo de distribución del reloj. Dichos problemas pueden deteriorar el rendimiento del sistema, reducir los márgenes de tiempo o causar errores de funcionamiento. Para evitar problemas relacionados con el sesgo de tiempo, los diseñadores pueden usar búferes de reloj con retardo cero.

Los típicos sistemas digitales síncronos utilizan un reloj común para mantener las operaciones en secuencia. Este reloj debe distribuirse a todos los elementos secuenciales para mantener el funcionamiento del sistema a la velocidad deseada, a menudo, mediante el uso del control de bucle cerrado para reducir el sesgo de tiempo. Los búferes de reloj con retardo cero utilizan circuitos de sincronización de fase (PLL) para garantizar que las salidas del reloj con búfer estén alineadas con la entrada del reloj de referencia, lo que asegura una sincronización del reloj casi perfecta.

En este artículo se describirán los búferes de reloj con retardo cero, se explicará cómo funcionan mediante el uso de soluciones de muestra de Cypress Semiconductor, Integrated Device Technology Inc. (IDT) y de ON Semiconductor y se detallará cómo puede controlarse el sesgo de reloj. También se investigarán los métodos de prueba para asegurar la estabilidad de estos dispositivos.

Sesgo de reloj

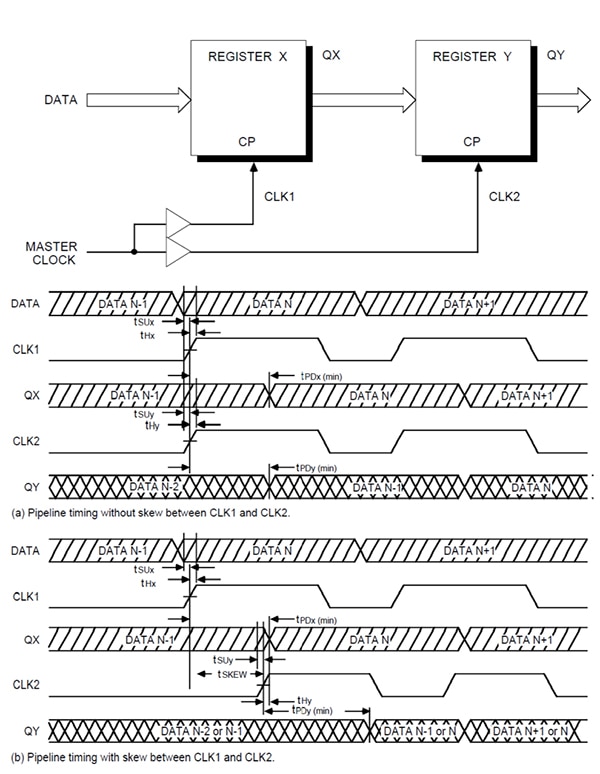

En los sistemas digitales síncronos, los relojes pueden llegar en diferentes momentos a distintas partes del circuito, lo que provoca un sesgo de reloj. El sesgo de reloj puede reducir los márgenes de tiempo y hacer que el sistema falle (Figura 1).

Figura 1: Un ejemplo simple de cómo el sesgo de reloj puede afectar las operaciones de un registro segmentado. Un reloj sesgado puede violar los requisitos de configuración o retención, lo que provoca un estado de salida indeterminado. (Fuente de la imagen: IDT)

Figura 1: Un ejemplo simple de cómo el sesgo de reloj puede afectar las operaciones de un registro segmentado. Un reloj sesgado puede violar los requisitos de configuración o retención, lo que provoca un estado de salida indeterminado. (Fuente de la imagen: IDT)

Considere un sistema síncrono simple que consta de dos registros. Los datos se canalizan a través de los registros de modo que la salida del registro X, QX, sea la entrada al registro Y. Los relojes se distribuyen a los registros a través de búferes independientes y se los designa CLK1 y CLK2. Si no hay sesgo entre los relojes como se muestra en el diagrama (a), el estado de datos N, que cumple con los requisitos de tiempo de configuración de registro (t SUx) y de espera (t Hx), se registra en la salida del registro X, QX, en el primer borde del reloj después del retardo de propagación del registro. El mismo borde del reloj en CLK2 hace que el estado anterior de QX, N-1, sea leído por el registro y aparezca en la salida QY después del retardo de propagación del registro.

Si hay un sesgo de tiempo entre CLK1 y CLK2, como se muestra en el diagrama (b), entonces el estado de QX puede estar en transición cuando se produce CLK2. Es posible que la entrada al registro Y no satisfaga los requisitos de tiempo de configuración o de espera del registro y, también, puede que la salida sea indeterminada y así ocasione un error.

Con el fin de garantizar un sesgo de reloj mínimo, los diseñadores emparejan las longitudes de las trazas del circuito impreso, seleccionan los búferes y otros componentes del reloj con retardos de propagación similares y equilibran la carga en las múltiples fuentes de reloj. Si bien estas técnicas ayudan, por lo general, se requiere el uso de búferes de reloj con retardo cero para adquirir un buen control sobre el sesgo de reloj.

Control del sesgo de reloj

El sesgo de reloj surge de muchas fuentes posibles. La más obvia es la de las señales de reloj que se envían a través de las interconexiones de circuitos impresos de longitudes variables. Otras fuentes de sesgo incluyen los relojes que pasan a través de diferentes dispositivos activos con diferentes retardos de propagación, los búferes de reloj con carga diferente o las diferencias de temperatura en los búferes. Si bien algunos de estos efectos pueden controlarse, los diseñadores, a menudo, utilizan dispositivos activos para volver a sincronizar los relojes con un reloj de referencia utilizando los PLL.

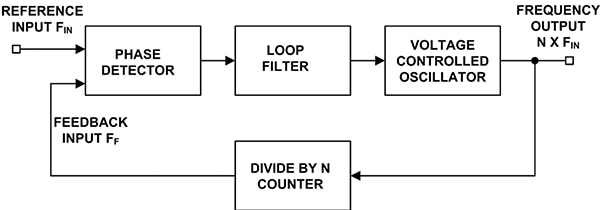

Los circuitos PLL se utilizan para el control de frecuencia y de fase. Se pueden configurar como multiplicadores de frecuencia, demoduladores, generadores de seguimiento o circuitos de recuperación de reloj. Cada una de estas aplicaciones requiere características diferentes, pero todas utilizan el mismo concepto básico de circuito que se muestra en la Figura 2.

Figura 2: Diagrama de bloques de un PLL configurado como un multiplicador de frecuencia. Es básicamente un sistema de control de realimentación que controla la fase de un oscilador controlado por tensión (VCO). (Fuente de la imagen: DigiKey).

Figura 2: Diagrama de bloques de un PLL configurado como un multiplicador de frecuencia. Es básicamente un sistema de control de realimentación que controla la fase de un oscilador controlado por tensión (VCO). (Fuente de la imagen: DigiKey).

La Figura 2 muestra un diagrama de bloques de un PLL básico configurado como un multiplicador de frecuencia. El funcionamiento de este circuito es típico de todos los PLL. Es básicamente un sistema de control de realimentación que controla la fase de un VCO. La señal de entrada se aplica a una entrada de un detector de fase. La otra entrada es una señal de realimentación de la salida de una división por el contador N. Normalmente, las frecuencias de ambas señales serán casi iguales.

La salida del detector de fase es un voltaje proporcional a la diferencia de fase entre las dos entradas. Esta señal se aplica al filtro de bucle. Es el filtro de bucle el que determina las características dinámicas del PLL. La señal filtrada controla el VCO. Tenga en cuenta que la salida del VCO está en una frecuencia que es N veces la entrada suministrada a la entrada de referencia de frecuencia (F IN). Esta señal de salida se envía de vuelta al detector de fase a través de la división por el contador N.

Normalmente, el filtro de bucle está diseñado para que coincida con las características requeridas por la aplicación del PLL. Si el PLL va a adquirir y rastrear una señal, el ancho de banda del filtro de bucle será mayor que si esperara una frecuencia de entrada fija. El rango de frecuencia que el PLL aceptará y bloqueará se denomina rango de captura. Una vez que el PLL se bloquea y rastrea una señal, el rango de frecuencias que seguirá el PLL se denomina rango de seguimiento. En general, el rango de seguimiento es mayor que el rango de captura. El filtro de bucle del PLL también determina qué tan rápido puede cambiar la frecuencia de la señal y aún así mantener el bloqueo. Esta es la velocidad de respuesta máxima. Cuanto más estrecho sea el ancho de banda del filtro de bucle, menor será el error de fase alcanzable. Esto se produce a expensas de una respuesta más lenta y un rango de captura reducido. Los PLL utilizados en las aplicaciones de reloj funcionan principalmente a frecuencias fijas.

Búferes de reloj con retardo cero

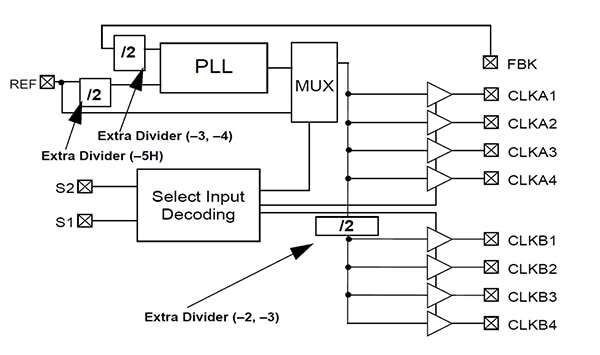

Un búfer con retardo cero es un dispositivo que puede almacenar una señal de reloj y así producir múltiples salidas de reloj desde una única entrada de reloj de referencia. Las múltiples salidas de reloj con búfer tienen poco o ningún retardo con respecto a la entrada del reloj de referencia y un sesgo bajo entre las salidas. El diagrama de bloques simplificado de un búfer con retardo cero Cypress Semiconductor CY2308SXC-3T se muestra en la Figura 3.

Figura 3: El búfer con retraso cero de ocho salidas CY2308SXC-3T utiliza un PLL para sincronizar todas las salidas con un sesgo de tiempo cercano a cero. (Fuente de la imagen: Cypress Semiconductor)

Figura 3: El búfer con retraso cero de ocho salidas CY2308SXC-3T utiliza un PLL para sincronizar todas las salidas con un sesgo de tiempo cercano a cero. (Fuente de la imagen: Cypress Semiconductor)

Un búfer con retardo cero se construye con un PLL integral que acepta una entrada de referencia (REF) y una entrada de realimentación (FBK) como las entradas a su detector de fase. La entrada de realimentación la controla una de las salidas seleccionadas por el usuario. El detector de fase interno del PLL ajusta la fase de salida del VCO para que sus dos entradas no tengan diferencia de fase ni de frecuencia. Se selecciona una de las salidas del reloj con búfer y su carga para que sean la señal de realimentación al PLL a través del detector de fase. Independientemente de los cambios de carga en esa salida, el PLL compensará de forma dinámica los cambios de carga de salida que provoquen un retardo cero desde la entrada a la salida que controla la realimentación, sin importar la carga de salida.

La familia del CY2308 tiene dos paneles de cuatro salidas, que operan en un rango de frecuencia de 10 a 133 megahercios (MHz). El sesgo de tiempo de entrada a salida es inferior a 250 picosegundos (ps) y el sesgo de reloj entre salidas es inferior a 200 ps. El sesgo de tiempo de entrada a salida puede ajustarse cambiando la capacidad de carga en la salida utilizada para la entrada de realimentación.

La familia del producto ofrece varias configuraciones de divisores de división por dos. El componente seleccionado es la variante “-3” que tiene dos de tales divisores, como se muestra en el diagrama de bloques. Esta configuración le permite al usuario obtener salidas de dos o cuatro veces la frecuencia de entrada del reloj de referencia.

El búfer con retardo cero más utilizado se configura con cinco salidas y se encuentra en varios fabricantes diferentes. El Cypress Semiconductor CY2305SXI-1HT, el IDT 2305-1DCGI8 y el ON Semiconductor NB2305AI1HDR2G son dispositivos muy similares. Todos cuentan con cinco salidas de reloj con búfer, un solo puerto CLKOUT y un panel cuádruple de salidas de reloj. A diferencia del CY2308, el punto de realimentación del PLL se establece en la única señal CLKOUT.

Dinámica del búfer con retardo cero

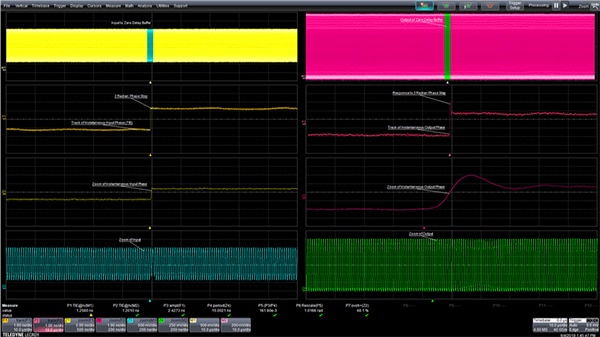

Los PLL en los búferes con retardo cero son, básicamente, sistemas de control de realimentación. El filtro de bucle del PLL controla las dinámicas. Al igual que con cualquier sistema de control, es importante evaluar la dinámica del bucle de realimentación en respuesta a una entrada transitoria. Una forma de hacer esto es aplicar una entrada con un cambio en escalón para evaluar la respuesta al escalón (Figura 4).

Figura 4: Evaluación de la respuesta al escalón del búfer con retardo cero CY2305 utilizando un escalón de fase de 1 radián a 66.67 MHz. La cuadrícula superior izquierda es la señal de entrada y la cuadrícula en la parte superior derecha es la salida. (Fuente de la imagen: DigiKey).

Figura 4: Evaluación de la respuesta al escalón del búfer con retardo cero CY2305 utilizando un escalón de fase de 1 radián a 66.67 MHz. La cuadrícula superior izquierda es la señal de entrada y la cuadrícula en la parte superior derecha es la salida. (Fuente de la imagen: DigiKey).

La señal de entrada es un seno de 66.67 MHz con un escalón de un radián en el centro de la ventana de señal adquirida. A esta forma de onda la generó un generador de forma de onda arbitrario (AWG). Tanto la entrada como la salida del búfer con retraso cero CY2305 se adquirieron utilizando un osciloscopio con una configuración de base de tiempo de 10 microsegundos (µs) por división.

La cuadrícula superior izquierda en la Figura 4 es la señal de entrada y la cuadrícula de la parte superior derecha es la salida. El error de intervalo de tiempo (TIE) es la diferencia de tiempo entre el borde del reloj medido y su posición ideal y se mide para cada forma de onda. En esencia, es la fase instantánea de la señal referida a una frecuencia de reloj fija, en este caso de 66.67 MHz. El valor del TIE para cada ciclo de reloj tanto de la entrada como de la salida se traza como una forma de onda denominada pista de TIE. La pista para la entrada es la segunda cuadrícula desde la parte superior izquierda. Aquí, el escalón en la fase es visible con una amplitud de 2.4 nanosegundos (ns). Este valor representa un cambio de fase de un radián para la frecuencia de reloj de 66.67 MHz.

La segunda traza desde la parte superior a la derecha es la pista de TIE de la salida. La pista de la salida muestra algunas sobrecrestas y se asienta en un nuevo valor promedio para coincidir con el cambio de entrada. La tercera traza de la parte superior muestra una traza de zoom expandida de forma horizontal de la entrada a la izquierda y de la salida a la derecha. Los detalles del escalón de entrada muestran una transición limpia.

El zoom de la salida exhibe algunas sobrecrestas y luego se establece de manera rápida en el nuevo valor promedio en alrededor de un ciclo de unos 500 ns de duración. Esta es una buena respuesta al escalón para un escalón de fase tan grande. Se asienta con rapidez y no hay evidencia de una respuesta oscilatoria inestable.

Las dos trazas inferiores muestran vistas expandidas de forma horizontal de la entrada (izquierda) y la salida (derecha). El gran escalón de fase es claramente visible en la entrada, pero la respuesta lenta de salida es menos visible en esta escala de tiempo.

Conclusión:

Los diseñadores de sistemas digitales de alto rendimiento deben seguir prestando una atención minuciosa al diseño de los circuitos de generación y distribución del reloj para evitar diferencias o incertidumbres en el tiempo de distribución del reloj. Dichos problemas pueden deteriorar el rendimiento del sistema, reducir los márgenes de tiempo o causar errores de funcionamiento.

Como se describe, el búfer con retardo cero es una buena herramienta para el control activo cuando se propagan múltiples señales de reloj y se mantiene la sincronización con una señal de reloj principal. Proporcionan un excelente seguimiento, incluso con cambios significativos de carga en la salida detectada. Sin embargo, como se muestra, los diseñadores deben evaluar de forma cuidadosa la dinámica del bucle de realimentación de un búfer con retardo cero para garantizar que cumpla con los requisitos de la aplicación.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.