Acelere el diseño de sistemas de reconocimiento de visión con las MPU de la serie RZ/V2 de Renesas

Colaboración de Editores de DigiKey de América del Norte

2022-09-29

Dado que el reconocimiento de la visión en el borde se está convirtiendo en una característica cada vez más crítica en muchos productos, el aprendizaje automático (ML) y la inteligencia artificial (AI) están encontrando su camino en una amplia gama de espacios de aplicación. El problema al que se enfrentan los desarrolladores es que la visión con ML/AI puede requerir más potencia de cálculo para ejecutar los algoritmos de reconocimiento de la que puede estar disponible en aplicaciones con limitaciones de potencia. También añade costos si se requieren costosas soluciones de gestión térmica.

El objetivo de ML/AI en el borde es encontrar el enfoque arquitectónico óptimo que equilibre el rendimiento y la potencia, al tiempo que proporciona un ecosistema de software resistente dentro del cual desarrollar la aplicación.

Teniendo en cuenta estas condiciones, este artículo presenta una solución en forma de unidad de microprocesador (MPU) de la serie RZ/V2 de Renesas Electronics con su acelerador de hardware de IA incorporado. El artículo explora cómo una MPU, en lugar de un microcontrolador (MCU) o una unidad de procesamiento gráfico (GPU) de alta gama, puede resolver varios problemas a los que se enfrentan los diseñadores. Se incluye una descripción de cómo pueden empezar a diseñar sistemas de reconocimiento de visión utilizando la serie RZ/V2, junto con algunos "Consejos y trucos" para facilitar el proceso.

Introducción a las MPU de la serie RZ/V2

La serie RZ/V2 es una solución que desbloquea muchas capacidades para los desarrolladores que utilizan un microprocesador de tres núcleos. Los microprocesadores de la serie RZ/V2L contienen dos procesadores Arm Cortex-A55 que funcionan a 1.2 gigahercios (GHz) y un núcleo de microcontrolador en tiempo real (Arm® Cortex®-M33) que funciona a 200 megahercios (MHz). Además, las piezas de la serie contienen una GPU basada en un procesador multimedia Arm Mali-G31 con instrucciones NEON de instrucción simple/datos múltiples (SIMD). La combinación de estos tres núcleos de procesamiento y el procesador multimedia proporciona una solución completa para los desarrolladores que trabajan en sistemas de reconocimiento de visión.

Actualmente hay dos clases de MPU en la serie RZ/V2, la RZ/V2L y la RZ/V2M. El RZ/V2L cuenta con un sencillo procesador de señal de imagen (ISP), un motor gráfico 3D y un conjunto de periféricos muy versátil. La RZ/V2M, por su parte, añade un ISP de alto rendimiento que admite la resolución 4K a 30 fotogramas por segundo (fps). Este artículo se centra en la familia RZ/V2L, formada por el R9A07G054L23GBG y el R9A07G054L24GBG. La principal diferencia entre las dos piezas es que el R9A07G054L23GBG se presenta en un encapsulado 456-LFBGA de 15 mm2, mientras que el R9A07G054L24GBG se presenta en un encapsulado 551-LFBGA de 21 mm2.

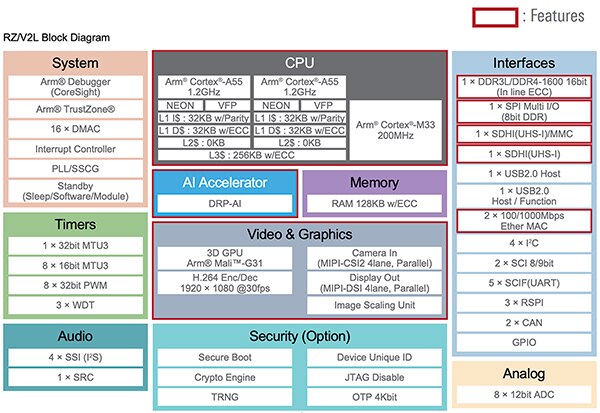

El diagrama de bloques de la serie RZ/V2L se muestra en la figura 1. Además de los tres núcleos de procesamiento, las MPU incluyen interfaces para periféricos estándar como memoria DDR3/DDR4, SPI, USB, Ethernet, I²C, CAN, SCI, GPIO y un convertidor analógico-digital (ADC). Además, las piezas incluyen funciones de seguridad como un arranque seguro, un motor criptográfico y un generador de números aleatorios reales (TRNG). Sin embargo, lo que diferencia a la serie MPU es el acelerador de IA del procesador reconfigurable dinámicamente (DRP).

Figura 1: La MPU de la serie RZ/V2L admite varias interfaces periféricas, seguridad y opciones de procesamiento de video. La característica fundamental para las aplicaciones de reconocimiento de visión es el acelerador DRP-AI. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 1: La MPU de la serie RZ/V2L admite varias interfaces periféricas, seguridad y opciones de procesamiento de video. La característica fundamental para las aplicaciones de reconocimiento de visión es el acelerador DRP-AI. (Fuente de la imagen: Renesas Electronics Corporation)

La salsa secreta del acelerador DRP-AI

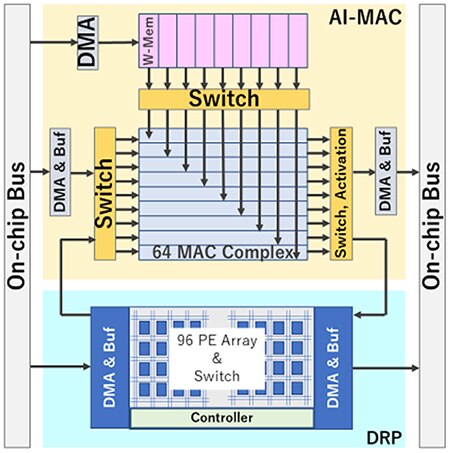

El acelerador DRP-AI es la salsa secreta que permite a las MPU de la serie RZ/V2L ejecutar aplicaciones de reconocimiento de visión con rapidez, menor consumo de energía y un perfil térmico más bajo. El DRP-AI consta de dos componentes: un DRP y un AI-multiplicar-y-acumular (MAC), que puede procesar eficazmente las operaciones en las redes convolucionales y las capas de combinación total optimizando el flujo de datos con conmutadores internos (Figura 2).

El hardware de DRP-AI está dedicado a la ejecución de inferencia de IA. El DRP-AI utiliza una tecnología única de reconfiguración dinámica desarrollada por Renesas que proporciona flexibilidad, procesamiento de alta velocidad y eficiencia energética. Además, el traductor DRP-AI, una herramienta de software gratuita, permite a los usuarios implementar modelos de IA optimizados que maximizan rápidamente el rendimiento. Se pueden colocar en la memoria externa múltiples ejecutables emitidos por el traductor DRP-AI. La aplicación puede entonces cambiar dinámicamente entre múltiples modelos de IA durante el tiempo de ejecución.

El DRP puede procesar rápidamente actividades complejas, como el preprocesamiento de imágenes y las capas de agrupación de modelos de IA, cambiando dinámicamente la configuración del hardware.

Figura 2: El DRP-AI se compone de un DRP y un AI-MAC, que juntos pueden procesar eficientemente operaciones en redes convolucionales y capas de combinación total optimizando el flujo de datos con conmutadores internos. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 2: El DRP-AI se compone de un DRP y un AI-MAC, que juntos pueden procesar eficientemente operaciones en redes convolucionales y capas de combinación total optimizando el flujo de datos con conmutadores internos. (Fuente de la imagen: Renesas Electronics Corporation)

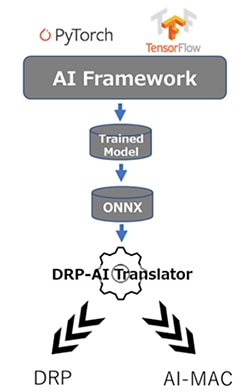

El traductor DRP-AI

La herramienta DRP-AI Translator genera ejecutables optimizados para DRP-AI a partir de modelos ONNX entrenados, independientemente de cualquier marco de trabajo de IA. Por ejemplo, un desarrollador podría utilizar PyTorch, TensorFlow o cualquier otro marco de modelado de IA si produce un modelo ONNX. Una vez entrenado el modelo, se introduce en el traductor DRP-AI, que genera los ejecutables DRP y AI-MAC (Figura 3).

Figura 3: Los modelos de IA se entrenan utilizando cualquier marco compatible con ONNX. El modelo ONNX se introduce en el traductor DRP-AI, que genera los ejecutables DRP y AI-MAC. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 3: Los modelos de IA se entrenan utilizando cualquier marco compatible con ONNX. El modelo ONNX se introduce en el traductor DRP-AI, que genera los ejecutables DRP y AI-MAC. (Fuente de la imagen: Renesas Electronics Corporation)

El traductor DRP-AI tiene tres objetivos principales:

- Programación de cada operación para procesar el modelo de IA.

- Ocultación de la sobrecarga, como el tiempo de acceso a la memoria que se produce durante la transición de cada operación en el programa.

- Optimización de la estructura del grafo de la red.

El traductor asigna automáticamente cada proceso del modelo de IA al AI-MAC y al DRP, lo que permite al usuario utilizar fácilmente el DRP-AI sin ser un experto en hardware. En su lugar, el desarrollador puede realizar llamadas a través del controlador suministrado para ejecutar el modelo de IA de alto rendimiento. Además, el traductor DRP-AI puede actualizarse continuamente para admitir nuevos modelos de IA sin necesidad de realizar cambios en el hardware.

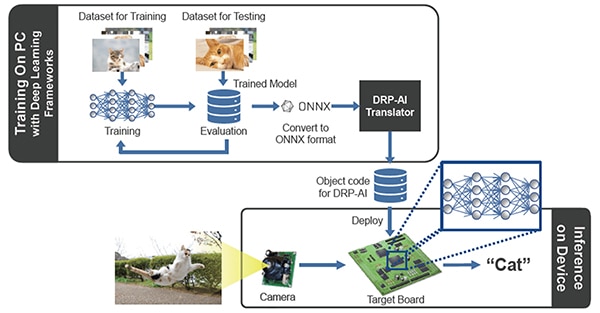

Casos y procesos de uso del sistema

En la Figura 4 se muestra el flujo general del proceso para utilizar las MPU RZ/V2L para entrenar e implementar aplicaciones de reconocimiento de visión. Como es habitual, los ingenieros pueden adquirir su conjunto de datos y utilizarlo para entrenar su modelo de reconocimiento de visión. Tanto si se trata de identificar gatos, un producto en un carro de la compra o piezas que fallan en una cadena de montaje, el proceso de entrenamiento se realizará utilizando marcos de trabajo de IA conocidos. Una vez entrenado el modelo, se convierte en formato ONNX y se introduce en el traductor DRP-AI, que a su vez genera un código objeto que puede ejecutarse en el hardware DRP-AI. Los datos de las cámaras, acelerómetros u otros sensores se muestrean y se introducen en los ejecutables, proporcionando el resultado de la ejecución de la inferencia.

Figura 4: Proceso de entrenamiento y ejecución de un algoritmo de reconocimiento de visión en las MPU RZ/V2L. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 4: Proceso de entrenamiento y ejecución de un algoritmo de reconocimiento de visión en las MPU RZ/V2L. (Fuente de la imagen: Renesas Electronics Corporation)

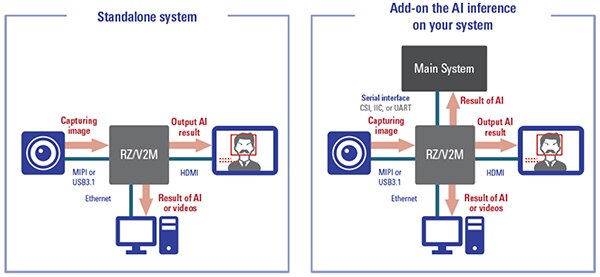

Los ingenieros pueden aprovechar las MPU RZ/V2L de varias maneras en sus diseños (Figura 5). En primer lugar, la MPU RZ/V2L puede utilizarse en diseños independientes en los que el RZ/V2L es el único procesador del sistema. Con sus tres núcleos y el hardware de aceleración de la IA, es posible que no se necesite potencia de cálculo adicional.

El segundo caso de uso es cuando el RZ/V2L se utiliza como procesador de IA en un sistema más amplio. En este caso de uso, el RZ/V2L ejecuta las inferencias de la IA y devuelve un resultado a otro procesador o sistema que luego actúa sobre ese resultado. El caso de uso seleccionado dependerá de varios factores como el coste, la arquitectura global del sistema, el rendimiento y los requisitos de respuesta en tiempo real.

Figura 5: Los dos casos de uso de las MPU RZ/V2L son utilizarlas de forma autónoma en una aplicación, o como procesador de IA utilizado en un sistema más amplio. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 5: Los dos casos de uso de las MPU RZ/V2L son utilizarlas de forma autónoma en una aplicación, o como procesador de IA utilizado en un sistema más amplio. (Fuente de la imagen: Renesas Electronics Corporation)

Ejemplo de aplicación en el mundo real

Hay muchos casos de uso en los que se puede desplegar la tecnología de reconocimiento de visión. Un ejemplo interesante es el del supermercado. Hoy en día, al pasar por caja en una tienda de comestibles, un empleado o un comprador suele escanear todos los artículos del carrito. Un caso de uso interesante sería detectar los productos que pasan por la cinta transportadora mediante el reconocimiento de la visión y cobrarlos automáticamente.

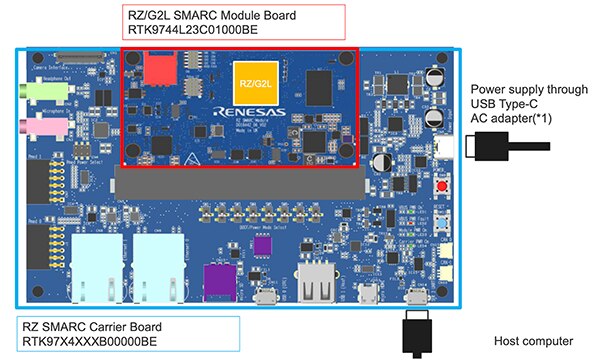

Se puede construir un prototipo utilizando una simple cámara CMOS y la placa de evaluación RTK9754L23S01000BE de Renesas (Figura 6). La placa de desarrollo embebido RZ/V2L cuenta con un sistema en módulo (SOM) y una placa portadora que permite a los desarrolladores ponerse en marcha rápidamente. Además, la placa de desarrollo es compatible con Linux, junto con varias herramientas como el traductor DRP-AI.

Figura 6: La placa de desarrollo embebido RZ/V2L cuenta con un SOM y una placa portadora que permite a los desarrolladores ponerse en marcha rápidamente. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 6: La placa de desarrollo embebido RZ/V2L cuenta con un SOM y una placa portadora que permite a los desarrolladores ponerse en marcha rápidamente. (Fuente de la imagen: Renesas Electronics Corporation)

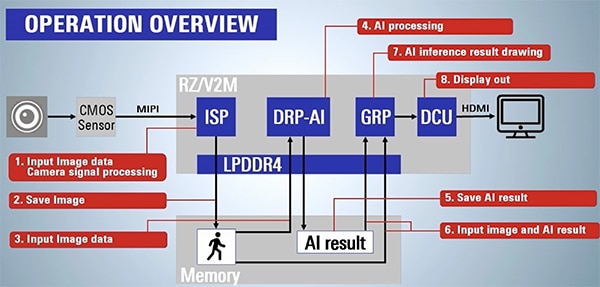

En la figura 7 se puede ver un resumen operativo de lo que se necesita para adquirir datos de imágenes y producir un resultado de IA. En este ejemplo de aplicación, se toman imágenes de la cinta transportadora utilizando un sensor CMOS a través del ISP integrado. A continuación, la imagen se guarda en la memoria y se introduce en el motor DRP-AI. Por último, el motor DRP-AI ejecuta la inferencia y proporciona un resultado de IA. Por ejemplo, el resultado puede ser que se encuentre un plátano, o una manzana, o alguna otra fruta.

El resultado suele ir acompañado de un nivel de confianza de 0 a 1. Por ejemplo, 0.90 de confianza significa que la IA está segura de haber detectado una manzana. Por otro lado, una confianza de 0.52 podría significar que la IA cree que es una manzana pero no está segura. No es raro tomar un resultado de la IA y promediarlo en varias muestras para mejorar las posibilidades de obtener resultados correctos.

Figura 7: La placa de desarrollo integrada RZ/V2L se utiliza para ejecutar una inferencia de IA que reconoce varias frutas en una cinta transportadora. La figura muestra los pasos necesarios para adquirir una imagen y producir un resultado de IA. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 7: La placa de desarrollo integrada RZ/V2L se utiliza para ejecutar una inferencia de IA que reconoce varias frutas en una cinta transportadora. La figura muestra los pasos necesarios para adquirir una imagen y producir un resultado de IA. (Fuente de la imagen: Renesas Electronics Corporation)

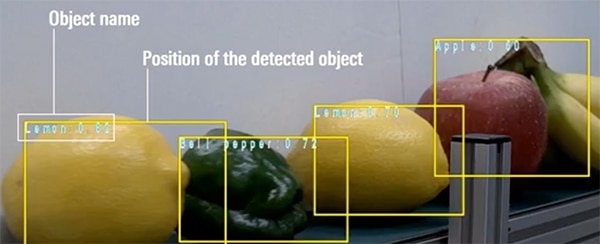

Por último, en este ejemplo, se dibuja un recuadro alrededor del objeto detectado y se muestra el nombre del objeto reconocido junto con el nivel de confianza (Figura 8).

Figura 8: Ejemplo de salida del RZ/V2L en una aplicación que detecta frutas y verduras en una cinta transportadora. (Fuente de la imagen: Renesas Electronics Corporation)

Figura 8: Ejemplo de salida del RZ/V2L en una aplicación que detecta frutas y verduras en una cinta transportadora. (Fuente de la imagen: Renesas Electronics Corporation)

Consejos y trucos para empezar a utilizar el RZ/V2L

Los desarrolladores que deseen iniciarse en el aprendizaje automático con las MPU RZ/V2L de Renesas descubrirán que tienen muchos recursos que aprovechar para ponerse en marcha. A continuación se presentan varios "consejos y trucos" que los desarrolladores deben tener en cuenta y que pueden simplificar y acelerar su desarrollo:

- Comienza con una placa de desarrollo y los ejemplos existentes para tener una idea de cómo desplegar y ejecutar una aplicación.

- Si es necesario ejecutar varias inferencias, guarde los modelos ejecutables en la memoria externa y utilice las capacidades de DRP-AI para cambiar rápidamente de modelo.

- Revise la documentación y los vídeos que se encuentran en el sitio de las MPU de IA embebidas RZ/V de Renesas.

- Descargue el traductor DRP-AI.

- Descargue el paquete de soporte de RZ/V2L DRP-AI.

Los desarrolladores que sigan estos "consejos y trucos" se ahorrarán bastante tiempo y disgustos al empezar.

Conclusión:

El ML y la IA están encontrando su camino en muchas aplicaciones de borde, con la capacidad de reconocer objetos en tiempo real cada vez más importante. Para los diseñadores, la dificultad estriba en encontrar la arquitectura adecuada con la que realizar la IA/ML en el borde. Las GPU tienden a consumir mucha energía, mientras que las MCU pueden no tener suficiente potencia de cálculo.

Como se ha mostrado, la serie de MPU Renesas RZ/V con DRP-AI tiene varias ventajas, como la IA acelerada por hardware, junto con una importante cadena de herramientas y soporte para la creación de prototipos.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.