Acelere las aplicaciones de inteligencia artificial en el kit de evaluación VCK190 de Xilinx con los núcleos IP de Design Gateway

2022-11-18

Los dispositivos de la serie Versal AI Core de Xilinx están diseñados para resolver el problema único y más difícil de la inferencia de la IA mediante el uso de un motor de cómputo de IA de clase ASIC de alta eficiencia de cálculo junto con un tejido programable flexible para construir una aplicación de IA con aceleradores que maximizan la eficiencia para cualquier carga de trabajo dada al mismo tiempo que ofrecen baja potencia y baja latencia.

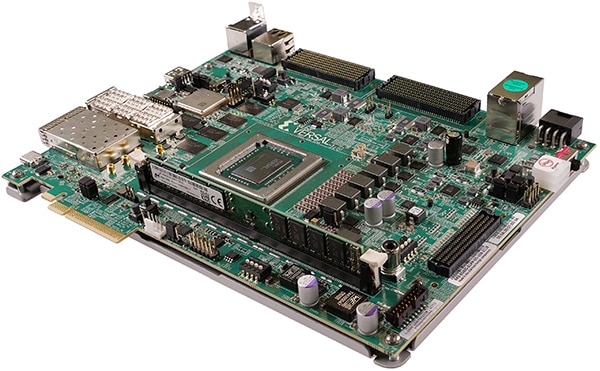

El kit de evaluación VCK190 de la serie Versal AI Core cuenta con el dispositivo VC1902, que tiene el mejor rendimiento de IA de la cartera. El kit está hecho para diseños que requieren un alto rendimiento de inferencia de IA y de procesamiento de señales. Al ofrecer una potencia de cálculo 100 veces superior a la de las actuales CPU de clase servidor y contar con varias opciones de conectividad, el kit VCK190 es una plataforma de evaluación y creación de prototipos ideal para una amplia gama de aplicaciones, desde la nube hasta el borde.

Figura 1: Kit de evaluación VCK190 serie Xilinx Versal AI Core. (Fuente de la imagen: AMD, Inc)

Figura 1: Kit de evaluación VCK190 serie Xilinx Versal AI Core. (Fuente de la imagen: AMD, Inc)

Características principales del kit de evaluación VCK190

- Dispositivo de la serie Versal AI Core integrado

- Equipado con silicio de producción Versal ACAP XCVC1902

- Motores de IA y DSP que proporcionan un rendimiento de cálculo 100 veces superior al de las actuales CPU de clase de servidor

- Diseños de referencia de socios preconstruidos para la creación rápida de prototipos

- La última tecnología de conectividad para el desarrollo de aplicaciones de vanguardia

- IP de disco duro PCIe® Gen4 integrada para una interfaz de dispositivo de alto rendimiento, como las unidades de estado sólido (SSD) NVMe y los procesadores de host.

- IP Hard EMAC 100G integrada para interfaces de red 100G de alta velocidad

- Interfaces de memoria DDR4 y LPDDR4

- Herramientas cooptimizadas y método de depuración

- Vivado® ML, plataforma de software unificada Vitis™, Vitis AI, herramientas del motor de IA para el desarrollo de aplicaciones de inferencia de IA

Acelerador de interfaz de IA con los dispositivos de la serie Versal AI Core de Xilinx

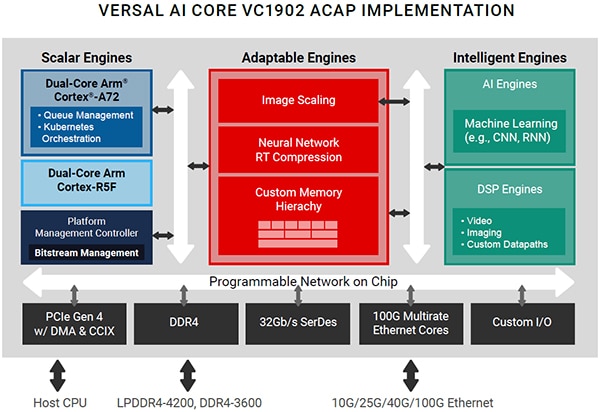

Figura 2: Diagrama de bloques del dispositivo Versal AI Core VC1902 ACAP de Xilinx. (Fuente de la imagen: AMD, Inc)

Figura 2: Diagrama de bloques del dispositivo Versal AI Core VC1902 ACAP de Xilinx. (Fuente de la imagen: AMD, Inc)

La plataforma de aceleración de computación adaptativa Versal® AI Core (ACAP) es un dispositivo heterogéneo, multinúcleo y altamente integrado que puede adaptarse dinámicamente a nivel de hardware y software para una amplia gama de cargas de trabajo de IA, por lo que es ideal para aplicaciones de computación de borde de IA o tarjetas aceleradoras de nube. La plataforma integra motores escalares de última generación para la computación integrada, motores adaptables para la flexibilidad del hardware y motores inteligentes formados por motores DSP y revolucionarios motores de IA para la inferencia y el procesamiento de señales. El resultado es un acelerador adaptable que supera el rendimiento, la latencia y la eficiencia energética de las FPGA y GPU tradicionales para las cargas de trabajo de IA/ML.

Lo más destacado de la plataforma ACAP de Versal

- Motores adaptables:

- La jerarquía de memoria personalizada optimiza el movimiento y la gestión de datos para los núcleos del acelerador.

- Funciones de pre y postprocesamiento, incluida la compresión de RT en red neural y el escalado de imágenes

- Motores de IA (DPU)

- Matriz de procesadores vectoriales en mosaico, hasta 133 INT8 TOPS de rendimiento con dispositivos XCVC1902, llamados, Unidad de Procesamiento de Aprendizaje Profundo o DPU

- Ideal para redes neuronales que van desde CNN, RNN y MLP; hardware adaptable para optimizar la evolución de los algoritmos

- Motores Scalar

- Subsistema de procesamiento ARM de cuatro núcleos, controlador de gestión de la plataforma para la seguridad, la energía y la gestión del flujo de bits

Rendimiento de la inferencia de IA VCK190

La VCK190 es capaz de ofrecer un rendimiento de cálculo 100 veces superior al de las actuales CPU de clase de servidor. A continuación, se muestra un ejemplo de rendimiento basado en la implementación del motor de IA por el núcleo DPU C32B6 con un lote = 6. Consulte la siguiente tabla para conocer la tasa de producción (en fotogramas/segundo o fps) de varias muestras de redes neuronales en VCK190 con la DPU funcionando a 1250 MHz.

|

Tabla 1: Ejemplo de rendimiento de la inferencia de IA VCK190.

Vea más detalles sobre el rendimiento de VCK190 AI en la Guía del usuario de la biblioteca Vitis AI (UG1354), r2.5.0 en https://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board

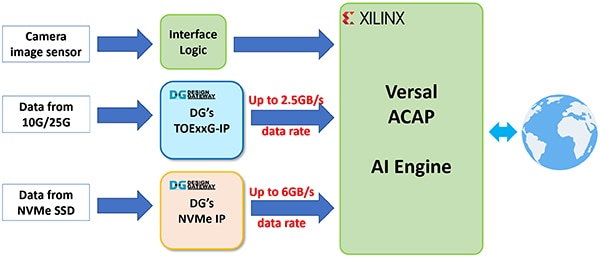

¿Cómo los núcleos IP de Design Gateway aceleran el rendimiento de las aplicaciones de IA?

Los núcleos IP de Design Gateway están diseñados para gestionar el protocolo de Red y Almacenamiento de datos sin necesidad de que intervenga la CPU. Esto lo hace ideal para descargar completamente a los sistemas de CPU del complicado procesamiento de protocolos y lo que les permite utilizar la mayor parte de su potencia de cálculo para aplicaciones de IA, incluyendo la inferencia de IA, el procesamiento de datos previo y posterior, la interfaz de usuario, la comunicación de red y el acceso al almacenamiento de datos para obtener el mejor rendimiento posible.

Figura 3: Diagrama de bloques de un ejemplo de aplicación de IA con los núcleos IP de Design Gateway. (Fuente de la imagen: Design Gateway)

Figura 3: Diagrama de bloques de un ejemplo de aplicación de IA con los núcleos IP de Design Gateway. (Fuente de la imagen: Design Gateway)

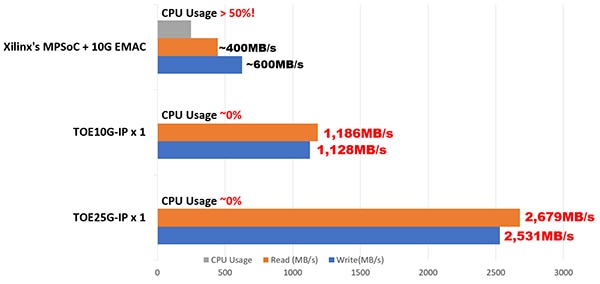

Rendimiento del motor de descarga TCP IP (TOExxG-IP) de Design Gateway

El procesamiento de flujos de datos TCP de alta velocidad y alto rendimiento a través de 10GbE o 25GbE por parte de los sistemas de CPU tradicionales necesita más del 50% del tiempo de la CPU, lo que reduce el rendimiento general de las aplicaciones de IA. Según la prueba de rendimiento de TCP 10G en los sistemas MPSoC Linux de Xilinx, el uso de la CPU durante la transmisión de TCP 10GbE es superior al 50%, la velocidad de transferencia de datos de envío y recepción de TCP podría alcanzarse sólo alrededor del 40% al 60% de la velocidad de 10GbE o 400 MB/s a 600 MB/s.

Al implementar el núcleo TOExxG-IP de Design Gateway, el uso de la CPU para la transmisión TCP a través de 10 GbE y 25 GbE puede reducirse casi al 0%, mientras que la utilización del ancho de banda ethernet puede lograrse cerca del 100%. Esto permite enviar y recibir datos a través de la red TCP directamente por pura lógica de hardware y alimentar el motor de IA Versal con un uso mínimo de la CPU y la menor latencia posible. La figura 4 muestra la comparación del uso de la CPU y la velocidad de transmisión TCP entre los sistemas TOExxG-IP y MPSoC Linux.

Figura 4: Comparación del rendimiento de la transmisión TCP 10G/25G por parte de los sistemas MPSoC Linux y el núcleo TOExxG-IP de Design Gateway. (Fuente de la imagen: Design Gateway)

Figura 4: Comparación del rendimiento de la transmisión TCP 10G/25G por parte de los sistemas MPSoC Linux y el núcleo TOExxG-IP de Design Gateway. (Fuente de la imagen: Design Gateway)

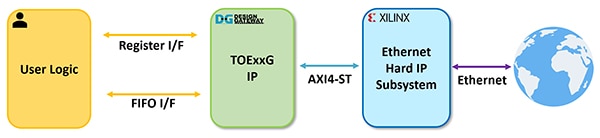

TOExxG-IP de Design Gateway para dispositivos Versal

Figura 5: Vista general de los sistemas TOExxG-IP. (Fuente de la imagen: Design Gateway)

Figura 5: Vista general de los sistemas TOExxG-IP. (Fuente de la imagen: Design Gateway)

El núcleo TOExxG-IP implementa la pila TCP/IP (en lógica hardwire) y se conecta con el módulo EMAC Hard IP y Ethernet Subsystem de Xilinx para la interfaz de hardware de capa inferior con velocidad 10G/25G/100G Ethernet. La interfaz de usuario del TOExxG-IP consta de una interfaz de registro para las señales de control y una interfaz FIFO para las señales de datos. El TOExxG-IP está diseñado para conectarse con el subsistema Ethernet de Xilinx a través de la interfaz AXI4-ST. La frecuencia de reloj de la interfaz de usuario depende de la velocidad de la interfaz Ethernet (por ejemplo, 156.625 MHz o 322.266 MHz).

Características de TOExxG-IP

- Implementación completa de la pila TCP/IP sin necesidad de la CPU

- Admite una sesión con un TOExxG-IP

- La multisesión puede implementarse utilizando múltiples instancias de TOExxG-IP

- Soporte para el modo Servidor y Cliente (apertura y cierre pasivo/activo)

- Soporte para el marco Jumbo

- Interfaz de datos sencilla mediante una interfaz FIFO estándar

- Interfaz de control sencilla mediante una interfaz RAM de un solo puerto

Los usos de los recursos de la FPGA en el dispositivo FPGA XCVC1902-VSVA2197-2MP-ES se muestran en la Tabla 2 siguiente.

|

Tabla 2: Ejemplo de estadísticas de aplicación del dispositivo Versal.

En su hoja de datos se describen más detalles del TOExxG-IP, que puede descargarse del sitio web de Design Gateway en los siguientes enlaces:

- Hoja de datos de TOE10G-IP Core Xilinx

- Hoja de datos de TOE25G-IP Core Xilinx

- Hoja de datos de TOE100G-IP Core Xilinx

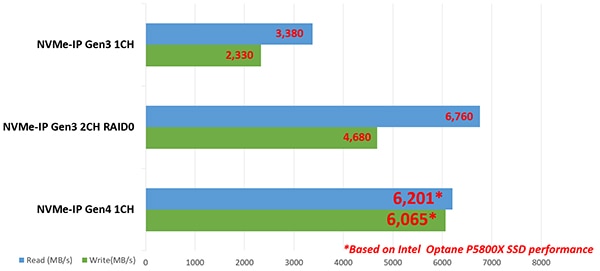

Rendimiento de la IP del controlador de host NVMe de Design Gateway

La velocidad de la interfaz de Almacenamiento NVMe con PCIe Gen3 x4 o PCIe Gen4 x4 tiene velocidades de datos de hasta 32 Gbps y 64 Gbps. Esta velocidad es entre tres y seis veces superior a la de 10GbE Ethernet. El procesamiento del complicado protocolo de almacenamiento NVMe por parte de la CPU para lograr la mayor velocidad de acceso al disco posible requiere más tiempo de CPU que el protocolo TCP a través de 10GbE.

Design Gateway resolvió este problema desarrollando el núcleo IP NVMe que es capaz de funcionar como un controlador de host NVMe independiente, capaz de comunicarse con una unidad de estado sólido (SSD) NVMe directamente sin la CPU. Esto permite una alta eficiencia y rendimiento del acceso a las unidades de estado sólido (SSD) NVMe PCIe Gen3 y Gen4, lo que simplifica la interfaz de usuario y las características estándar para facilitar su uso sin necesidad de conocer el protocolo NVMe. El rendimiento de las unidades de estado sólido (SSD) NVMe PCIe Gen4 puede alcanzar una velocidad de transferencia de hasta 6 GB/s con NVMe IP, como se muestra en la figura 6.

Figura 6: Comparación del rendimiento de las unidades de estado sólido (SSD) NVMe Gen3 y Gen4 con el núcleo NVMe-IP de Design Gateway. (Fuente de la imagen: Design Gateway)

Figura 6: Comparación del rendimiento de las unidades de estado sólido (SSD) NVMe Gen3 y Gen4 con el núcleo NVMe-IP de Design Gateway. (Fuente de la imagen: Design Gateway)

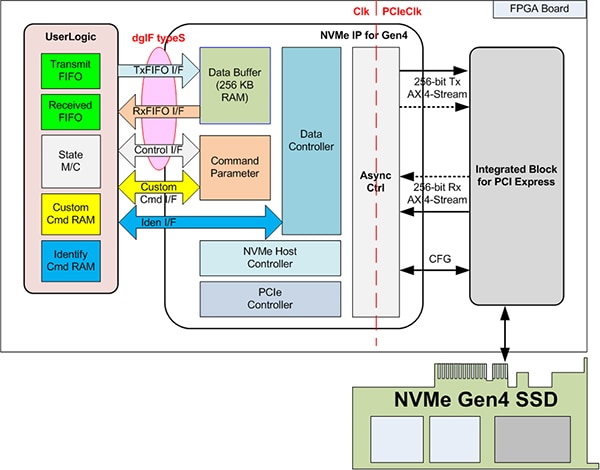

NVMe-IP de Design Gateway para dispositivos Versal

Figura 7: Visión general de los sistemas NVMe-IP. (Fuente de la imagen: Design Gateway)

Figura 7: Visión general de los sistemas NVMe-IP. (Fuente de la imagen: Design Gateway)

Características de NVMe-IP

- Capaz de implementar la capa de aplicación, la capa de transacción, la capa de enlace de datos y algunas partes de la capa física para acceder a la unidad SSD NVMe sin una CPU o una memoria DDR externa

- Funciona con Xilinx PCIe Gen3 y Gen4 Hard IP

- Posibilidad de utilizar BRAM y URAM como búferes de datos sin necesidad de una interfaz de memoria externa

- Soporta seis comandos: Identificar, Apagar, Escribir, Leer, SMART y Purgar (soporte opcional de comandos adicionales disponible)

Los usos de los recursos FPGA en el dispositivo FPGA XCVC1902-VSVA2197-2MP-E-S se muestran en la Tabla 2.

|

Tabla 3: Ejemplo de estadísticas de aplicación del dispositivo Versal.

En la hoja de datos del dispositivo NVMe-IP para Versal se describen más detalles, que pueden descargarse del sitio web de Design Gateway en el siguiente enlace:

Hoja de datos del núcleo IP NVMe para Xilinx Gen4

Conclusión:

Tanto el núcleo TOExxG-IP como el NVMe-IP podrían ayudar a acelerar el rendimiento de las aplicaciones de IA descargando por completo los sistemas de la CPU de los protocolos intensivos de computación y memoria, como TCP y el protocolo de Almacenamiento NVMe, que son fundamentales para las aplicaciones de IA en tiempo real. Esto permite al dispositivo de la serie Versal AI Core de Xilinx realizar inferencia de IA y aplicaciones informáticas de alto rendimiento sin cuellos de botella ni retrasos por el procesamiento de protocolos de red y almacenamiento de datos.

El kit de evaluación VCK190 y la solución IP de red y almacenamiento de Design Gateway permiten obtener el mejor rendimiento posible en aplicaciones de IA con el menor uso posible de recursos de la FPGA y una eficiencia energética muy alta en el dispositivo Versal AI Core de Xilinx.

Descargo de responsabilidad: Las opiniones, creencias y puntos de vista expresados por los autores o participantes del foro de este sitio web no reflejan necesariamente las opiniones, las creencias y los puntos de vista de DigiKey o de las políticas oficiales de DigiKey.